代码:

module yanxu11(in,out);

input wire[3:0] in;

output reg[3:0] out;

always @(in)

begin

out[0]=~in[0];

out[1]=~in[1];

out[2]=~in[2];

out[3]=~in[3];

end

endmodule

`timescale 1ns/1ns

module test();

reg[3:0] in;

wire[3:0] out;

yanxu11 U(in,out);

initial

begin

#10 in[3:0]=4'b0101;

#10 in[3:0]=4'b0000;

#10 in[3:0]=4'b1010;

#10 in[3:0]=4'b1111;

#60 $stop;

end

endmodule

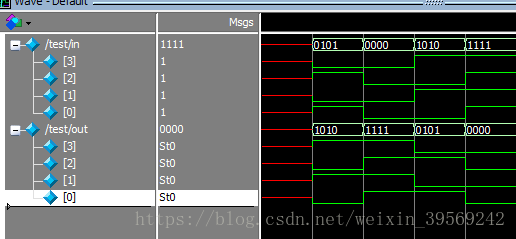

仿真图: