- 设计m序列发生器,其特征方程为,输出数字序列信号m_sequence码速率为10Mbps;设计串行转并行电路,每4位m序列并行输出,先输入的串行数据位于并行输出数据的高位。设计测试程序,进行功能仿真,将Verilog代码和仿真波形图整理入实验报告。

代码:

功能代码:

module shiyan51(reset,clock,clock_1,A_reg,m_sequence,m_seq_paral_out);

input clock;

input reset;

output A_reg;

output m_sequence;

output m_seq_paral_out;

output clock_1;

wire clock;

reg clock_1;

wire reset;

reg [3:0] A_reg;

reg m_sequence;

reg [3:0] m_seq_paral_out;

reg [1:0] cnt_2;

//clock四分频

always @(posedge clock or posedge reset)

begin

if(reset)

begin

cnt_2<=0;

clock_1<=0;

end

else

begin if(cnt_2==2'd1)

begin

cnt_2<=0;

clock_1<=~clock_1;

end

else

cnt_2<=cnt_2+1;

end

end

//m序列产生

always @(posedge clock or posedge reset)

begin

if(reset)

begin

A_reg<=4'b0001;

m_sequence<=1'b0;

end

else

begin

A_reg[0]<=A_reg[2]^A_reg[3];

A_reg[3:1]<=A_reg[2:0];

m_sequence<=A_reg[3];

end

end

//串并转换电路

reg[3:0] xx;

reg en;

always @(posedge clock or posedge reset)

begin

if(reset)

begin

xx<=4'b0000;

end

else

begin

xx<={xx[2:0],m_sequence};//连接字符串,xx的后三位作为高位,m_sequence作为低位

end

end

always @(posedge clock_1)

begin

m_seq_paral_out<=xx; //4个clock_1之后,输出并行

end

endmodule

测试代码:

`timescale 1 ns/ 1 ps

module test();

reg clock;

reg reset;

wire clock_1;

wire [3:0] A_reg;

wire m_sequence;

wire [3:0] m_seq_paral_out;

shiyan51 U1(reset,clock,clock_1,A_reg,m_sequence,m_seq_paral_out);

always #50 clock=~clock;

initial

begin

reset=1;clock=0;

#(100);

reset=0;

end

endmodule

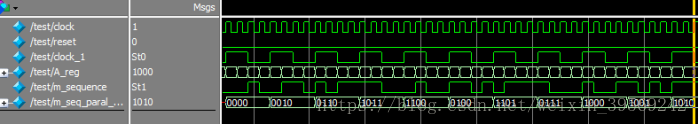

结果:

- 用函数描述一个4选1多路选择器。设计测试程序,进行功能仿真,将Verilog代码和仿真波形图整理入实验报告。

代码:

功能代码:

module shiyan52(din,dout);

input din;

output dout;

wire [1:0] din;

wire [1:0] dout;

function [1:0] code;

input [1:0] din;

casex (din)

2'b00: code=2'h0;

2'b01: code=2'h1;

2'b10: code=2'h2;

2'b11: code=2'h3;

default :code=2'hx;

endcase

endfunction

assign dout=code(din);

endmodule

测试代码:

`timescale 1 ns/ 1 ps

module test();

reg [1:0]din;

wire [1:0]dout;

shiyan52 U1(din,dout);

initial

begin din=2'b00;

#10 din=2'b01;

#10 din=2'b10;

#10 din=2'b11;

#10 din=2'b01;

#10 din=2'b10;

#10 din=2'b11;

#10 $stop;

end

endmodule

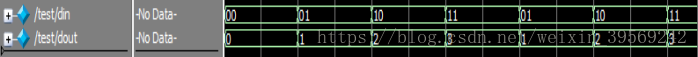

结果: