创建clk的ip核以及设置PLL的时钟输出

原理:外部晶振输入50M的频率,由ip核输出想要的频率

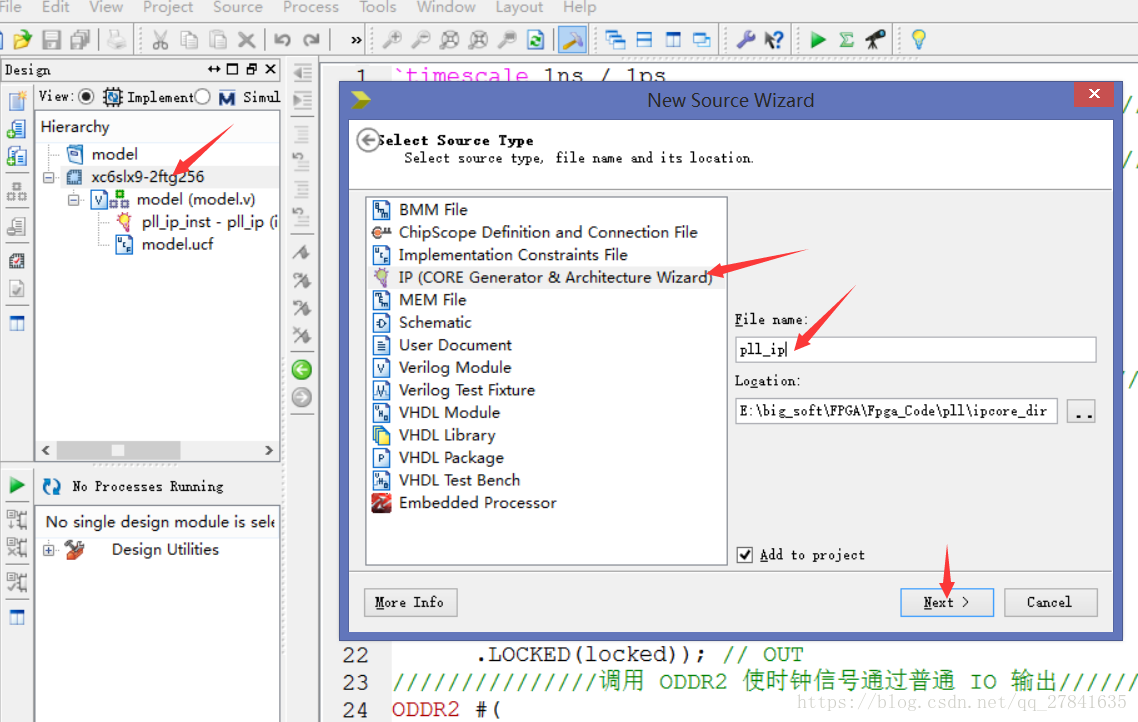

1、新建工程model再在“芯片”名称上建立clk的ip核

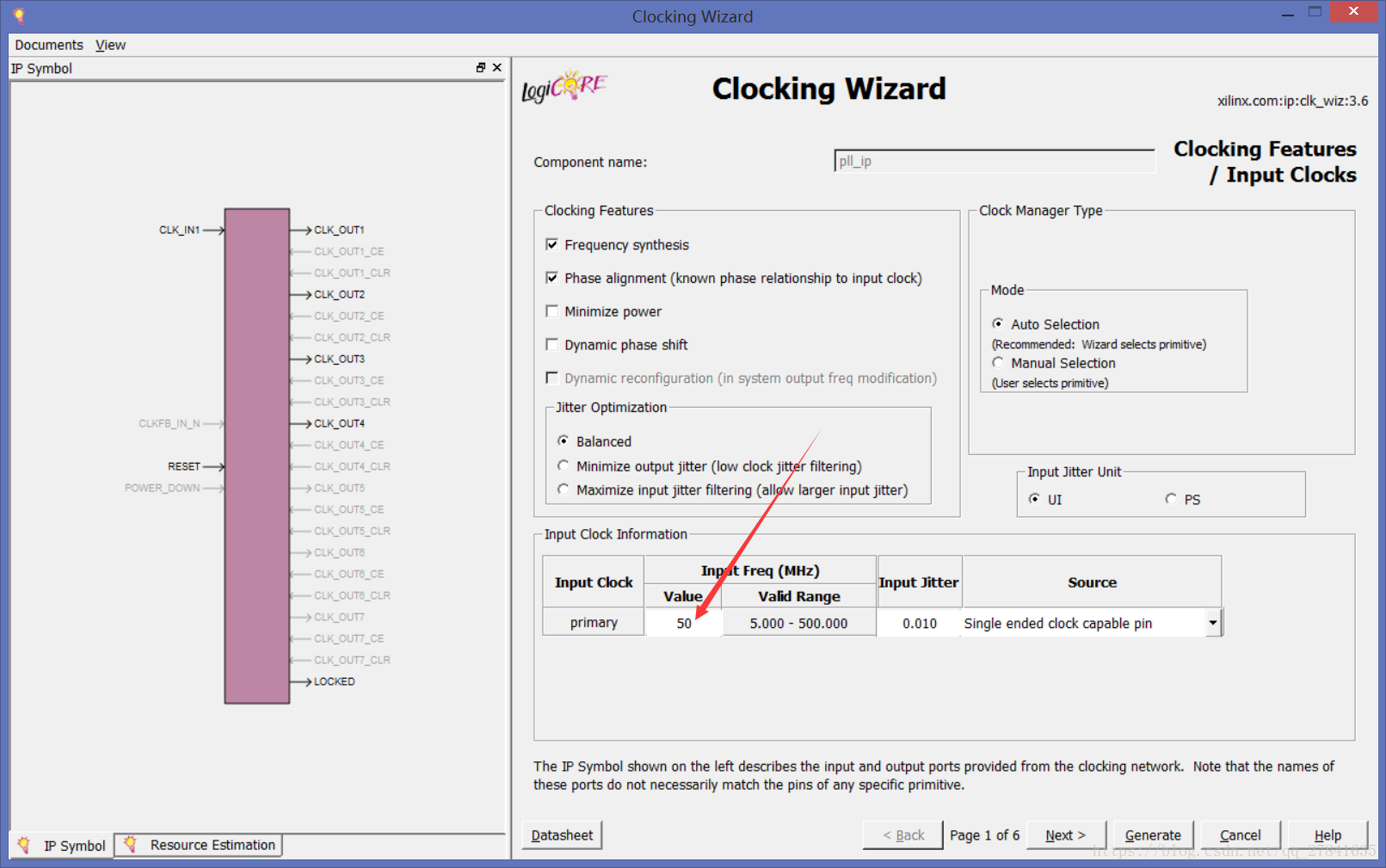

2、设置输入写为50M

3、设置想要的频率可多选

4、之后完成即可 调用

实例化pll_ip

5、程序

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

//仿真注意reset是先下降沿,在高电平

//////////////////////////////////////////////////////////////////////////////////

module model(

input clk,

input rst_n,

output clk_out //pll clock output

);

wire locked;

wire pll_clk_o;

/////////////////////PLL IP 调用////////////////////////////

pll_ip pll_ip_inst

(

.CLK_IN1(clk), // IN 50Mhz

.CLK_OUT1(pll_clk_o), // OUT 25Mhz

.CLK_OUT2(), // OUT 50Mhz

.CLK_OUT3(), // OUT 75Mhz

.CLK_OUT4(), // OUT 100Mhz

// Status and control signals

.RESET(~rst_n),// IN

.LOCKED(locked)); // OUT

///////////////调用 ODDR2 使时钟信号通过普通 IO 输出//////////////////

ODDR2 #(

.DDR_ALIGNMENT("NONE"), // Sets output alignment to "NONE", "C0" or "C1"

.INIT(1'b0), // Sets initial state of the Q output to 1'b0 or 1'b1

.SRTYPE("SYNC") // Specifies "SYNC" or "ASYNC" set/reset

) ODDR2_inst (

.Q(clk_out), // 1-bit DDR output data

.C0(pll_clk_o), // 1-bit clock input

.C1(~pll_clk_o), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D0(1'b1), // 1-bit data input (associated with C0)

.D1(1'b0), // 1-bit data input (associated with C1)

.R(1'b0), // 1-bit reset input

.S(1'b0) // 1-bit set input

);

endmodule

6、引脚

NET "clk" LOC = T8 | TNM_NET = sys_clk_pin;

TIMESPEC TS_sys_clk_pin = PERIOD sys_clk_pin 50000 kHz;

NET rst_n LOC = L3 | IOSTANDARD = "LVCMOS33";

NET clk_out LOC = J16 | IOSTANDARD = "LVCMOS33";

7、综合测试J16引脚即可

优势,快速方便,稳定。