项目简述

我们前面的两篇文章已经介绍了ISE中MIG IP的调用、用户接口、读写时序,相信大家从前面两篇文章的学习中已经可以掌握MIG的使用。那么为了巩固MIG的使用,我们将介绍一个DDR3的典型应用。

该项目的简述是:

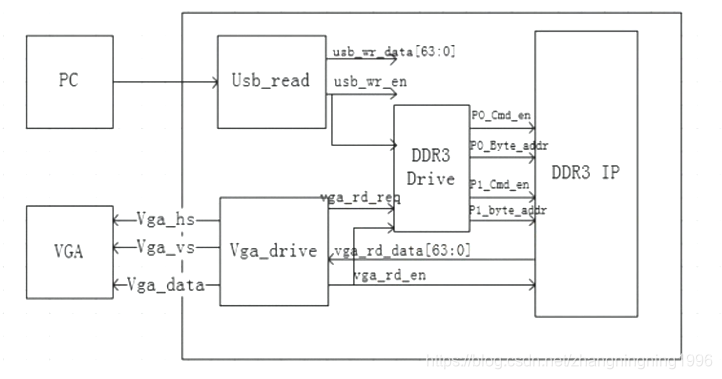

上位机通过USB发送一张图片,经过DDR3缓存,最终经由VGA接口显示在显示屏上面。

这里我们只给出框架与框图设计,相信同学们经由前面两篇文章的沉淀可以写出代码。

项目流程框图

从上面的系统框图中可以看出,主要就是DDR3Drive这个模块的书写,而这个模块经由我们前面的书写相信会变得比较容易。

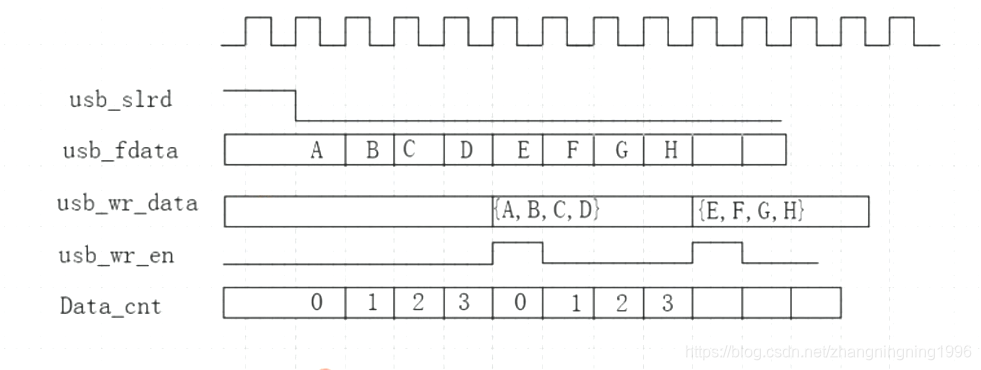

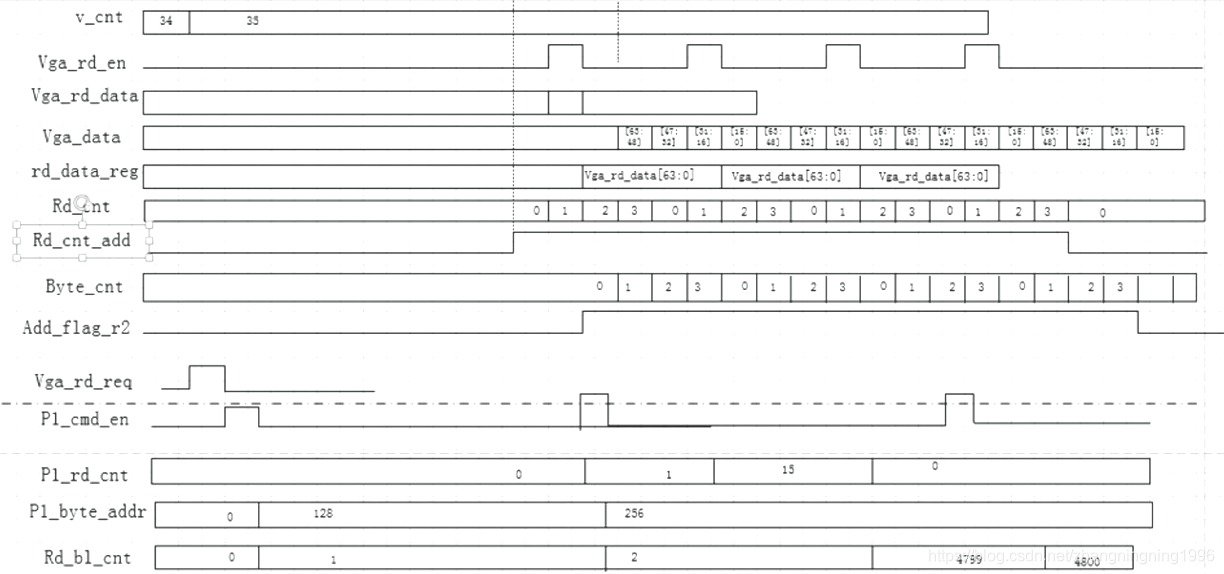

模块读写控制时序图

写DDR3部分的时序图如下:

读DDR3部分的时序如下:

我们这里由于没有相应的板卡,就不再给出具体的代码,相信大家也都可以调试出来,但是调试的过程是痛苦的,需要坚持。

参考文献

[1]、开源骚客

总结

创作不易,认为文章有帮助的同学们可以关注点赞支持。(工程也都在群中)对文章有什么看法或者需要更近一步交流的同学,可以加入下面的群: