第1关:全加器的设计—门级原始结构方式

如有任何不解或者想要答案代码,可在评论区喊话我哦,希望我的答案对你有帮助,点个关注再走吧,感谢!!!

本关卡最终答案:

任务描述

本关任务:使用门级原始结构方式描述全加器。

相关知识

全加器

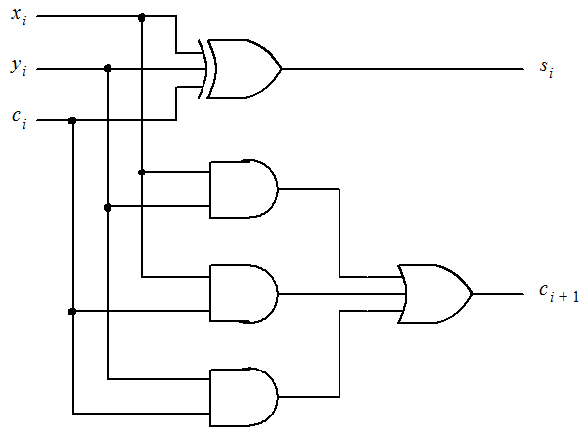

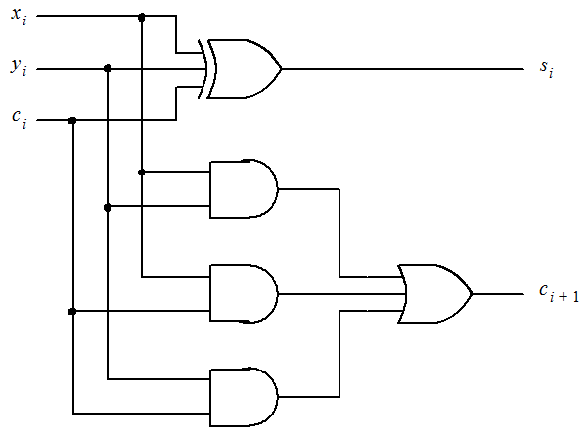

全加器FA(Full Adder)是实现两个1位二进制数(x、y)和来自低位进位(Ci或Cin)相加,产生和(s)与进位输出(Ci+1或Cout)的组合逻辑电路。电路原理图如下:

逻辑电路的结构化定义

Verilog包含了一系列与通用逻辑门电路对应的门级原始结构,一个逻辑门可以通过定义其函数名、输入和输出来表示。门级原始结构可以用于定义较大规模的电路。 门级原始结构又称门实例化 gate instantiation,语法如下:

gate_name [inst_name](output_port,input_port{,input_port});

例如,一个2输入与门,其输出为y,输入为x1和x2,则该与门可以表示为:

and( y, x1, x2 );

一个3输入或门,可以定义为:

or( y, x1, x2, x3 );

一个3输入异或门,可以定义为:

xor( y, x1, x2, x3 );

编程要求

根据上述电路图,在右侧编辑器中补充代码,注意接口信号以右侧代码中的命名为准。

测试说明

平台会对你编写的代码进行测试。

第2关:全加器的设计—连续赋值方式

如有任何不解或者想要答案代码,可在评论区喊话我哦,希望我的答案对你有帮助,点个关注再走吧,感谢!!!

本关卡最终答案:

任务描述

本关任务:使用连续赋值方式描述全加器。

相关知识

全加器

全加器FA(Full Adder)是实现两个1位二进制数(x、y)和来自低位进位(Ci或Cin)相加,产生和(s)与进位输出(Ci+1或Cout)的组合逻辑电路。电路原理图如下:

全加器的逻辑表达式如下: s=x⊕y⊕Cin Cout=xy+xCin+yCin

连续赋值assign

在Verilog中,与、或、非运算分别用 &、|、~ 表示,使用关键词assign对输出信号进行连续赋值,语法形式如下:

assign net_assignment{,net_assignment};

编程要求

根据上述电路图,在右侧编辑器中补充代码,注意接口信号以右侧代码中的命名为准。

测试说明

平台会对你编写的代码进行测试。

第3关:全加器的设计—行为描述方式(算术运算)

如有任何不解或者想要答案代码,可在评论区喊话我哦,希望我的答案对你有帮助,点个关注再走吧,感谢!!!

本关卡最终答案:

任务描述

本关任务:使用算术运算的行为方式方式描述全加器。

相关知识

全加器FA(Full Adder)是实现两个1位二进制数(x、y)和来自低位进位(Ci或Cin)相加,产生和(s)与进位输出(Ci+1或Cout)的组合逻辑电路。 使用算术运算,可以更抽象、更简洁地描述加法电路。

算术运算

Verilog中的算数运算加法的运算符为+,例如半加运算求和可以表示如下:

sum = a + b;

位连接运算符{s1,s2}

把a和b两个信号拼接成一个向量(多位二进制信号),如下:

{a,b}

把全加器的进位输出Cout与和s拼接起来,如下:

{Cout,s}

编程要求

在右侧编辑器中补充代码,注意使用位连接运算和算数运算。

测试说明

平台会对你编写的代码进行测试。

第4关:4位加法器设计—模块实例化

如有任何不解或者想要答案代码,可在评论区喊话我哦,希望我的答案对你有帮助,点个关注再走吧,感谢!!!

本关卡最终答案:

任务描述

任务描述

本关任务:用前面关卡设计的全加器模块实例化4个全加器(可依次命名为stage0,stage1,stage2,stage3或者U0,U1,U2,U3等等)构建4位行波进位加法器。

相关知识

include关键字

在当前模块中引入其它电路模块并实例化,语法如下:

`include "[path/]<module_name.v>"...module_name [instanse_name](portmap)//括号中为端口映射

如引入第一关中的电路模块并实例化:

`include "fulladd_gates.v" //引入第一关中的电路模块...fulladd_gates U0 (...);//实例化一个名为U0的模块,括号中按顺序给定对应信号fulladd_gates U1 (...);//实例化一个名为U1的模块...

向量(矢量)

Verilog中的向量类似于C语言中的数组,但定义形式有所区别,如下:

input [3:0] X; //input为输入信号wire [3:1] C; //wire为电路内部连线

编程要求

根据提示,在右侧编辑器中补充代码。

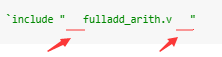

常见错误

电路文件(模块)引入时,引号前后不应该有空格,如

测试说明

平台会对你编写的代码进行测试。

第5关:n位加法器设计—算术运算方式

如有任何不解或者想要答案代码,可在评论区喊话我哦,希望我的答案对你有帮助,点个关注再走吧,感谢!!!

本关卡最终答案:

任务描述

本关任务:用算术运算方式构建n位加法器并进行溢出检测。

相关知识

参数设定parameter

Verilog中使用parameter关键字定义参数,如定义加法器位宽:

parameter n = 16;

模块实例化时可以给参数重新赋值,如下:

addern_arith U1(...);defparam U1.n = 8 ;

溢出检测

有符号数的加法运算(X+Y=S)溢出检测原理之一: X和Y符号相同并与结果S符号相反则溢出,逻辑表达式如下:

overflow=Xn−1Yn−1Sn−1+Xn−1Yn−1Sn−1

有符号数的加法运算(X+Y=S)溢出检测原理之二: 符号位进位与最高有效位进位相反则溢出,逻辑表达式如下:

overflow=Cn⊕Cn−1

有符号数的加法运算(X+Y=S)溢出检测原理之三: 采用双符号位,和S的两个符号位相反则溢出,逻辑表达式如下:

overflow=Sn+1⊕Sn

编程要求

根据提示,在右侧编辑器中补充代码。

测试说明

平台会对你编写的代码进行测试。

第6关:8421BCD码加法器设计(1位十进制)

如有任何不解或者想要答案代码,可在评论区喊话我哦,希望我的答案对你有帮助,点个关注再走吧,感谢!!!

本关卡最终答案:

任务描述

本关任务:设计8421BCD码加法器(1位十进制)。

相关知识

在4位二进制加法(X+Y=Z)的基础上进行修正,从而求得1位十进制相加的结果S。 如果Z<=9,加0修正,即S=Z; 如果Z >9,加6修正,即S=Z+9。

编程要求

根据提示,在右侧编辑器中补充代码。

测试说明

平台会对你编写的代码进行测试。