- 分别采用结构描述和行为描述方式设计一个基本的D触发器,在此基础上,采用结构描述的方式,用8个D触发器构成一个8位移位寄存器。进行功能仿真,查看结果,把上述内容整理到实验报告。

- (1)行为描述:

- 单个D触发器

功能代码:

module shiyan31(q,d,clk);

input d,clk;

output q;

reg q;

always @(posedge clk) %在时钟的每个下降沿

begin

q<=d;

end

endmodule

测试代码:

`timescale 1ns/1ns

module test();

reg d,clk;

wire q;

shiyan31 U1(q,d,clk);

always #10 clk=~clk;

initial

begin clk =0; %每隔20s输入一个d

#20 d=1;

#20 d=0;

#20 d=1;

#20 d=0;

#20 d=1;

#20 d=0;

#20 d=1;

#200 $finish;

end

endmodule

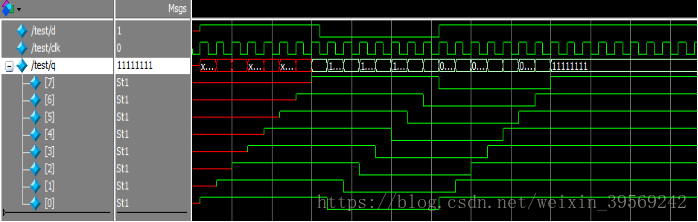

- 8位D触发的移位寄存器:

功能程序:

module shiyan31(q,d,clk);

input d,clk;

output q;

wire d;

wire[7:0] q;

D U2(q[0],d,clk); %调用8次Module D,第一个的输入为d,其它输入为上一级的输出

D U3(q[1],q[0],clk);

D U4(q[2],q[1],clk);

D U5(q[3],q[2],clk);

D U6(q[4],q[3],clk);

D U7(q[5],q[4],clk);

D U8(q[6],q[5],clk);

D U9(q[7],q[6],clk);

endmodule

module D(q,d,clk);%一个D触发器的module

input d,clk;

output q;

reg q;

always @(posedge clk)

begin

q<=d;

end

endmodule

测试程序:

`timescale 1ns/1ns

module test();

reg d,clk;

wire[7:0] q;

shiyan31 U1(q,d,clk);

always #10 clk=~clk;

initial

begin clk =0;

#10 d=1;

#150 d=0;

#150 d=1;

#900 $stop;

end

endmodule

(2)结构描述:

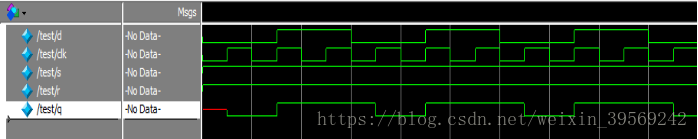

- 单个D触发器

功能程序:

module shiyan31(clk,d,s,r,q);

input clk,d,s,r;

output q;

wire q1,q2,q3,q4,q0;

nand (q1,s,q4,q2);

nand(q2,q1,r,clk);

nand(q3,q2,clk,q4);

nand(q4,q3,d,r);

nand(q,s,q2,q0);

nand(q0,q,q3,r);

endmodule

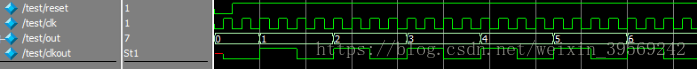

测试程序:

`timescale 1ns/1ns

module test();

reg d,clk,s,r;

wire q;

shiyan31 U1(clk,d,s,r,q);

always #10 clk=~clk;

always #30 d=~d;

initial

begin clk =0;s=1;r=1;d=0;

#200 $stop;

end

endmodule

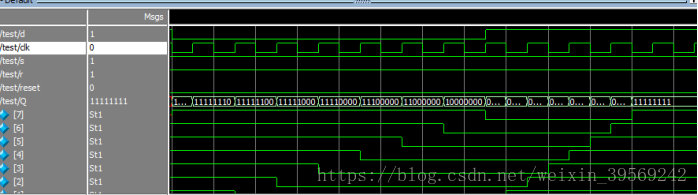

- 8位移位寄存器:

功能代码:

module shiyan31(Q,d,clk,s,r,reset);

input d,clk,s,r,reset;

output Q;

wire d;

wire[7:0] Q;

wire s,r;

D U2(clk,d,s,r,Q[0]);

D U3(clk,Q[0],s,r,Q[1]);

D U4(clk,Q[1],s,r,Q[2]);

D U5(clk,Q[2],s,r,Q[3]);

D U6(clk,Q[3],s,r,Q[4]);

D U7(clk,Q[4],s,r,Q[5]);

D U8(clk,Q[5],s,r,Q[6]);

D U9(clk,Q[6],s,r,Q[7]);

endmodule

module D(clk,d,s,r,q);

input clk,d,s,r;

output q;

wire q1,q2,q3,q4,q0;

nand (q1,s,q4,q2);

nand(q2,q1,r,clk);

nand(q3,q2,clk,q4);

nand(q4,q3,d,r);

nand(q,s,q2,q0);

nand(q0,q,q3,r);

Endmodule

测试代码:

`timescale 1ns/1ns

module test();

reg d,clk,s,r,reset;

wire [7:0] Q;

shiyan31 U1(Q,d,clk,s,r,reset);

always #10 clk=~clk;

initial

begin clk =0;s=1;r=1;reset=1;

#10 reset=0;

#10 d=1;

#150 d=0;

#150 d=1;

#900 $stop;

end

endmodule

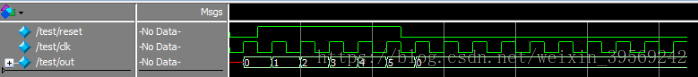

- 设计1个8位的计数器,带同步复位功能,复位信号低电平有效。(1)在同一个module中设计1个4分频器,采用分频器输出脉冲作为计数器的输入。(2)将4分频器设计成独立的module,实例化四分频器模块,完成与(1)相同的功能。进行综合和仿真,查看功能仿真结果,把上述内容整理到实验报告。

- (1)计数器:

功能代码:

module shiyan32(out,reset,clk);

input clk,reset;

output reg[7:0] out;

always @(posedge clk)

begin

if(!reset)

out<=8'h00;%同步置位

else

out<=out+1;%来一个时钟上升沿,则加1

end

endmodule

测试代码:

`timescale 1ns/1ns

module test();

reg reset,clk;

wire[7:0] out;

shiyan32 U1(out,reset,clk);

always #10 clk=~clk;

initial

begin clk=0;reset=0;

#20 reset=1;

#100 reset=0;

#200 $stop;

end

endmodule

(2)同一个module 模块:

功能程序:

module shiyan32(clkout,out,reset,clk);

input clk,reset;

output clkout;

output reg[7:0] out;

reg clkout;

reg [4:0] qout;

always @(posedge clk)

begin if(!reset)

begin

clkout<=0;

qout<=0;%同步置位,clkout,qout都为0

end

else begin

if(qout==1)%当qout为1是表示经历了两个时钟,则达到了占空比为50%的四分频

begin

qout <=0;

clkout<=~clkout;

end

else

qout <=qout+1;

end

end

always @(posedge clkout or negedge reset) %用分频之后的clk时钟作为计数器的输入时钟

begin

if(!reset)

out<=8'h00;

else

out<=out+1;

end

endmodule

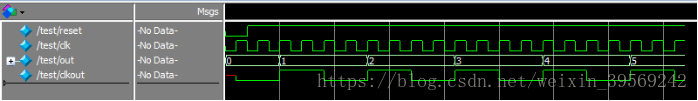

测试程序:

`timescale 1ns/1ns

module test();

reg reset,clk;

wire[7:0] out;

shiyan32 U1(clkout,out,reset,clk);

always #10 clk=~clk;

initial

begin clk=0;reset=0;%reset=0%低电平置位

#20 reset=1;

#1000 $stop;

end

Endmodule

(3)两个module 模块:

功能代码:

module shiyan32(out,clkout,reset,clk);

input clk,reset;

output reg[7:0] out;

output clkout;

wire clkout;

wire [4:0] qout;

clk4 u1(reset,clk,clkout,qout);%四分频时钟的模块调用,在调用的模块中出现的信号,可以不出现在主模块中

always @(posedge clkout or negedge reset)

begin

if(!reset)

out<=8'h00;

else

out<=out+1;

end

endmodule

module clk4 (reset,clk,clkout,qout);

input reset,clk;

output clkout,qout;

reg clkout;

reg [4:0] qout;

always @(posedge clk)

begin if(!reset)

begin clkout<=0;qout<=0;end

else begin if(qout==1)

begin qout <=0; clkout<=~clkout; end

else qout <=qout+1; end end

Endmodule

测试程序:

`timescale 1ns/1ns

module test();

reg reset,clk;

wire[7:0] out;

shiyan32 U1(out,clkout,reset,clk);

always #10 clk=~clk;

initial

begin clk=0;reset=0;

#20 reset=1;

#400 $stop;

end

endmodule