名称:vivado数字秒表verilog代码ego1开发板电子秒表跑表

软件:VIVADO

语言:Verilog

代码功能:

数字秒表设计

1、秒表的设计精确到10毫秒(0.01秒)

2、可通过按键控制秒表启动、暂停、复位

3、数码管显示分、秒、毫秒

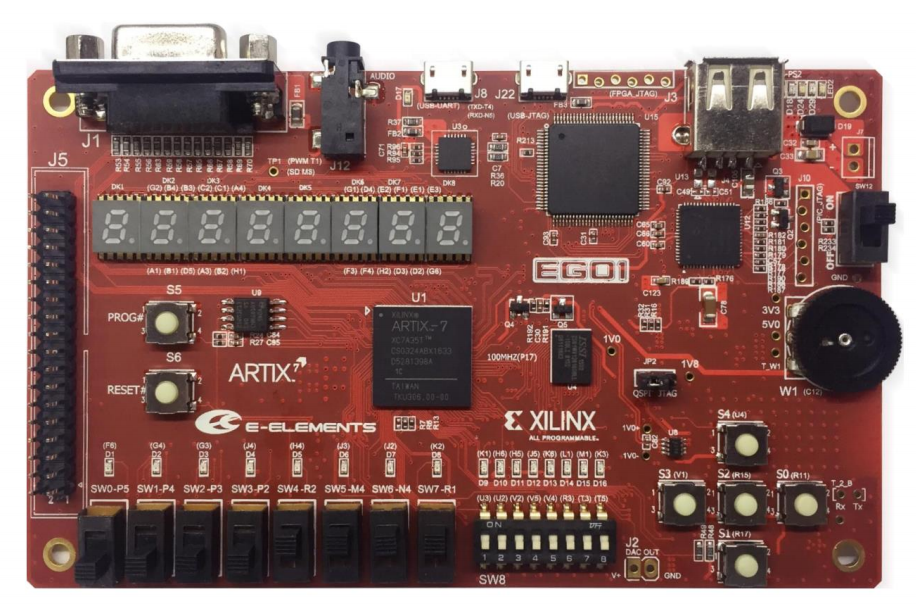

本代码已在ego1开发板验证,开发板如下,其他开发板可以修改管脚适配:

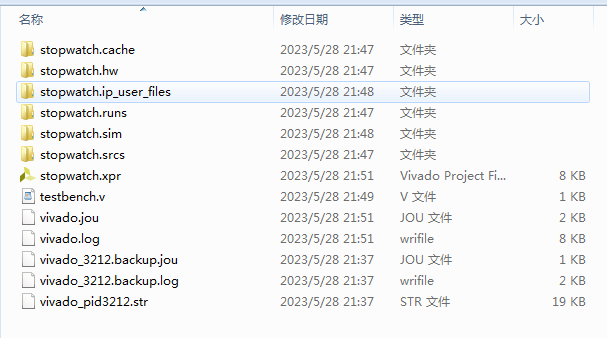

1. 工程文件

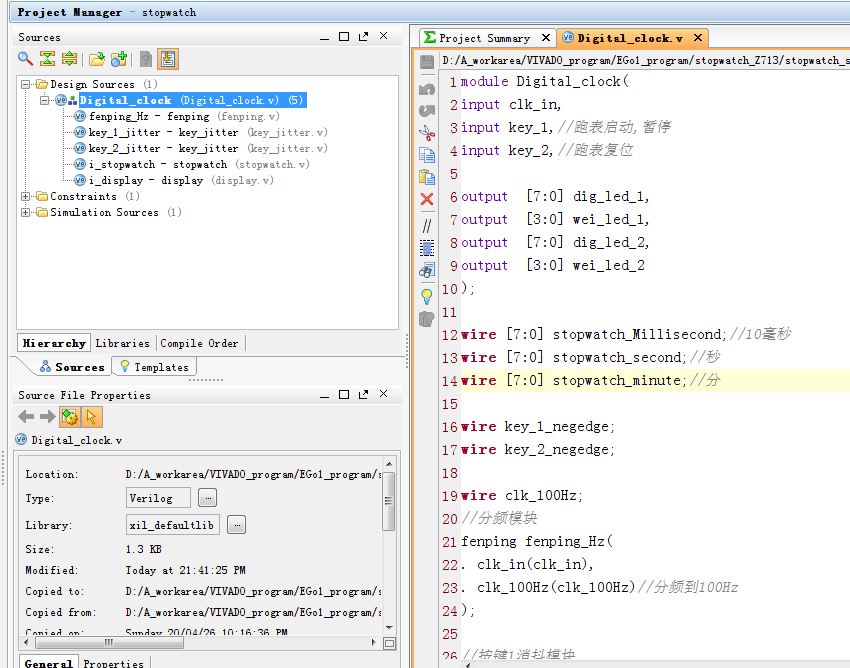

2. 程序文件

3. 程序编译

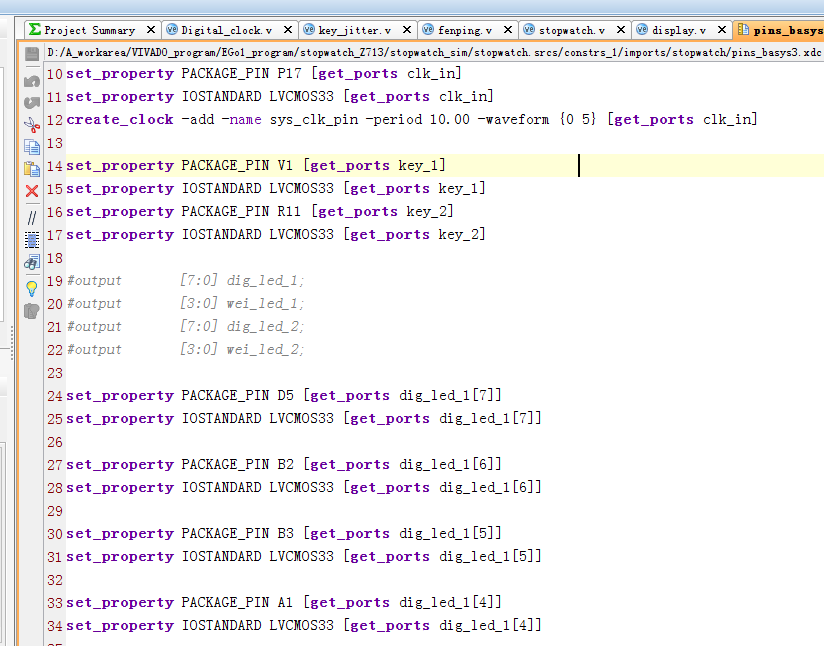

4. 管脚分配

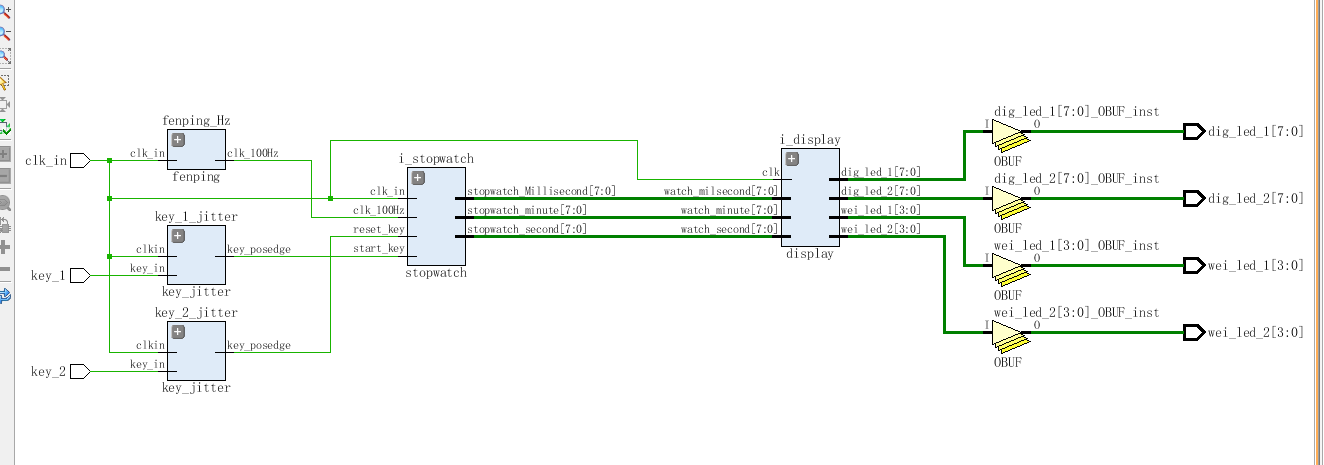

5. RTL图

6. 仿真

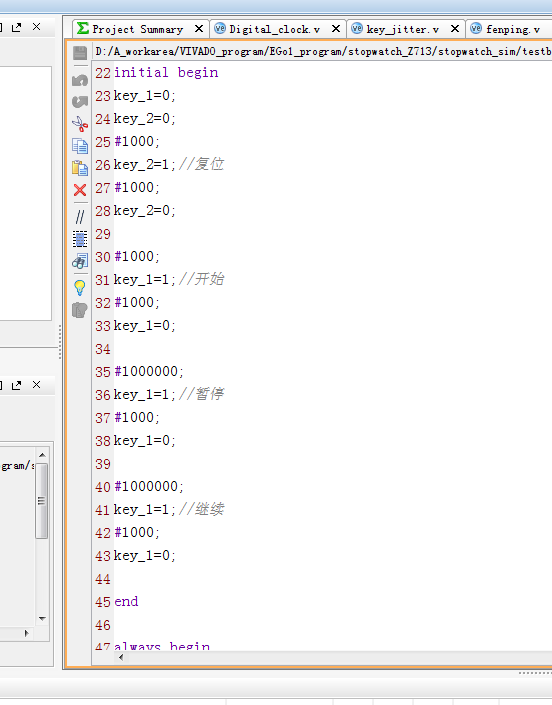

Testbench

整体仿真图

分频模块

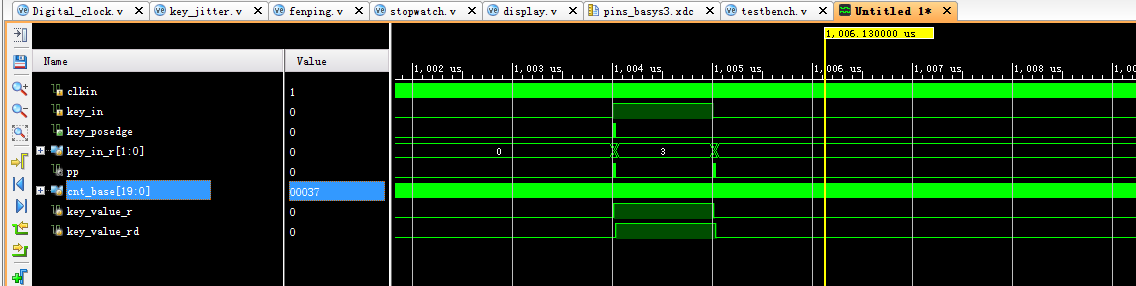

按键消抖模块

秒表控制模块

显示译码模块

部分代码展示:

//跑表模块 module stopwatch( input clk_in, input clk_100Hz,//100Hz--对应10ms input start_key,//启动//暂停 input reset_key,//复位 output [7:0] stopwatch_Millisecond,//10毫秒 output [7:0] stopwatch_second,//秒 output [7:0] stopwatch_minute//分 ); parameter idle_state=3'd0; parameter cnt_time_state=3'd1; parameter hold_time_state=3'd2; parameter reset_time_state=3'd3; reg [2:0] state=3'd0; //计时状态机 always@(posedge clk_in) if(reset_key) state<=reset_time_state;//复位状态 else case(state) reset_time_state://复位状态 state<=idle_state; idle_state://空闲状态 if(start_key) state<=cnt_time_state; else state<=idle_state; cnt_time_state://计时状态 if(start_key) state<=hold_time_state; else state<=cnt_time_state; hold_time_state://暂停状态 if(start_key) state<=cnt_time_state; else state<=hold_time_state; default:; endcase reg [7:0] Millisecond_cnt=8'd0;//10毫秒 reg [7:0] second_cnt=8'd0;//秒 reg [7:0] minute_cnt=8'd0;//分 always@(posedge clk_in) if(state==reset_time_state)//复位状态 minute_cnt<=8'd0; else if(state==cnt_time_state && clk_100Hz==1)//计时状态 if(Millisecond_cnt==8'd99 && second_cnt==8'd59)//59秒99'时向前记1分 if(minute_cnt<8'd59) minute_cnt<=minute_cnt+8'd1;//计时到990ms,下一次就到1秒了 else minute_cnt<=8'd0; else minute_cnt<=minute_cnt; else; always@(posedge clk_in) if(state==reset_time_state)//复位状态 second_cnt<=8'd0; else if(state==cnt_time_state && clk_100Hz==1)//计时状态 if(Millisecond_cnt==8'd99)//990ms时向前记1秒 if(second_cnt<8'd59) second_cnt<=second_cnt+8'd1;//计时到990ms,下一次就到1秒了 else second_cnt<=8'd0; else second_cnt<=second_cnt; else; always@(posedge clk_in) if(state==reset_time_state)//复位状态 Millisecond_cnt<=8'd0; else if(state==cnt_time_state && clk_100Hz==1)//计时状态 if(Millisecond_cnt<8'd99)//计时到990ms,下一次就到1秒了 Millisecond_cnt<=Millisecond_cnt+8'd1; else Millisecond_cnt<=8'd0;//计时到990ms,下一次就到1秒了 else; assign stopwatch_Millisecond=Millisecond_cnt; assign stopwatch_second=second_cnt; assign stopwatch_minute=minute_cnt; endmodule