名称:洗衣机控制器VHDL代码ego1开发板vivado软件

软件:VIVADO

语言:VHDL

代码功能:

(1)设计一个洗衣机控制器,使洗衣机作如下运转:定时启动—〉正转20秒—〉暂停10秒—〉反转20秒—〉暂停10秒—〉定时不到,重复上面过程。

(2)若定时到,则停止,并发出提示信号。

(3)用两个数码管显示洗涤的预置时间(15分钟),按倒计时方式对洗涤过程作计时显示,直到时间到停机;洗涤过程由开始信号开始。

(4)三只LED灯表示正转、反转、暂停三个状态。

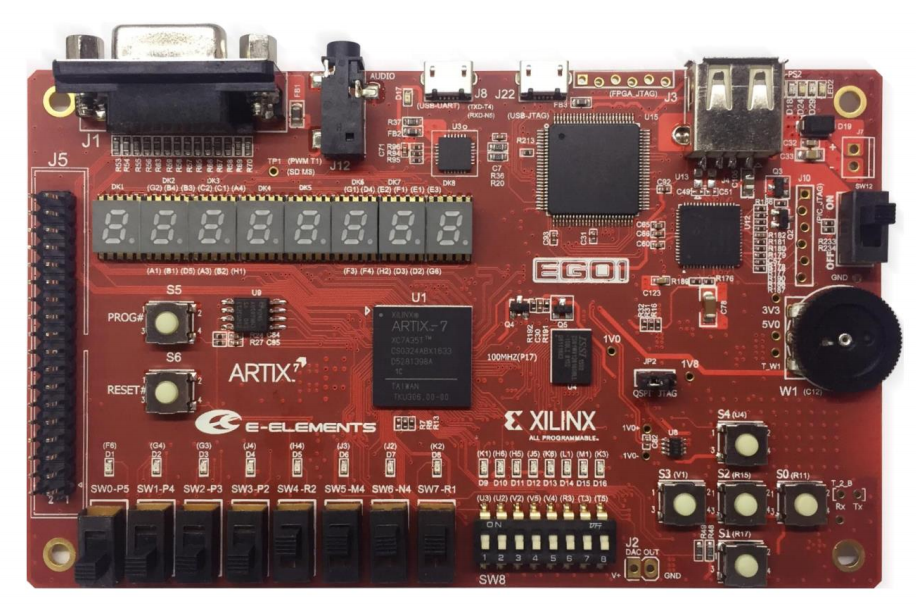

本代码已在ego1开发板验证,开发板如下,其他开发板可以修改管脚适配:

1. 工程文件

代码功能

(1)设计一个洗衣机控制器,使洗衣机作如下运转:定时启动—〉正转20秒—〉暂停10秒—〉反转20秒—〉暂停10秒—〉定时不到,重复上面过程。

(2)若定时到,则停止,并发出提示信号。

(3)用两个数码管显示洗涤的预置时间(15分钟),按倒计时方式对洗涤过程作计时显示,直到时间到停机;洗涤过程由开始信号开始。

(4)三只LED灯表示正转、反转、暂停三个状态。

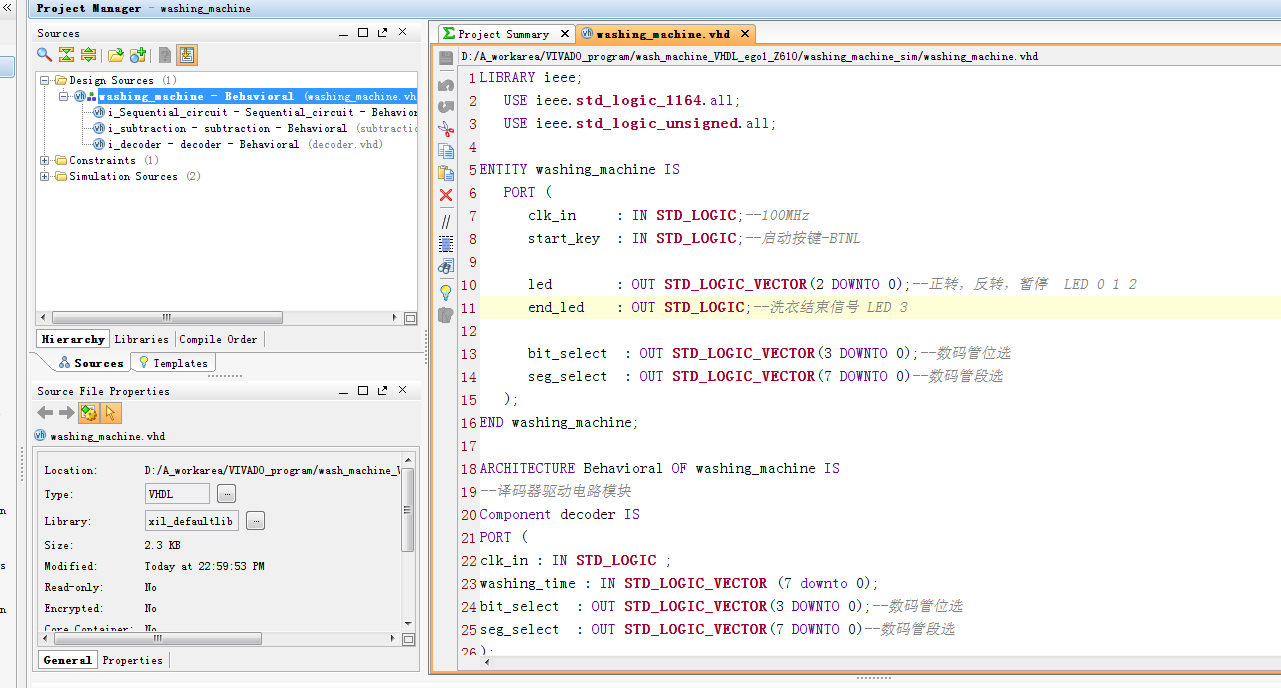

2. 程序文件

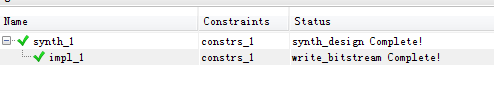

3. 程序编译

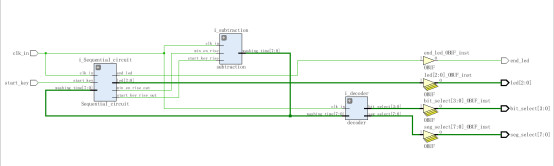

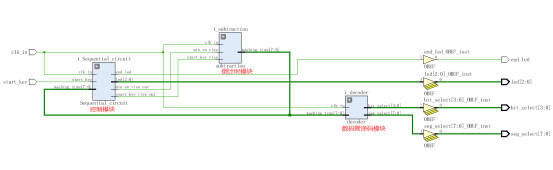

4. RTL图(代码框图)

5. 管脚分配

6. Testbench

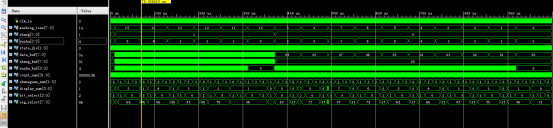

7. 仿真图

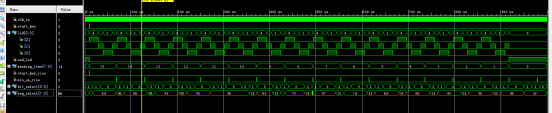

整体仿真图

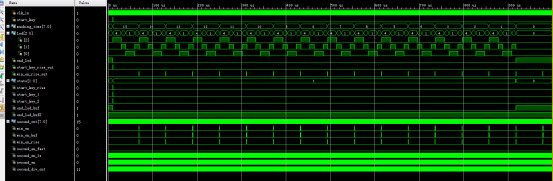

控制模块

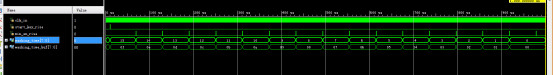

倒计时模块

数码管译码模块

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; ENTITY washing_machine IS PORT ( clk_in : IN STD_LOGIC;--100MHz start_key : IN STD_LOGIC;--启动按键-BTNL led : OUT STD_LOGIC_VECTOR(2 DOWNTO 0);--正转,反转,暂停 LED 0 1 2 end_led : OUT STD_LOGIC;--洗衣结束信号 LED 3 bit_select : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--数码管位选 seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选 ); END washing_machine; ARCHITECTURE Behavioral OF washing_machine IS --译码器驱动电路模块 Component decoder IS PORT ( clk_in : IN STD_LOGIC ; washing_time : IN STD_LOGIC_VECTOR (7 downto 0); bit_select : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--数码管位选 seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选 ); end Component ; Component subtraction IS PORT ( clk_in : IN STD_LOGIC;--50Hz start_key_rise : IN STD_LOGIC; min_en_rise : IN STD_LOGIC; washing_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); end Component ; Component Sequential_circuit IS PORT ( clk_in : IN STD_LOGIC;--50Hz start_key : IN STD_LOGIC;--启动按键 washing_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); led : OUT STD_LOGIC_VECTOR(2 DOWNTO 0);--正转,反转,暂停 end_led : OUT STD_LOGIC;--洗衣结束信号 start_key_rise_out : OUT STD_LOGIC; min_en_rise_out : OUT STD_LOGIC ); end Component ; SIGNAL washing_time : STD_LOGIC_VECTOR(7 DOWNTO 0) := "00000000";--预置洗衣时间15分钟 SIGNAL start_key_rise : STD_LOGIC:='0'; SIGNAL min_en_rise : STD_LOGIC:='0'; SIGNAL duanxuan2 : STD_LOGIC_VECTOR(7 DOWNTO 0) := "00000000"; SIGNAL duanxuan1 : STD_LOGIC_VECTOR(7 DOWNTO 0) := "00000000"; BEGIN --控制模块 i_Sequential_circuit : Sequential_circuit port map ( clk_in => clk_in, start_key => start_key, washing_time => washing_time, led => led, end_led => end_led, start_key_rise_out => start_key_rise, min_en_rise_out => min_en_rise ); --倒计时模块 i_subtraction : subtraction port map ( clk_in => clk_in, start_key_rise => start_key_rise, min_en_rise => min_en_rise, washing_time => washing_time ); --译码器驱动电路模块 i_decoder : decoder port map ( clk_in => clk_in, washing_time => washing_time, bit_select =>bit_select,--数码管位选 seg_select =>seg_select--数码管段选 ); END Behavioral;