名称:vivado序列检测器verilog代码ego1开发板验证

软件:VIVADO

语言:Verilog

代码功能:

设计一个111序列检测器。

要求:当检测到3个或3个以上的1时,输出为1,其他输入情况输出为0.

画出状态转移图,完成 Verilog描述。

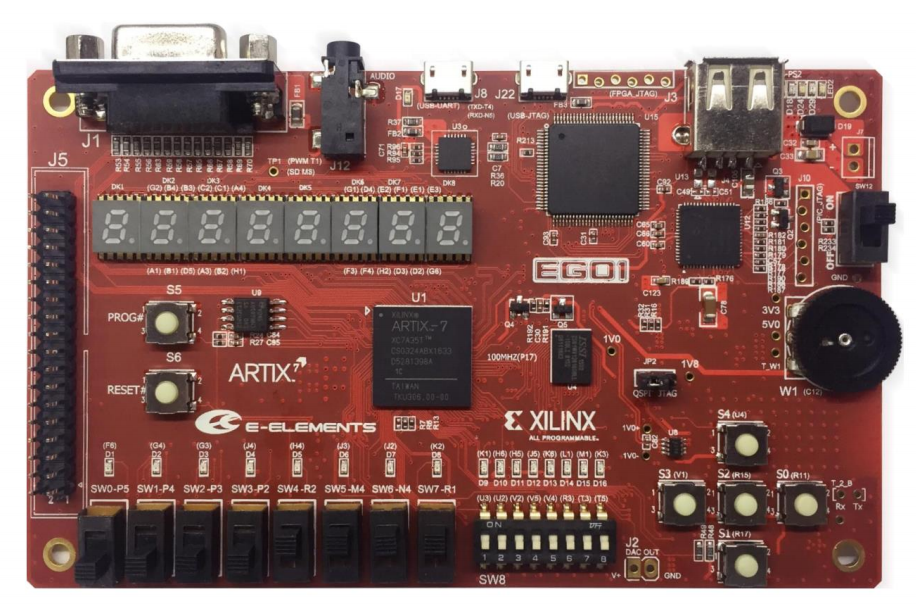

本代码已在ego1开发板验证,开发板如下,其他开发板可以修改管脚适配:

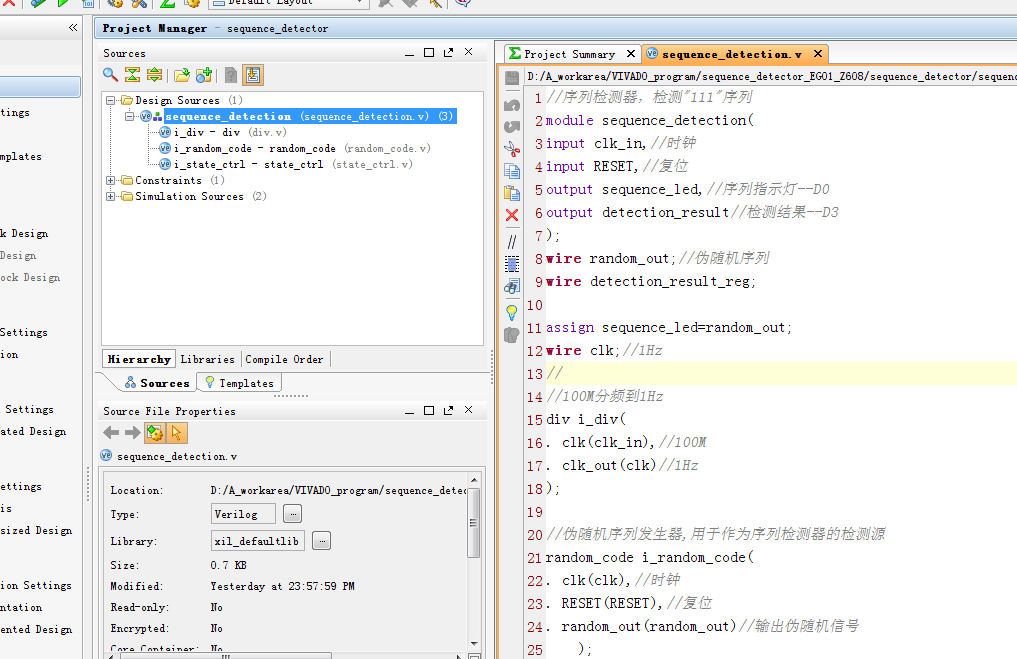

1. 工程文件

2. 程序文件

3. 程序编译

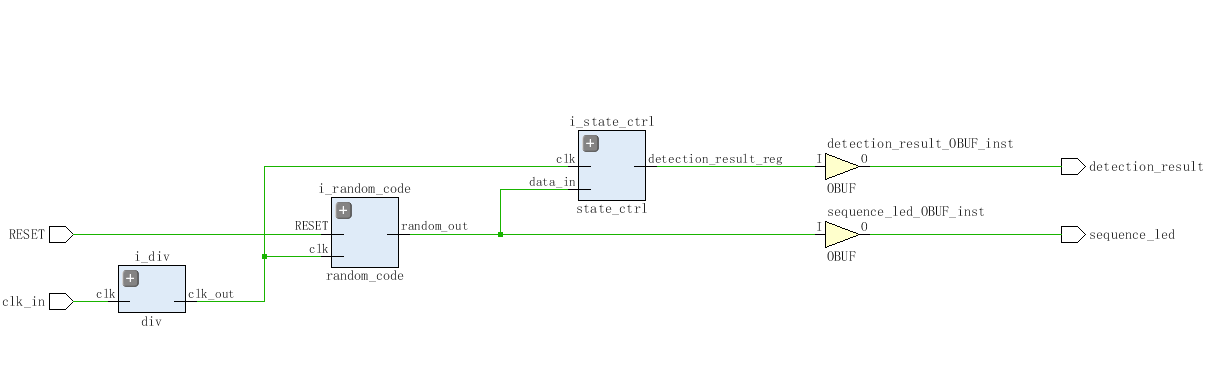

4. RTL图

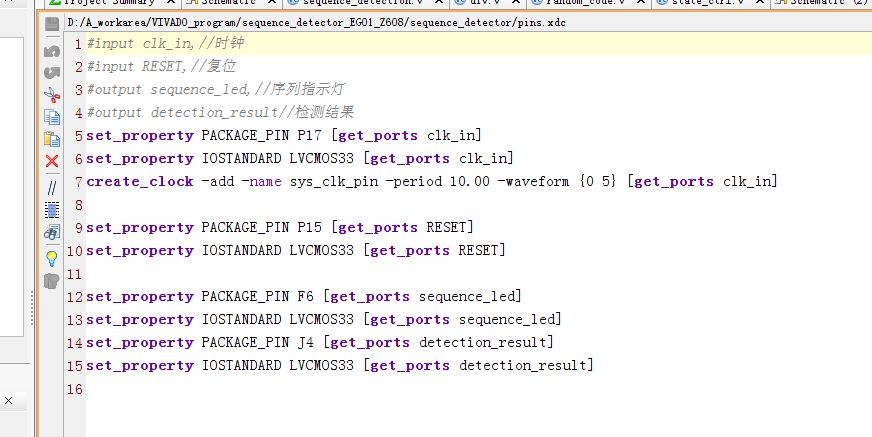

5. 管脚分配

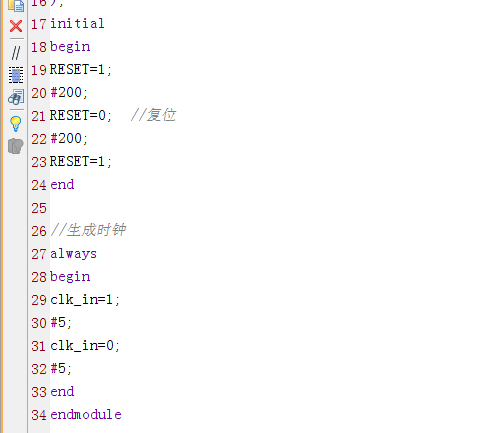

6. Testbench

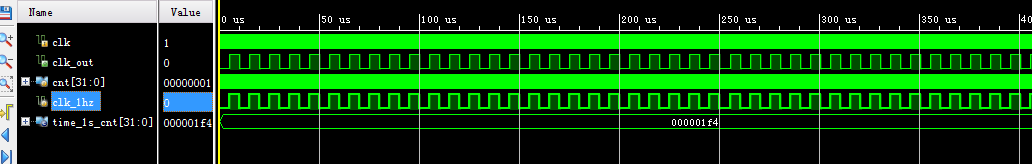

7. 仿真图

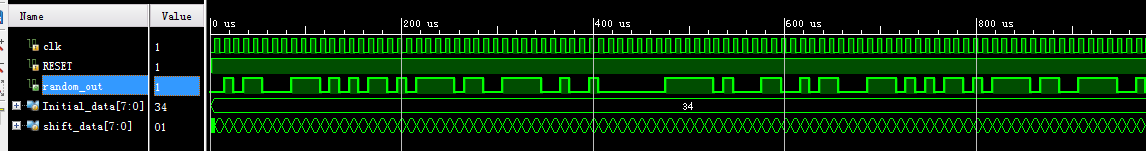

整体仿真图

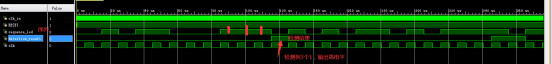

分频模块

随机序列产生模块

状态机控制模块

部分代码展示:

//序列检测器,检测"111"序列 module sequence_detection( input clk_in,//时钟 input RESET,//复位 output sequence_led,//序列指示灯--D0 output detection_result//检测结果--D3 ); wire random_out;//伪随机序列 wire detection_result_reg; assign sequence_led=random_out; wire clk;//1Hz // //100M分频到1Hz div i_div( . clk(clk_in),//100M . clk_out(clk)//1Hz ); //伪随机序列发生器,用于作为序列检测器的检测源 random_code i_random_code( . clk(clk),//时钟 . RESET(RESET),//复位 . random_out(random_out)//输出伪随机信号 ); //状态机控制模块 state_ctrl i_state_ctrl( . clk(clk),//时钟 . data_in(random_out),//序列输入 . detection_result_reg(detection_result)//检测结果 ); endmodule