名称:八输入的表决器ego1开发板verilog代码vivado软件

软件:VIVADO

语言:Verilog

代码功能:

设计一个八输入的表决器

要求:0-3个同意A灯亮(闪烁); 4-5个同意B亮(闪烁);6-8个同意C亮(闪烁)

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

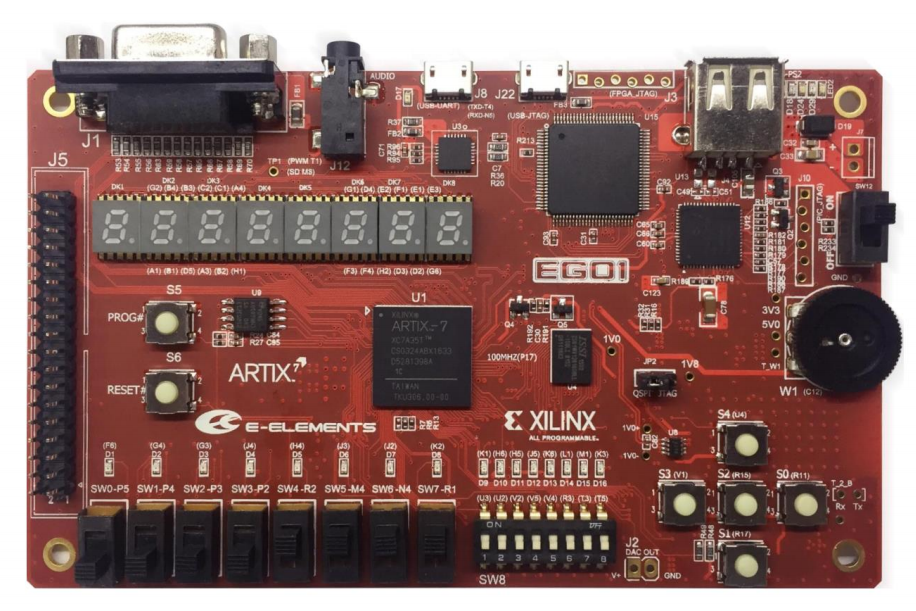

本代码已在ego1开发板验证,开发板如下,其他开发板可以修改管脚适配:

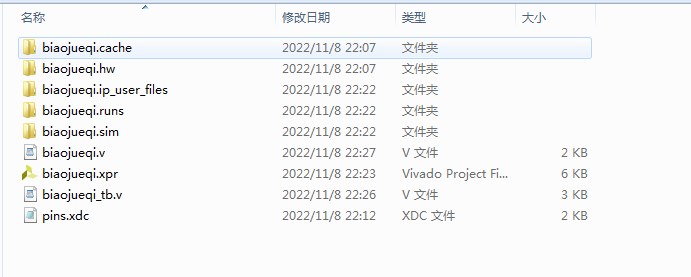

1. 工程文件

2. 程序文件

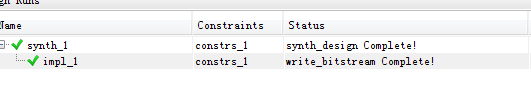

3. 程序编译

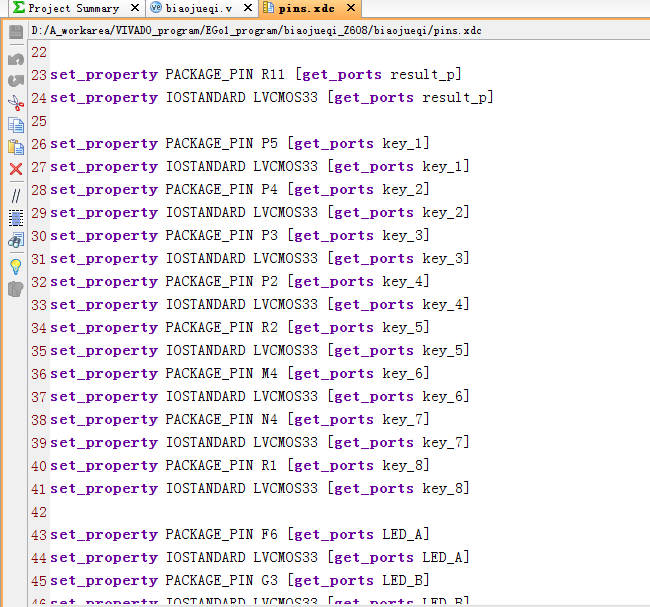

4. 管脚分配

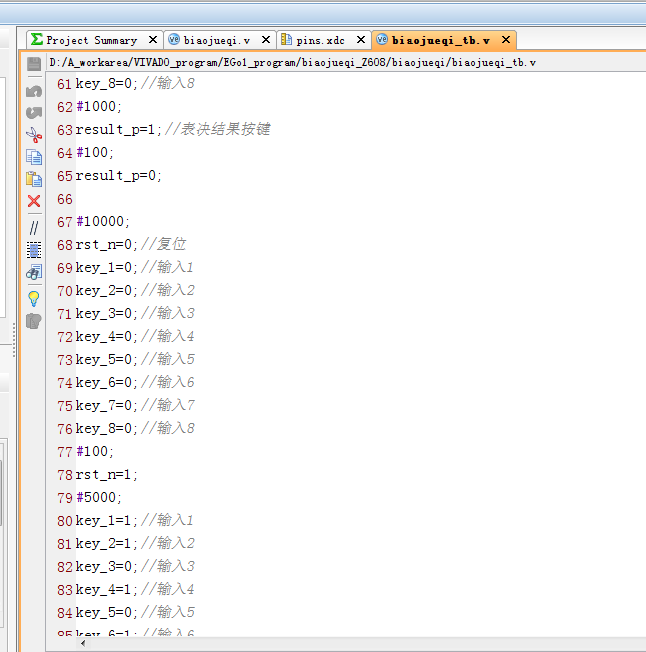

5. Testbench

6. 仿真图

部分代码展示:

//8输入表决器 module biaojueqi( input clk,//时钟 input rst_n,//复位 input result_p,//表决结果按键 input key_1,//输入1 input key_2,//输入2 input key_3,//输入3 input key_4,//输入4 input key_5,//输入5 input key_6,//输入6 input key_7,//输入7 input key_8,//输入8 //LED灯 output reg LED_A, output reg LED_B, output reg LED_C ); wire [3:0] agree_num; assign agree_num=key_1+key_2+key_3+key_4+key_5+key_6+key_7+key_8;//计算有几个同意 reg [31:0] div_cnt=32'd0; reg clk_1HZ=0; always@(posedge clk) if(div_cnt>=32'd50_000_000)begin//计数,上板调试时计数50_000_000,仿真时为减小仿真耗时计数改为50 div_cnt<=0;//清零 clk_1HZ<=~clk_1HZ;//翻转得到1Hz的闪烁信号 end else div_cnt<=div_cnt+1;//累加 parameter s_idle=2'd0; parameter s_result=2'd1; parameter s_led=2'd2; reg [1:0] state=2'd0; //状态机 always@(posedge clk or negedge rst_n) if(rst_n==0)//复位 state<=s_idle; else case(state) s_idle://初始状态 if(result_p)//表决结果按键 state<=s_result; else state<=s_idle; s_result://表决结果状态