名称:学号滚动显示verilog代码vivado软件ego1开发板

软件:VIVADO

语言:Verilog

代码功能:

学号滚动显示 Course Outline实验要求

》用EGO1实验板卡上的8个7段数码管滚动显示你的学号;

》例如:李佳一(LJY)学号2019040509;

》滚动显示16个字符为: HEULJY2019040509HEULJY201904.

》实验提示

》学号中的数码被存储在一个64位的寄存器msg_ array[0:63]中;

》在时钟上升沿,把msg_aray[0:63]中的内容向左循环移动4位,即 msg_ array[0:3]的内容移到msg_ array[60:63]中(注意: msg array数组中的0位为高位),之后在每个时钟上升沿时进行循环移位;

》用频率3Hz的时钟在7段数码管上移动字符;

》SW7为暂停信号,SW7为1时暂停移动;S0为复位信号,按下后重新开始移动

》姓名拼音字母的7段编码见下页;若姓名为陈晨,则扩展为陈晨晨。

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

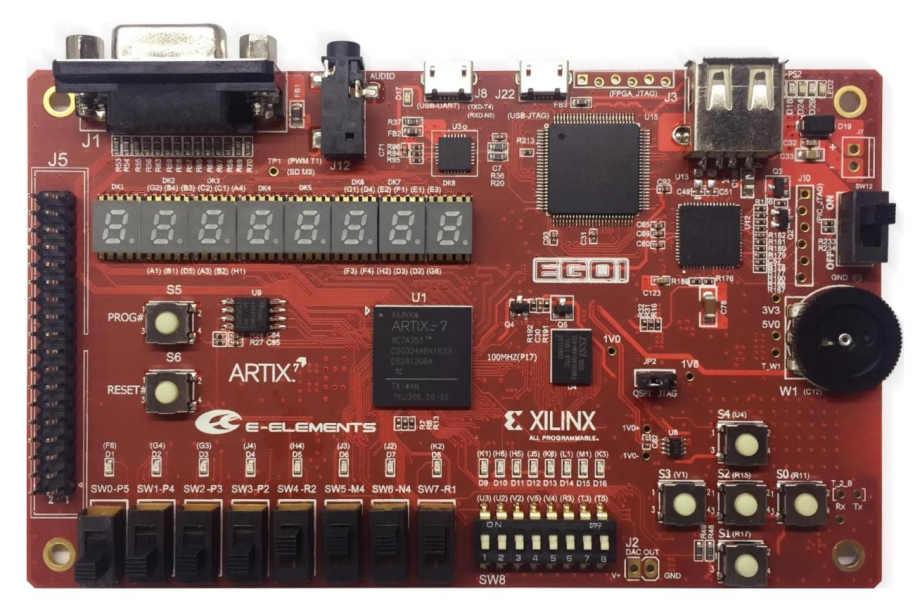

本代码已在ego1开发板验证,开发板如下,其他开发板可以修改管脚适配:

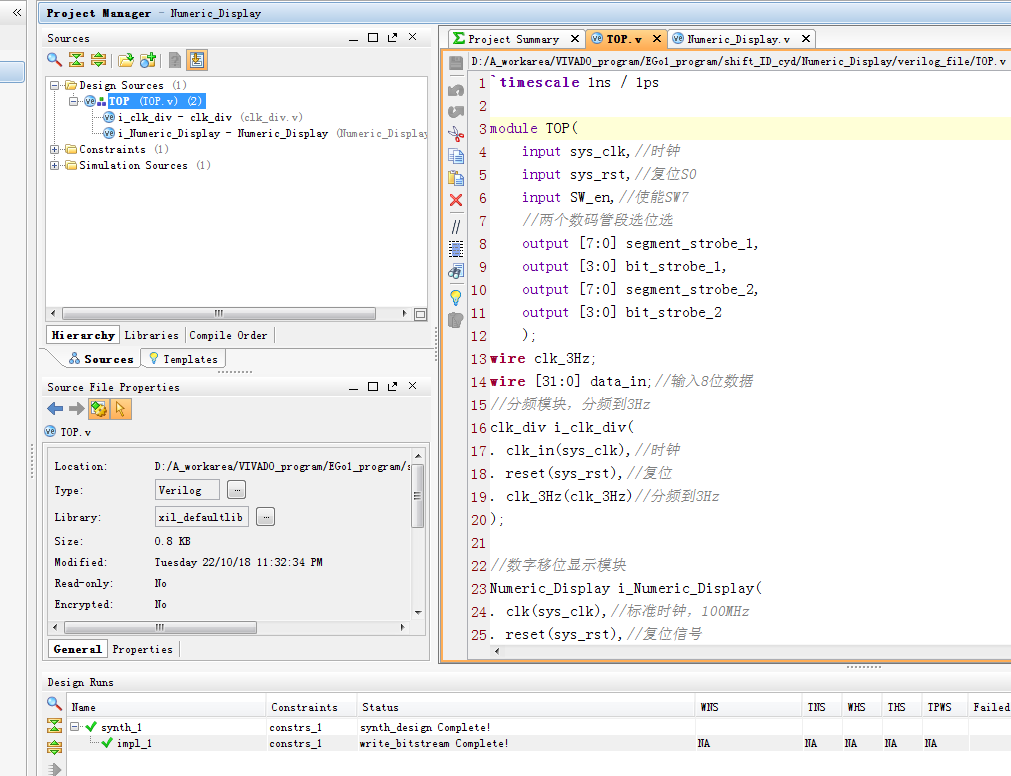

工程文件:

程序文件:

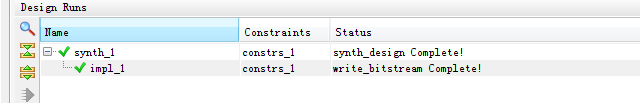

程序编译:

RTL图:

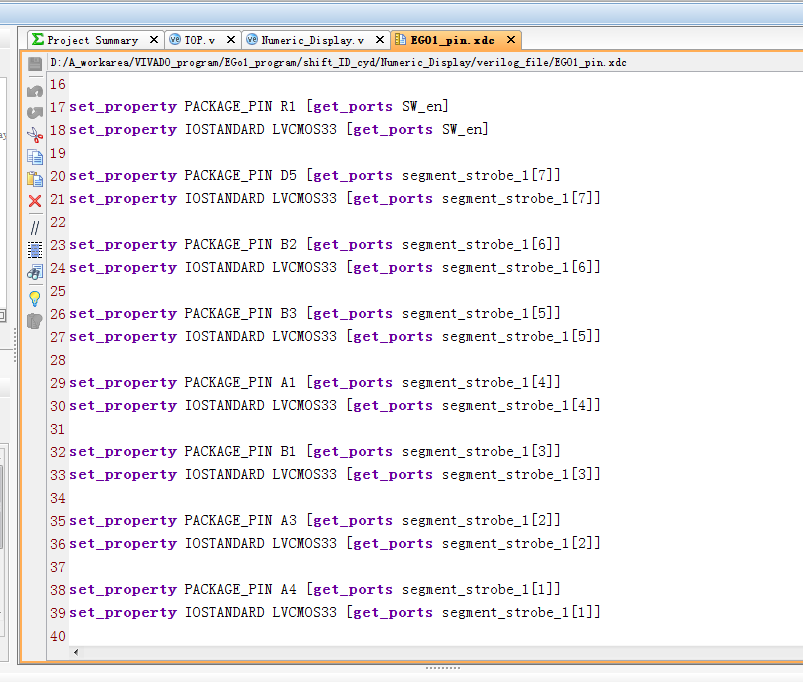

管脚分配:

部分代码展示:

`timescale 1ns / 1ps module TOP( input sys_clk,//时钟 input sys_rst,//复位S0 input SW_en,//使能SW7 //两个数码管段选位选 output [7:0] segment_strobe_1, output [3:0] bit_strobe_1, output [7:0] segment_strobe_2, output [3:0] bit_strobe_2 ); wire clk_3Hz; wire [31:0] data_in;//输入8位数据 //分频模块,分频到3Hz clk_div i_clk_div( . clk_in(sys_clk),//时钟 . reset(sys_rst),//复位 . clk_3Hz(clk_3Hz)//分频到3Hz ); //数字移位显示模块 Numeric_Display i_Numeric_Display( . clk(sys_clk),//标准时钟,100MHz . reset(sys_rst),//复位信号 . SW_en(SW_en),//使能 . shift_key_p(clk_3Hz),//移位信号 . segment_strobe_1(segment_strobe_1), . bit_strobe_1(bit_strobe_1), . segment_strobe_2(segment_strobe_2), . bit_strobe_2(bit_strobe_2)//高电平点亮,高电平选通 ); endmodule