基于数电的电子秒表

题 目: 基于数电的电子秒表

专 业: 物联网工程

姓 名: xh 学 号: 88143331

指导教师:nmy 职 称:

填写日期: 2018年5月28日

毕业设计(论文)题目 基于数电的电子秒表

学生承诺

1.本人在毕业设计(论文)撰写过程中严格遵守学院有关规定,恪守学术规范,所呈交的毕业设计(论文)是在指导教师的指导下独立完成;

2. 毕业设计(论文)所使用的相关资料、数据、观点等均真实可靠,文中所有引用的他人观点、材料、数据、图表均已注释说明来源;

3.毕业设计(论文)中无抄袭、剽窃或不正当引用他人学术观点、思想和学术成果,伪造、篡改数据的情况;

4.本人已被告知并明白,学院对毕业设计(论文)中的抄袭、剽窃、弄虚作假等违反学术规范的行为将严肃处理,并可能导致毕业设计(论文)成绩不合格,无法正常毕业、取消学士学位资格或注销并追回已发放的毕业证书、学士学位证书等严重后果;

5.若在省教育厅、学院组织的毕业论文(设计)检查、评比中,被发现有抄袭、剽窃、弄虚作假等违反学术规范的行为,本人愿意接受按学院有关规定给予的处理,并承担相应责任。

学生(签名):

2018年 5月 14日

摘要

本文主要设计一个机械秒表,要求最大计数为59:59:99,通过使用555定时器设计一个频率为100HZ的脉冲作为基准信号,并且使用一个一百进制计数器和两个六十进制计数器共同完成,对于本次实验,我运用proteous仿真软件作为仿真工具。该秒表具有计时准确、性能稳定、设计结构灵活、方便进行多功能组合、经济适用、成本低廉的优势。

关键字: 一百进制计数器 六十进制计数器 多谐振荡器 555定时器 proteous仿真

Abstract

This article mainly designs a mechanical stopwatch, which requires a maximum count of 59:59:99. By using the 555 timer, a pulse with a frequency of 100HZ is designed as the reference signal, and a one-hundred-base counter and two hexadecimal counters are used together. Complete, for this experiment, I use proteous simulation software as a simulation tool. The stopwatch has the advantages of accurate timing, stable performance, flexible design structure, convenient multifunctional combination, economical application, and low cost.

Keyword: One hundred base addition counter、Hexadecimal addition counter、Multivibrator、555Timer、proteous simulation

目录

摘 要 I

Abstract II

第一章 绪论 1

1.1 研究目的 1

1.2 研究意义 1

1.3 设计要求 1

第二章 电路总设计 3

2.1 实验方案与比较分析 3

2.2 时钟发生及控制信号 4

2.3 设计100进制加法计数器 5

2.4 设计60进制加法计数器 6

2.5 设计两秒倒计时电路 7

2.6 设计秒信号的输出电路 8

2.7 总原理图 9

第三章 元器件的介绍 10

3.1 七段数码管及其工作原理 10

3.1.1 数码管的介绍 10

3.1.2 数码管的驱动cd4511 11

3.2 74LS192 13

3.3 74LS04 14

3.4 74LS08 15

3.5 74LS32 16

3.6 555定时器 17

第四章 仿真及实际电路展示 20

4.1 仿真及实物运行过程记录 20

第五章 本文总结 24

参考文献 24

致谢 25

附录 26

第一章 绪论

1.1研究目的

1.以便能够广泛地把数字式电子秒表运用到生活和工作当中;

2.学习电子秒表的调试方法及过程;

3.学习数字电路中显示译码器、计数器、多谐振荡器等这些单元电路的综合应用。

1.2 研究意义

数字式电子秒表在现代化发展的过程中是一种相对准确的计数器,它的性能稳定,设计结构灵活。当前,中国的电子秒表设计基本是由石英振荡器组成的振荡频率为时间基准的电子秒表,采用6位数码显示器。本设计中电子秒表所能够容纳的最大数值为59:59:99,555定时器组成的多谐振荡器可以产生频率为100Hz的时钟脉冲信号。由于电子秒表能准确的记录时间,所以电子秒表的应用也很广泛,尤其是时代快速发展今天,电子秒表使用方便,方便进行计数及显示的,经济实用,成本低廉。

1.3设计要求

为了完成该设计,我翻阅了大量相关资料,积极和同学以及老师进行探讨,吸取资料中精华的部分,认真听从同学和老师的建议。研究设计具体要求包含以下几方面:

(1)设计一个秒表,显示格式00:00 00,最后00为00到99,

(2)中间的00为00到59,最前面的00为00到59,

(3)该秒表使用一个按钮K工作,

(4)当第一次按下按钮时,秒表开始计数;

(5)当第二次按下按钮时,秒表停止计数;

(6)当第三次按下按钮时,秒表计数器继续计数;

(7)当第四次按下按钮时,秒表停止计数,如此反复。

(8)若该定时器处在停止计数状态的情况下,此时按下开关并保持开的按下时间(不松开开关)超出2s,则此秒表计数器的所有显示器全部呈现清零的状态。

第二章 电路总设计

2.1 实验方案与比较分析

根据老师所给的题目要求,本设计中电子秒表所能够容纳的最大数值为59:59:99,即需要两个60进制加法计数器和一个100进制加法计数器,除此以外还需要用到六个数码管来显示时间,同时我选择了七段共阴极数码管并选择用译码器cd4511对其进行驱动。为了此次计数分辨率达到0.01s,信号源也是不可或缺的,但是信号源须满足相应的频率要求。

对于信号源,我设计了两种方案:第一种可用的方案是运用555定时器与满足电路要求的相应参数的电阻R及电容C可以组成一个多谐振荡器,该多谐振荡器可以为整个电路提供一个方波信号。第二种可以实行的方案是运用到一个晶体振荡器也可以为整个电路供应所需要的脉冲电源。通过分析发现由555定时器组成的多谐振荡器性能比较稳定,效率也相对较高,因此在本次的设计中决定采用第一种实验方案。

该数字式电子秒表需要实现不同种类的功能,为了实现这些功能,电路中加上控制信号也显得格外重要,也使得电路的功能更加的多样化,加上控制电路后该电路则可以实现相应的功能:从初始状态启动计时、暂停计时状态、从暂停计时的状态下继续计时下去、在暂停状态下保持按下开关的时间超过2s计时器则开始清零等。所以,100Hz的时间信号必须既能稳定又是精确的。

七段数码管

图2-1 方案设计思路图

上图2-1是我对此次毕业设计的大致设计思路。由图可以见,该电子秒表的组成部分有以下的几部分来组成的:七段共阴极数码管;提供方波信号的多谐振荡器;开关;60进制加法计数器、100进制加法计数器、控制电路。

在此次实验中,七段数码管选用共阴极并用译码器cd4511对其进行驱动,计数器选用74ls192,通过查阅相关的资料了解到通过十进制加法可逆计数器74ls192之间的通过相应的连接可以分别组成满足我的实验中所需要用到的的六十进制加法计数器和一百进制的加法计数器,一个555定时器及相关电阻和电容组成的提供方波信号的多谐振荡器,74ls192同门电路的不同组合形成一个按下两秒计时电路,通过四个74ls192的组合输出秒的信号从而满足电路的要求。通过对555定时器功能的查阅可知由555定时器组成的多谐振荡器可以产生频率为100Hz的时钟脉冲信号,时钟脉冲为整个电路来提供方波信号,满足电子秒表计时的操作。通过控制的输出与非门后作为信号源输入,将信号源输入到第一个10进制计数器。后来进位至0.1s,紧接着继续朝下一位执行进位操作,通过这种循环往复的实验操作从而可以实现相应种类的计数功能。由于在此实验中需要用到六位数码管显示器,显示时间从00:00:00到59:59:99。

2.2 时钟发生及控制信号

由定时器555与相应参数的电容和电阻的组合组成的多谐振荡器作为信号源产生矩形的脉冲:

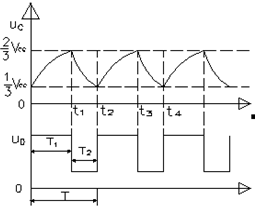

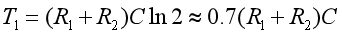

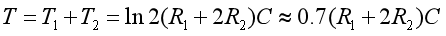

暂稳态的脉冲宽度为tp1,此时对Vc进行充电,Vc的初始状态为(1/3)Vcc,进行充电之后Vc上升到了(2/3)Vcc,根据查阅到的公式可以求出Vc从(1/3)Vcc上升到(2/3)Vcc变化过程所需要经过的时间tp1:

(2-1) 脉冲宽度tp2,Vc的初始状态又变成(2/3)Vcc,此刻对Vc进行放电然下降到(1/3)Vcc,根据公式可以求出整个放电过程所需的时间tp2 :

(2-2)

振荡周期的计算一般即为Vc的充电与放电这两个过程中时间的总和T:

(2-3)

该多谐振荡器由频率为100Hz的555定时器构成。从3脚(OUT端)输出频率为100Hz的脉冲方波信号。

图2-2 由定时器555集成电路构成的多谐振荡器

图2-3 多谐振荡器的工作波形图

2.3 设计100进制加法计数器

使用两个74LS192芯片之间的连接实现形成100进制加法计数器:即用两个10进制加法计数器进行组合。

若要使74LS192处于一个计数状态时,则需要满足74ls192中的两个引脚满足TCU=1,TCD=0时,因为此时只需要用到进位状态不需要借位。此刻该电路会从0000状态作为起始并开始计时,最终能够到达1001。通过信号的不断输入,此刻的电路状态将从1001状态通过信号的跳变返回至0000的初始状态,紧接着端口RCO也从高电平状态往低电平状态转换。因此该电路技术过程中的进位输出信号可以通过对RCO端输出的高电平或下降沿的跳变来实现。

图2-4 100进制加法计数器

由于该电子秒表仅包含计时的功能从而只需考虑进位端即可,即借位端可置空,该电路也与输入信号无关因此输入信号D0、D1、D2、D3都接地即可。输出端Q0、Q1、Q2、Q3与译码器cd4511的输入端相连接。图2-3所示是两个十进制的可逆加法计数器,本次实验所需的100进制的加法计数器就可以通过两个十进制加计数器组合而成,电路之间不同的连接可以形成不同进制的计数器。

2.4 设计60进制加法计数器

由于74ls192是一个十进制计数器,通过几个74ls192之间不同线路的连接可以组成相应进制的计数器,电路之间的连接取决于题目中要求的进制数。如果要设计一个六十进制加法计数器可以通过将一个十进制加法计数器与一个六进制加法计数器进行连接与组合形成一个该实验需要的六十进制加法计数器,由于用74ls192实现十进制加法计数器的原理2.2中已进行详细说明过,此处不再进行相关重复的论述。

设计六进制加法计数器:

由于计数器74ls192的计数初始状态是从0000开始的,如果要求通过74ls192之间的操作设计出一个六进制加法计数器,即只需要输出满足Q3Q2Q1Q0=0110即可以了,即需要当输入到第6个CP 脉冲(上升沿)时,Q3Q0端通过清零端MR给出一个清零的号,一旦MR端给出清零信号之后,即电路将开始进行清零操作,四个输出信号Q3Q2Q1Q0可以立即返回0000状态即Q3Q2Q1Q0=0000,输出信号都为0之后,MR端口的清零信号也会逐渐消失,此刻的计数器74ls192则继续再一次从0000状态开始又一轮新的计数周期

图2-5 60进制加法计数器

将输出口Q1和Q2相与非后连接到加法计数端从而形成六进制加法计数器,图2-3右半边表示10进制加法计数器,两者通过电路连接从而可以形成一个60进制的加法计数器。

2.5 设计两秒倒计时电路

图2-6 两秒倒计时电路

该两秒倒计时电路由两个74ls192及若干与门,非门及或门组合而成。当计数器处于暂停计数状态时,此时按下按钮K图2-5电路开始启动进行两秒倒计时的状态,此时有两种情况发生,第一种情况是未到达两秒的情况,第二种情况是倒计时超过或恰巧等于两秒的情况。

2.6 设计秒信号输出的电路

在暂停计数状态下,当按下时间未到达两秒的时候,输出的秒信号为暂停计数状态下的时间。

在暂停技术状态下,当按下时间超过两秒或者恰巧等于两秒状态时,输出秒信号为全部清零状态。

图2-7 输出秒信号电路图

2.7总原理图

图2-8 总原理图

第三章 元器件的介绍

3.1 数码管

3.1.1七段数码管的工作原理

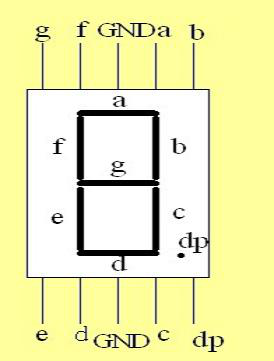

在这个实验中我选择使用共阴极七段数码管来显示计数结果,每个共阴极七段数码管均有七个发光段,即a.b.c.d.e.f.g(共阴极)

图3-2 七段数码管引脚图

BCD码 显示数码 发光管 BCD码 显示数码 发光管

0000 abcdef 0101 acdfg

0001 bc 0110 cdefg

0010 abdeg 0111 abc

0011 abcdg 1000 abcdefg

0100 bcfg 1001 abcfg

表3-1 BCD码与显示发光管的对应关

数码管发光原理与运用方面介绍:七段数码管通过对8个显示引脚及一个Vcc、接地端输入相对应的需要的电流信号,从而使对应段发亮,最终使得能够显示出需要的数字。由于一个数码管的价格十分便宜,使用方面也十分简单便捷,因此在日常生活中,我们经常能看到数码管的存在,它无论是在时间、日期、红绿灯等等这些所有可以用数字表示的方面应用及其广泛,可以说说生活中少了它将失去很多色彩。

3.1.2七段显示译码器

对于数码管的驱动,使用的是七段显示译码器,本文选择使用的是CD4511。

CD4511的介绍:CD4511 是一个7位BCD码译码器,它的作用是能够用来驱动一个共阴极的数码管显示器,但需要注意的是cd4511不能驱动共阳极的数码管,因此在驱动数码管之前需要确认一下一下。译码器CD4511能实现的功能是电路能提供较大的电流,从而具有BCD译码转换、信息锁存和对信息实现消隐控制。

图3-3 译码器CD4511的引脚图

CD4511引脚功能介绍:

A1、A2、A3、A4分别对应8421BCD码的4个输入端,在此要注意输入的顺序应为A4A3A2A1,不能将先后顺序搞混。

a、b、c、d、e、f、g分别对应表示BCD译码器中的7个的输出端,不同的段码启动可以有不同的效果只有当输出为高电平1时才能代表该输出是有效的。

LT:表示测试端,主要能够用来检测数码管是否完好。具体的检测过程为:将LT设为低电平即设0 ,将BI端设为高电平即设1 时,若此时BCD译码器的7个输出端口全部显示为1,且此刻 A4A3A2A1端不论输入什么,七段数码管的每一个段码均处于发亮的状态,即此时的数码管一直显示数字“8”,则说明该数码管是完好的,不存在任何的损坏问题。

BI:表示消隐控制端。当端口BI设为低电平时,不论4个输入端A4A3A2A1输入的是什么,七段数码管的显示受到阻碍,不会受到任何输入的影响,即此刻输出端的每一个段码均处于熄灭状态。

LE:表示锁定控制端,即此时的输出是可以锁存的。当把锁定控制端LE设为低电平时,即设为0时,译码器的输出是允许进行的。当锁定控制端LE设为高电平时,7位BCD译码器则处于数据被锁定的状态,即此刻的译码器的输出结果为前一次的LE=0时对应所显示的数值,不再输出新的数值。

输 入 输 出

LE BI LI D C B A a b c d e f g 显示

X X 0 X X X X 1 1 1 1 1 1 1 8

X 0 1 X X X X 0 0 0 0 0 0 0 消隐

0 1 1 0 0 0 0 1 1 1 1 1 1 0 0

0 1 1 0 0 0 1 0 1 1 0 0 0 0 1

0 1 1 0 0 1 0 1 1 0 1 1 0 1 2

0 1 1 0 0 1 1 1 1 1 1 0 0 1 3

0 1 1 0 1 0 0 0 1 1 0 0 1 1 4

0 1 1 0 1 0 1 1 0 1 1 0 1 1 5

0 1 1 0 1 1 0 0 0 1 1 1 1 1 6

0 1 1 0 1 1 1 1 1 1 0 0 0 0 7

0 1 1 1 0 0 0 1 1 1 1 1 1 1 8

0 1 1 1 0 0 1 1 1 1 0 0 1 1 9

0 1 1 1 0 1 0 0 0 0 0 0 0 0 消隐

0 1 1 1 0 1 1 0 0 0 0 0 0 0 消隐

0 1 1 1 1 0 0 0 0 0 0 0 0 0 消隐

0 1 1 1 1 0 1 0 0 0 0 0 0 0 消隐

0 1 1 1 1 1 0 0 0 0 0 0 0 0 消隐

0 1 1 1 1 1 1 0 0 0 0 0 0 消隐

1 1 1 X X X X 锁 存 锁存

表3-2 CD4511的真值表

3.2 74LS192

74LS192是一个能够同步计数的十进制的加法可逆计数器。74ls192的功能比较多样,它不仅支持双时钟输入的功能,而且能够实现数据的清除以及对数据进行置数的功能。PL端表示置数的端口,当PL端设为低电平时,代表可以进行置数。CPU端表示加计数时钟输入端,当CPU端设为高电平时,代表可以进行加计数。CPD端表示减计数时钟输入端,当CPD设为高电平时,代表允许进行减计数。TCU端表示非同步进位的输出端口,即需要进行进位时则该端连通,此刻1001状态后实现负脉冲输出。TCD端表示非同步借位输出端口,即需要实现借位的功能时该端连通即可,此刻0000状态后实现负脉冲输出。数据输入端分别为P0、P1、P2、P3,输入端可以输入相应数据,也可以接地代表无输入状态,数据输出端为 Q0、Q1、Q2、Q3为数据输出端,不一定输出端一定要有结果,也可以无输出状态。MR端表示复位输入端,高电平有效即进行清零。

图3-4 74ls192引脚及仿真图

输入 输出

MR PL CPU CPD P3 P2 P1 P0 Q3 Q2 Q1 Q0

1 × × × × × × × 0 0 0 0

0 0 × × d c b a d c b a

0 1 1 × × × × 加计数

0 1 1 × × × × 减计数

表3-3 74ls192真值表

3.3 74LS04介绍

74ls04是一个反相器,有六个输入端口和六个输出端口组成,即每一个74ls192内都带有6个非门,每一个反相器的输入端与输出端相位均相反。一个74ls04中有六个反相器,其中的Vcc端和地端是公用的,但除了这两个端口以外其它端口之间都是互相独立的。反相器实现的功能是将输入信号往对立面进行输出,即把0变成1,1变成0。这种芯片在数字电路与模拟电路中的应用极为广泛。在我们的生活中反相器打多用于开关的设置。此外,74ls04的工作电压5V。

74ls04引脚图:

图3-5 74ls04引脚图

输入 输出

A B Y

L

L

H

H L

H

L

H L

L

L

H

表3-4 74ls04真值表

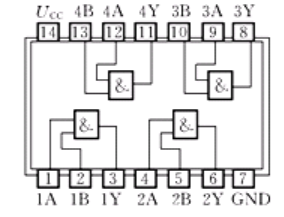

3.4 74LS08

74LS08是一个与门电路芯片,每一个与门包含两个输入端和一个输出端,在一个74ls08中包含有4个与门,此外端口共用Vcc端和地端,其余端口之间相互独立,该电路芯片在各种功能的数字电路系统中的应用较为广泛。

图3-6 74ls08引脚图

输入 输出

A B Y

L

L

H

H L

H

L

H L

L

L

H

表3-5 74ls08真值表

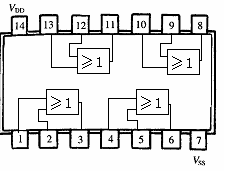

3.5 74LS32

74LS32表示的是一个或门的电路集成芯片,每一组或门当中都要有包含有两个输入端和一个输出端,在一个74ls32芯片中包含有4组这样的或门,且每个端口都共用电源正极Vcc端及地端(GND),其余端口之间相互独立,通常用在各种数字电路以及单片机的应用系统中。

图3-7 74ls32引脚图

输入 输出

A B Y

0 0 0

0 1 1

1 0 1

1 1 1

表3-6 74LS32真值表

3.6 555定时器

由于起初的555集成电路普遍是用作定时器来使用的,因此555集成电路也可以叫做555定时器。后来经过不断发展与更新,555定时器不仅能够作为定时器的延时控制,而且它还可以进行多种的控制及很多检测等方面都有广泛的应用。除了这些应用之外,方波脉冲振荡电路、单稳态及双稳态电路及脉冲调制电路均可用555定时器来实现。由于555定时器的工作原理简单、使用便捷且价格比较低廉,因此在各式各样的电子产品中通常被广泛应用。

555定时器具有以下的几个特点:

(1)555定时器,既可以用在数字电路中同时也可以用在模拟电路中。

(2)555定时器采用的是4.5~16V的电源,一般在使用过程中给5V信号即可,同时555定时器也可以和其它不同种类的运算放大器共用电源;

(3)每一个555集成电路,可以提供一个较为准确地计时时间,持续时间约为15min。

(4)由于555定时器具有一定的输出功率,因此它的输出功率可以对小型负载进行直接驱动,且每一个555定时器并不是能承受任何电流的,能承受的最大输出电流为200mA。

各引脚功能如下:

1脚接电源地端,即电源的负极(GND);

2脚为低电位触发端,简称低触发端(TR);

3脚为输出端,将它与有负载的一端进行连接,另一端接地或接Vcc端(OUT);

4脚为低电位复位端(RESET);

5脚为电压的控制端,主要用来调节比较器的触发电压(CV);

6脚为高电位触发端,简称为高触发端(TH);

7脚为放电端(DIS);

8脚接电源正极(Vcc)。

通过对555定时器与相应参数的电阻及电容就可以组成各种样式的多谐振荡器,如图3-8所示。当电路的电源刚接通时,由于电容C未来得及充电,定时器555电路的2脚处于低电平状态,最终导致输出3脚呈现高电平状态。当电源向电容C充电时,当达到Vc≥Vcc时,3号输出端口则由高电平状态往低电平状态发生转变,然后电容C经电阻R2和内部电路又实现放电的过程。当Vc≤Vcc时,说明此时电容又开始处于放电的过程,此时3号输出端口又由低电平状态转变为高电平状态。发生跳变之后电容C又处于再次充电的状态,在这种过程中将电平的跳变周而复始地循环进行下去,通过这种循环,从而形成了自激振荡的过程。图3-9中给出了输出端3脚和电容C上所呈现的电压的波形。

图3-8 555定时器基本电路组成 图3-9 电压波形图

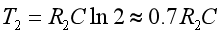

充电时间过程:

(3-1)

放电时间过程:

(3-2)

方形波的振荡周期:

(3-3)

通过对电阻、和电容C的数值的改变,从而可以实现对矩形波的频率和周期的改变.

第四章 仿真及实际电路展示

4.1 仿真及实物运行过程记录

按照上面的总电路图建立仿真电路,点击按钮,下面的图就是仿真的输出结果。

图4-1 运行初始状态

运行之后,按下开关,仿真的电子秒表呈现开始计时状态,再次按下开关之后,处于计时暂停状态,暂停状态如下图4-2.

图4-2 计时暂停状态

图4-3 实物图正面

图4-4 实物图反面

将+5V电源及地端接入电路板对应引脚后电路板显示的初始状态如下图4-5

4-5 实物运行初始状态

接入电源及GND端后,按下开关,计时器将处于开始计时状态,再次按下开关之后计时器处于计时暂停状态,暂停状态如下图4-6所示: ,

,

图4-6 计时暂停状态

在暂停计数的状态下,长按开关超过2s之后,计时器处于清零状态,清零状态如下图4-7所示:

图4-7 计时清零状态

第五章 本文总结

经过一个多月的学习与实践,我终于完成了论文。从开始确定论文题目到实验的完成,再到论文文章的完成,这个过程对我充满了未知和挑战,也是我在大学期间独立完成的最大的项目。在这段时间里,我学到了很多知识和经验,开始了独立的学习和探索,通过查看相关的资料和书籍,让自己头脑中对这个毕设的整体有了个大概思路,每一次的进步都是我前进的动力。我的论文题目是基于数电的电子秒表,通过学习和研究我知道了一些芯片的原理与应用,知道了芯片之间紧密的联系。也让我学习了对待工作那种严谨的态度,假若焊接途中有一个引脚的连接出现差错都有可能影响最后的结果。对待生活也是一样,一步一步脚踏实地,终能走到彼岸。

参考文献

[1]康华光,电子技术基础 数字部分(第六版)高等教育出版社,2013

[2]沈尚贤,电子技术导论(上),北京:高等教育出版社,1985

[3]彭容修,数字电子技术基础,武汉:华中理工大学出版社,2000

[4]阎石,数字电子技术基础(第五版),北京:高等教育出版社,2006

[5]William Keith.数字电子技术[M]陶国彬,赵玉峰译。北京:科学出版社,2008

[6]李士雄,丁康源,数字电子集成技术教程[M],北京,高等教育出版社,1993

[7]瞿安连.应用电子技术[M].北京:科学出版社,2003

[8]李哲英.电子技术及应用基础(数字部分)[M].2版.北京:高等教育出版社,2009

[9]蔡惟铮.基础电子技术[M].北京:高等教育出版社,2004

[10]王小海.集成电子技术基础教程(下)[M].2版.北京:高等教育出版社,2008

[11]王金明.数字系统设计[M].2版,北京:高等教育出版社,2009

[12]初秀琴.基于FPGA的嵌入式系统设计[M].西安:西安电子科技大学出版社,2004

[13] 薛文.华慧明编著:《新编实用电子技术快速入门》,福州,福建科学技术出版社,1999.9

[14]贾立新 著 :数字电路(第2版)电子工业出版社2011.8

[15] 刘勇 编著:数字电路(第4版).电子工业出版社 2012.2

致谢

光阴似箭,大学生活转瞬即逝,很快就迎来了毕业的时刻。在这里我要感谢我的学校给予我好的学习环境,感谢我的父母生我养我以及老师和同学们的帮助,感谢你们在我大学这几年的时间里对我的关心、帮助和支持。我要感谢我的父母给我提供了良好的家庭环境并给予我学习的机会,从小到大能够无条件的包容我一些不成熟的举动,总是给我最暖心、最坚实的依靠。

首先,在此我要深深的感谢我的论文指导老师聂梦雅老师,此篇论文是在聂梦雅老师的精心指导下,在周围人们的热情帮助和支持下完成的。真的非常感激聂梦雅老师的孜孜教诲,她知识渊博,拥有刻苦钻研的精神,深深感染了我,对我们的要求也很严格,让我们不敢有一丝懈怠,做这次毕设也让我学到了很多知识,对以往学过的知识从纸面上升到了实践。当我对毕业论文感到迷茫的时候,是老师在百忙之中挤出时间来与我交流、讨论,不厌其烦的指点我,最后我才有了明确的方向,确定了毕业设计的思路,并确立了明确的学习目标。在整个毕业设计中无论从选题到论文提纲确定,包括开题报告的填写,论文的中期检查以及论文格式、语病等一些问题上面,老师都耐心的给我提出许多中肯的指导意见,在整个论文的环节中是老师给予了我深深的教诲和帮助。

其次,我还要深深的感谢在校期间所有帮助过我的老师,是你们无私的教导我才能学习到更多的专业知识并且最后顺利的完成毕业论文。你们大学期间以来的认真教导使我学习到不少的知识,除了课本中的专业知识以外还包括将来在社会所要学习的,这些知识对我以后的生活和工作都有着极大的帮助。最后,感谢大学几年来一直陪伴在我身边的朋友和同学们,非常谢谢你们一直以来对我的关心和帮助。非常感谢四年来教予我知识的各位老师,感谢四年以来所有关心帮助过我的同学、老师和学校,在以后的学习生活中我将以加倍的努力来回报那些给予我帮助的人。毕业在即,让我能运用自己学过的知识编写出此篇论文,让我感受到了知识的魅力。当我在学习和生活中感到困惑和迷茫时,谢谢你们能够放下手头的事情认真的听我倾述,并且积极开导我、鼓励我,是你们给了我精神上的动力。正因为有了你们,我的人生道路上才更加的多姿多彩。

最后我想感谢我的家人,谢谢你们一直以来对我的信任,没有我的家人对我的支持与付出,我就很难有今天的进步与成长。

附录

元件序号 型号 主要参数 数量 备注

1 555定时器 T,RC 1

2 CD4511 6

3 74LS192 12

4 LED共阴极数码管 6

5 电阻 R 10 100Ω,47kΩ

6 电容 C 3 1nF,10nF,100nF

7 74LS08 8

8 74LS04 5

9 74LS32 2

10 开关 1

表5-1 元器件使用清单