名称:4人竞赛数字抢答器vivado软件verilog代码ego1开发板

软件:VIVADO

语言:Verilog

代码功能:

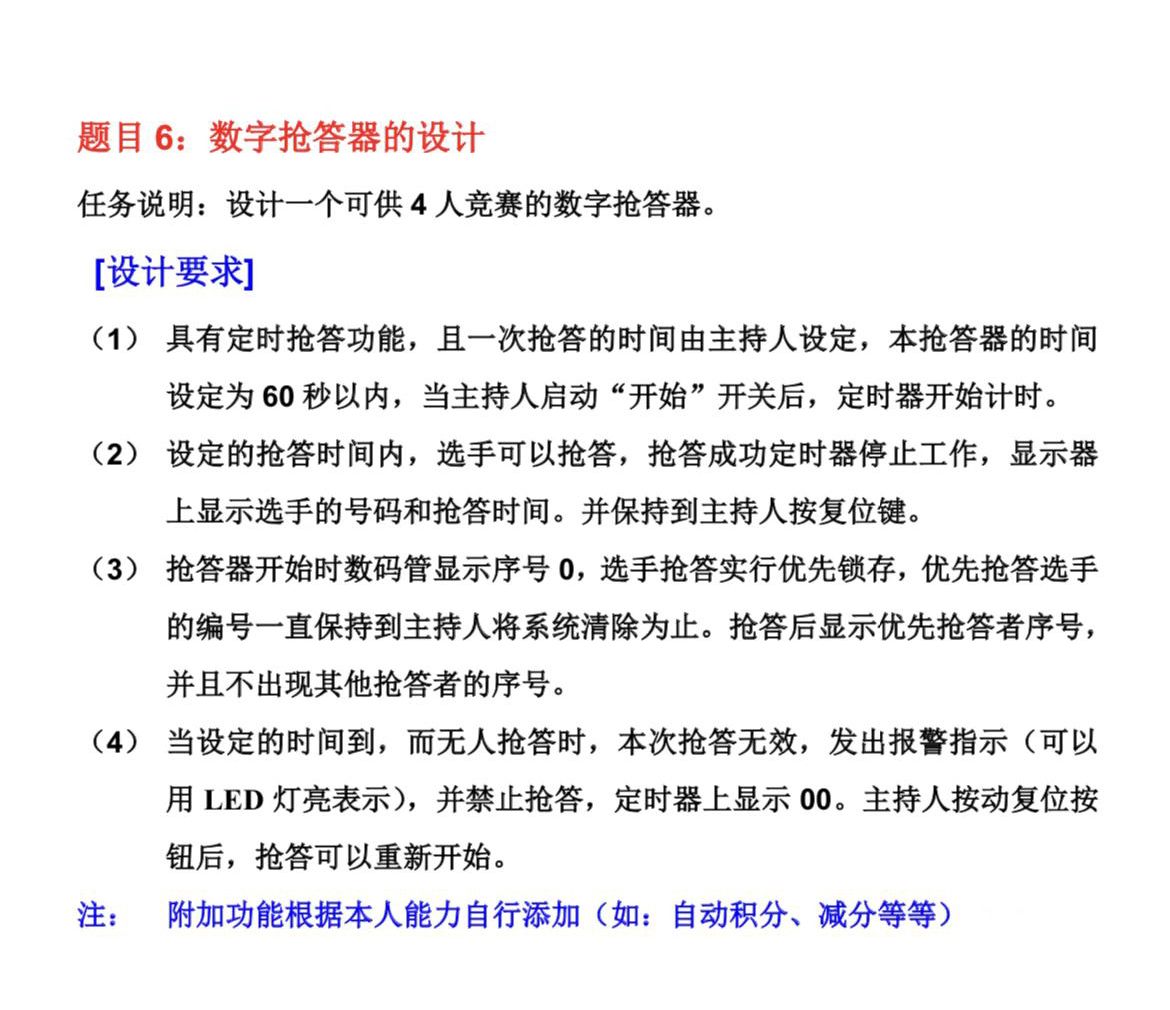

数字抢答器的设计任务说明:

设计一个可供4人竞赛的数字抢答器。

(1)具有定时抢答功能,且一次抢答的时间由主持人设定,本抢答器的时间 设定为60秒以内,当主持人启动“开始”开关后,定时器开始计时。

(2)设定的抢答时间内,选手可以抢答,抢答成功定时器停止工作,显示器上显示选手的号码和抢答时间。并保持到主持人按复位键

(3)抢答器开始时数码管显示序号0,选手抢答实行优先锁存,优先抢答选手 的编号一直保持到主持人将系统清除为止。抢答后显示优先抢答者序号,并且不出现其他抢答者的序号。 (4)当设定的时间到,而无人抢答时,本次抢答无效,发出报警指示(可以 用LED灯亮表示),并禁止抢答,定时器上显示00。主持人按动复位按 钮后,抢答可以重新开始。

注:附加功能根据本人能力自行添加(如:自动积分、减分等等)

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

本代码已在ego1开发板验证,开发板如下,其他开发板可以修改管脚适配:

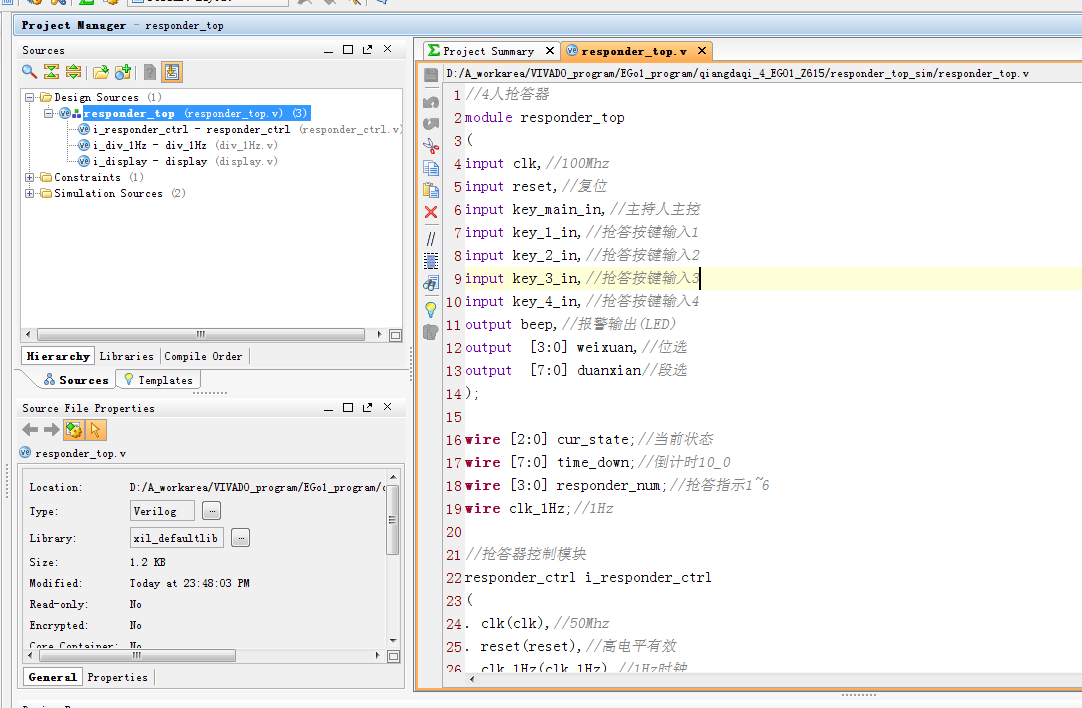

1. 工程文件

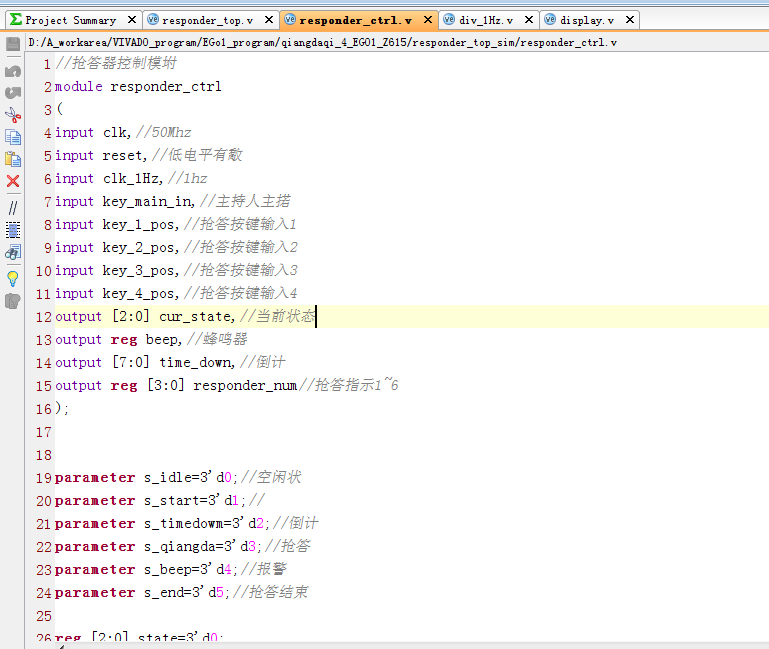

2. 程序文件

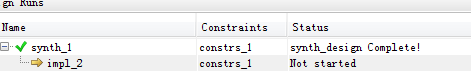

3. 程序编译

4. RTL图

5. 管脚分配

6. Testbench

7. 仿真图

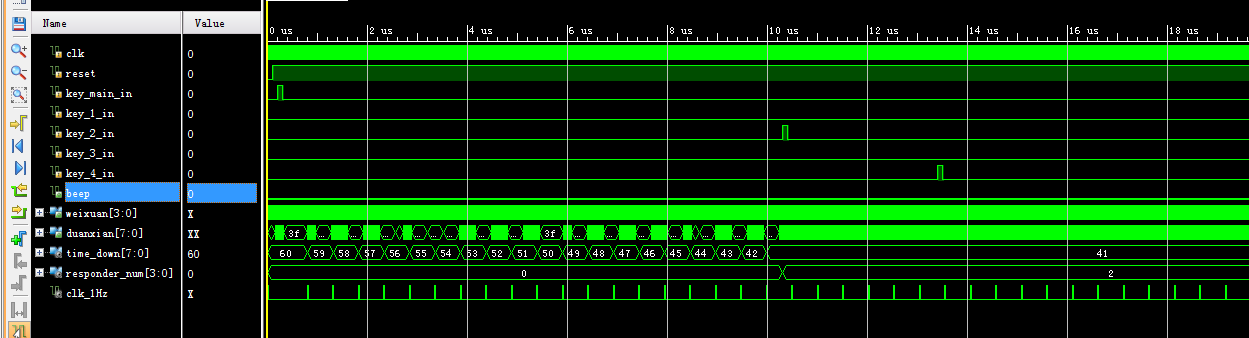

整体仿真图

分频模块

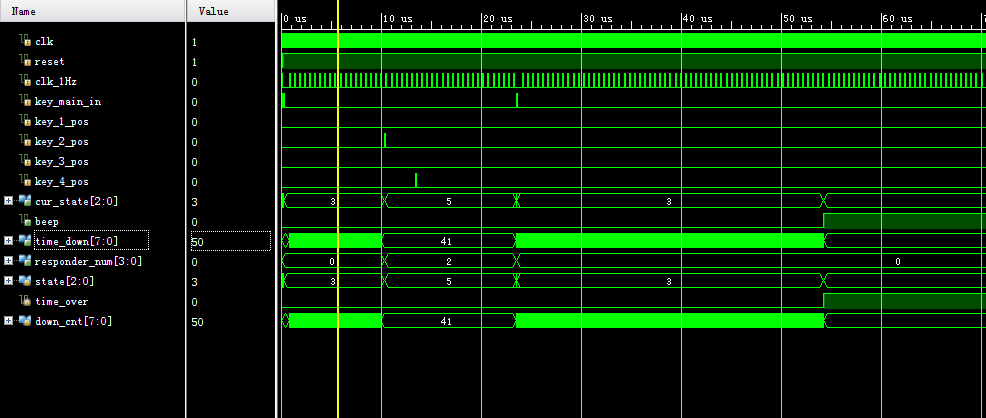

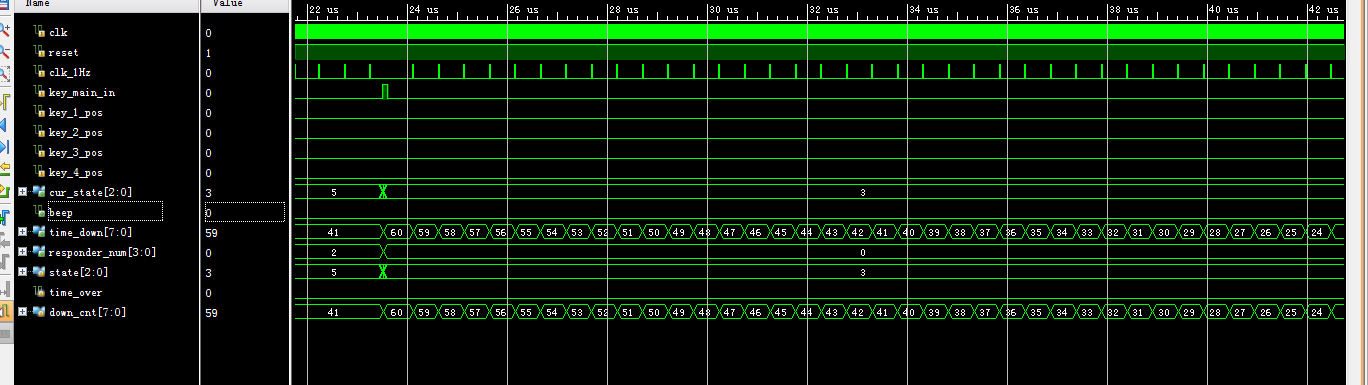

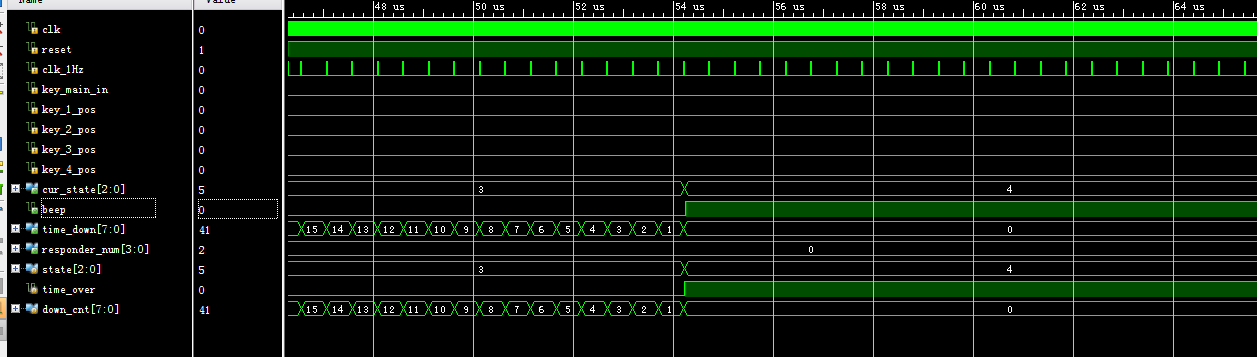

抢答器控制模块

数码管显示模块

部分代码展示:

//4人抢答器 module responder_top ( input clk,//100Mhz input reset,//复位 input key_main_in,//主持人主控S0 input key_1_in,//抢答按键输入1 input key_2_in,//抢答按键输入2 input key_3_in,//抢答按键输入3 input key_4_in,//抢答按键输入4 output beep,//报警输出(LED) output [3:0] weixuan,//位选 output [7:0] duanxian//段选 ); wire [2:0] cur_state;//当前状态 wire [7:0] time_down;//倒计时10_0 wire [3:0] responder_num;//抢答指示1~6 wire clk_1Hz;//1Hz //抢答器控制模块 responder_ctrl i_responder_ctrl ( . clk(clk),//50Mhz . reset(reset),//高电平有效 . clk_1Hz(clk_1Hz),//1Hz时钟 . key_main_in(key_main_in),//主持人主控 . key_1_pos(key_1_in),//抢答按键输入1 . key_2_pos(key_2_in),//抢答按键输入2 . key_3_pos(key_3_in),//抢答按键输入3 . key_4_pos(key_4_in),//抢答按键输入4 . beep(beep),//蜂鸣器输出 . time_down(time_down),//倒计时 . cur_state(cur_state), . responder_num(responder_num)//抢答指示1~6 ); //分频模块 div_1Hz i_div_1Hz ( . clk(clk),//50M . reset(key_main_in),//复位 . clk_1Hz(clk_1Hz)//1Hz时钟 ); //数码管显示模块 display i_display ( . clk(clk), . time_down(time_down),//倒计时10_0 . responder_num(responder_num),//抢答指示1~6 . weixuan(weixuan),//位选,高电平亮 . duanxian(duanxian)//段选,高电平亮 ); endmodule