HDLBits: 在线学习 SystemVerilog(二十三)-Problem 158-162(找BUG)

HDLBits 是一组小型电路设计习题集,使用 Verilog/SystemVerilog 硬件描述语言 (HDL) 练习数字硬件设计~

网址如下:

https://hdlbits.01xz.net/

关于HDLBits的Verilog实现可以查看下面专栏:

https://www.zhihu.com/column/c_1131528588117385216

缩略词索引:

SV:SystemVerilog

从今天开始新的一章-时序电路,包括触发器、计数器、移位寄存器、状态机等。

Finding bugs in code 这一节中,将找出给的电路中的bug,有一双找bug的眼睛。

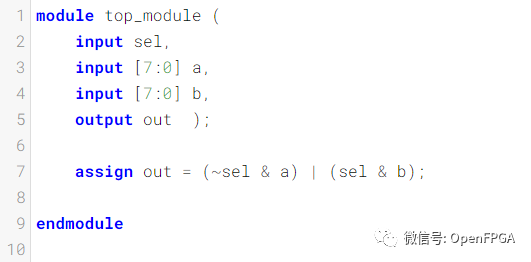

Problem 158-Bugs_mux2

题目说明

这个 8 位宽的 2 对 1 多路复用器不起作用。修复错误。

模块端口声明

module top_module (

input sel,

input [7:0] a,

input [7:0] b,

output [7:0] out );题目解析

sel的位宽不够,补到8位即可。

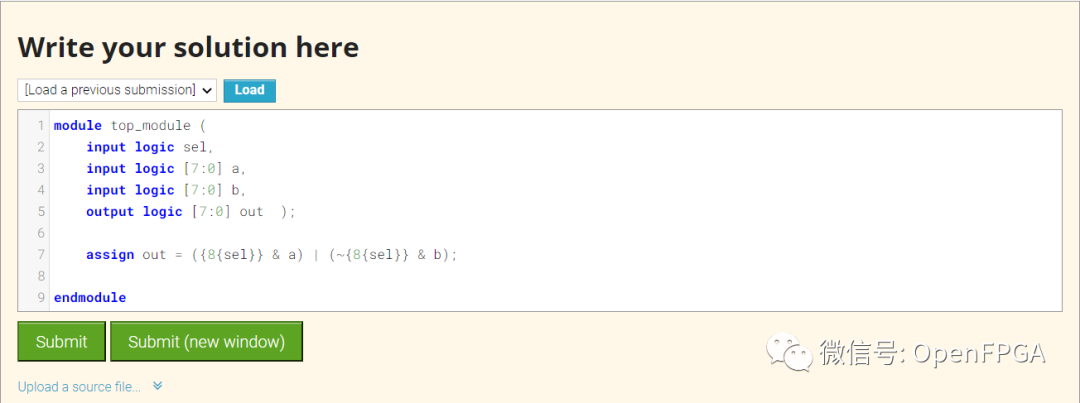

module top_module (

input logic sel,

input logic [7:0] a,

input logic [7:0] b,

output logic [7:0] out );

assign out = ({8{sel}} & a) | (~{8{sel}} & b);

endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

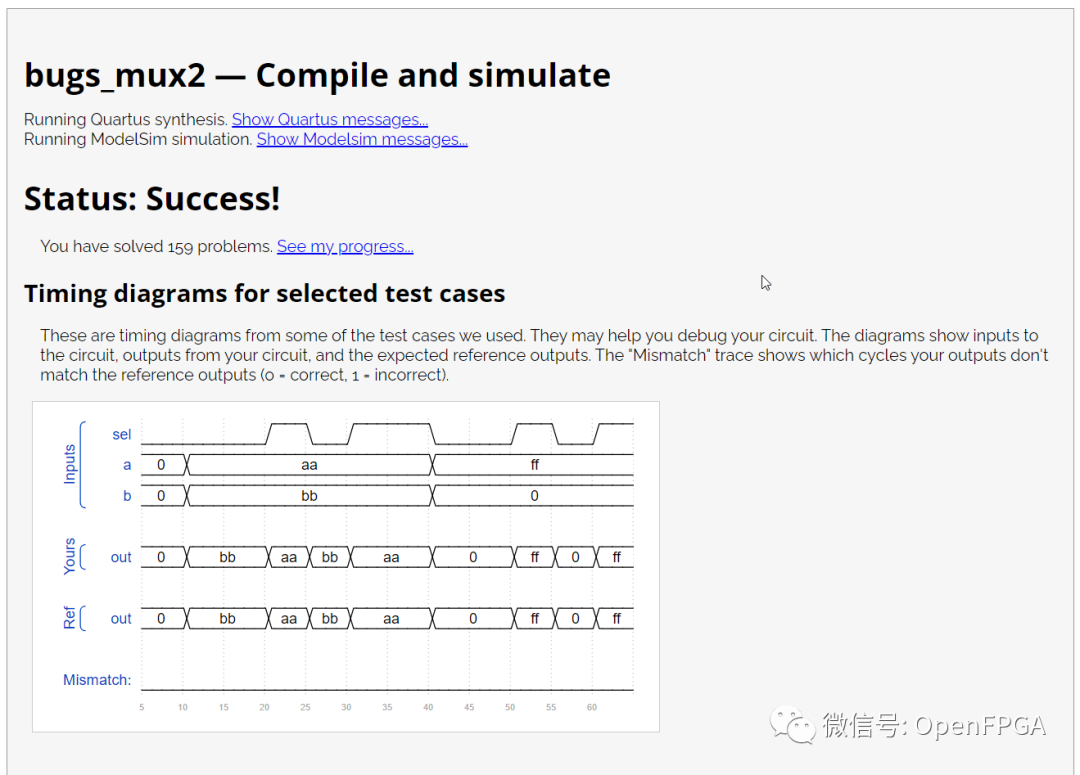

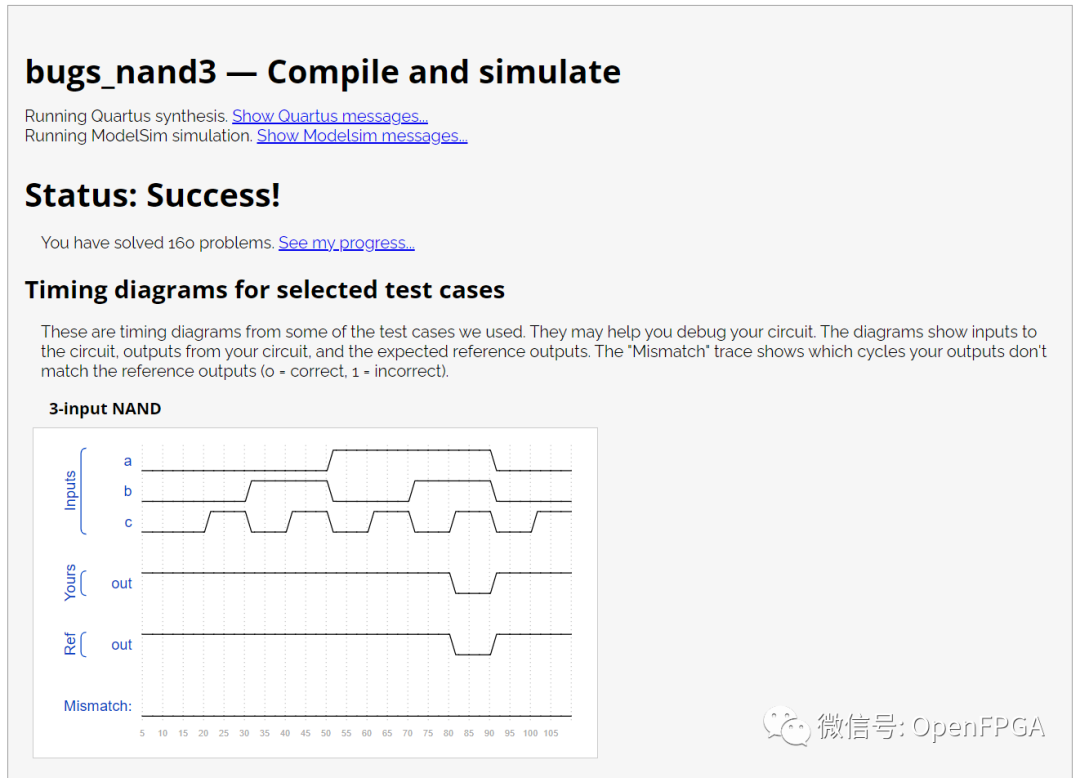

Problem 159-Bugs_nand3

题目说明

本题中的三输入与非门不工作了,找出并修正 BUG。

读者必须使用提供的 5 输入与门来实现这个与非门。

模块端口声明

module top_module (input a, input b, input c, output out);题目解析

原题中只使用了与门~

module top_module (input logic a,

input logic b,

input logic c,

output logic out

);//

var logic out_temp ;

andgate inst1 (.out(out_temp) ,

.a(a),

.b(b),

.c(c),

.d(1'd1),

.e(1'd1)

);

assign out = ~out_temp ;

endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

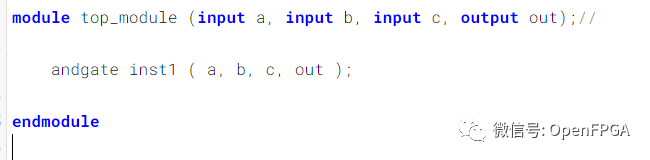

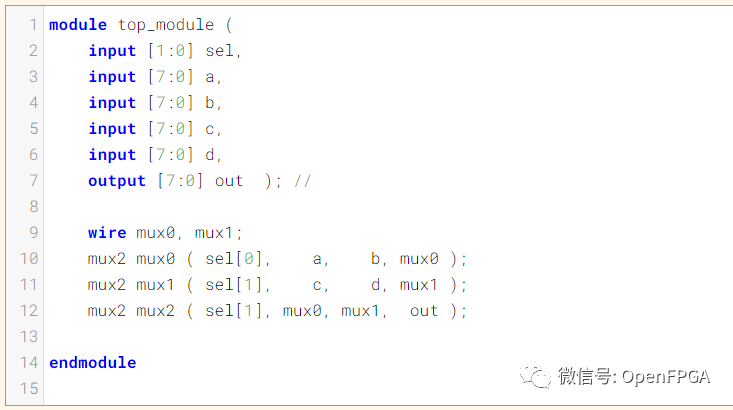

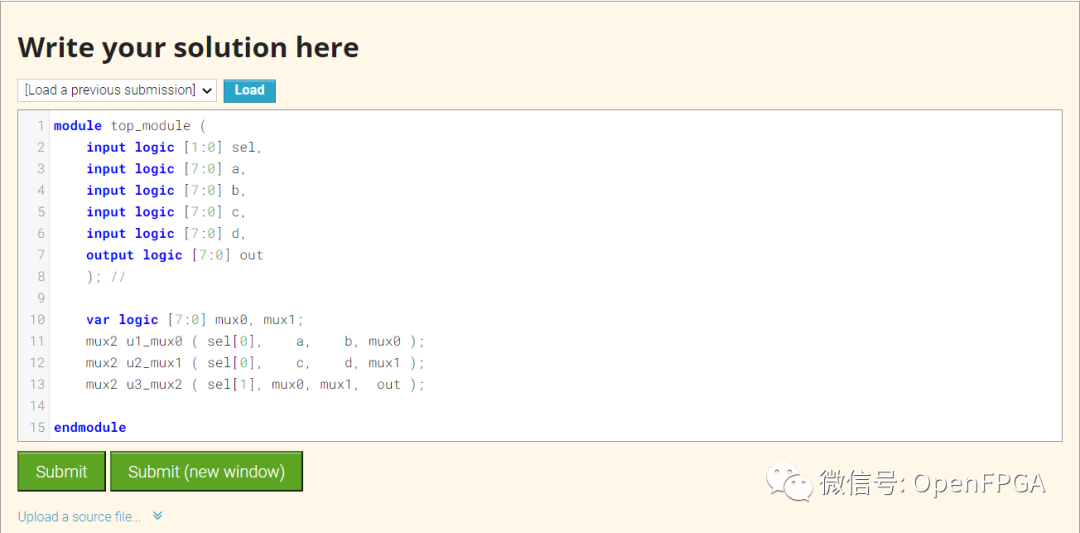

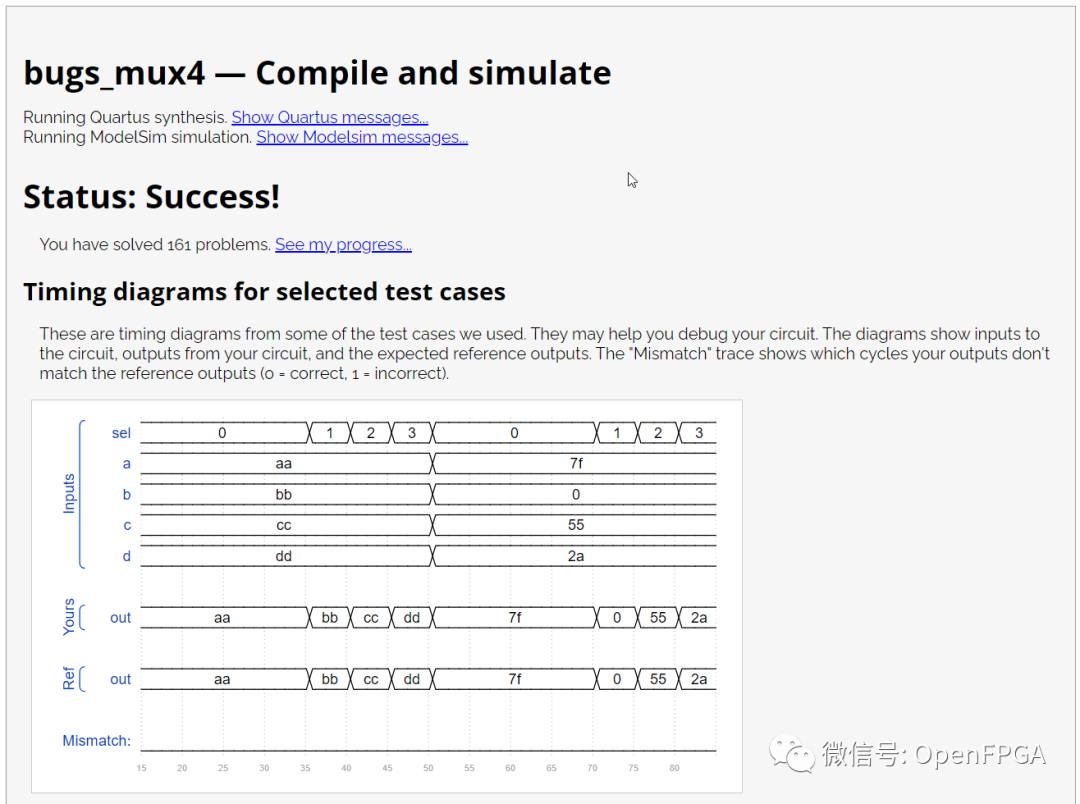

Problem 160-Bugs_mux4

题目说明

这个 4 对 1 多路复用器不起作用。修复错误。

下面无错误的 2 对 1 多路复用器:

module mux2 (

input sel,

input [7:0] a,

input [7:0] b,

output [7:0] out

);

模块端口声明

module top_module (

input [1:0] sel,

input [7:0] a,

input [7:0] b,

input [7:0] c,

input [7:0] d,

output [7:0] out );题目解析

没啥大问题,还是变量位宽问题。

module top_module (

input logic [1:0] sel,

input logic [7:0] a,

input logic [7:0] b,

input logic [7:0] c,

input logic [7:0] d,

output logic [7:0] out

); //

var logic [7:0] mux0, mux1;

mux2 u1_mux0 ( sel[0], a, b, mux0 );

mux2 u2_mux1 ( sel[0], c, d, mux1 );

mux2 u3_mux2 ( sel[1], mux0, mux1, out );

endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

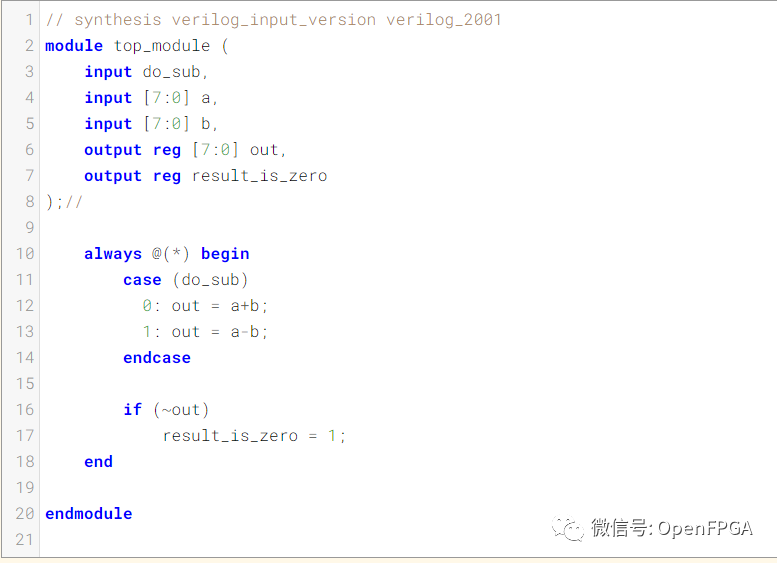

Problem 161-Bugs_addsubz

题目说明

继续找BUG

图片来自HDLBits

图片来自HDLBits

模块端口声明

module top_module (

input do_sub,

input [7:0] a,

input [7:0] b,

output reg [7:0] out,

output reg result_is_zero

);题目解析

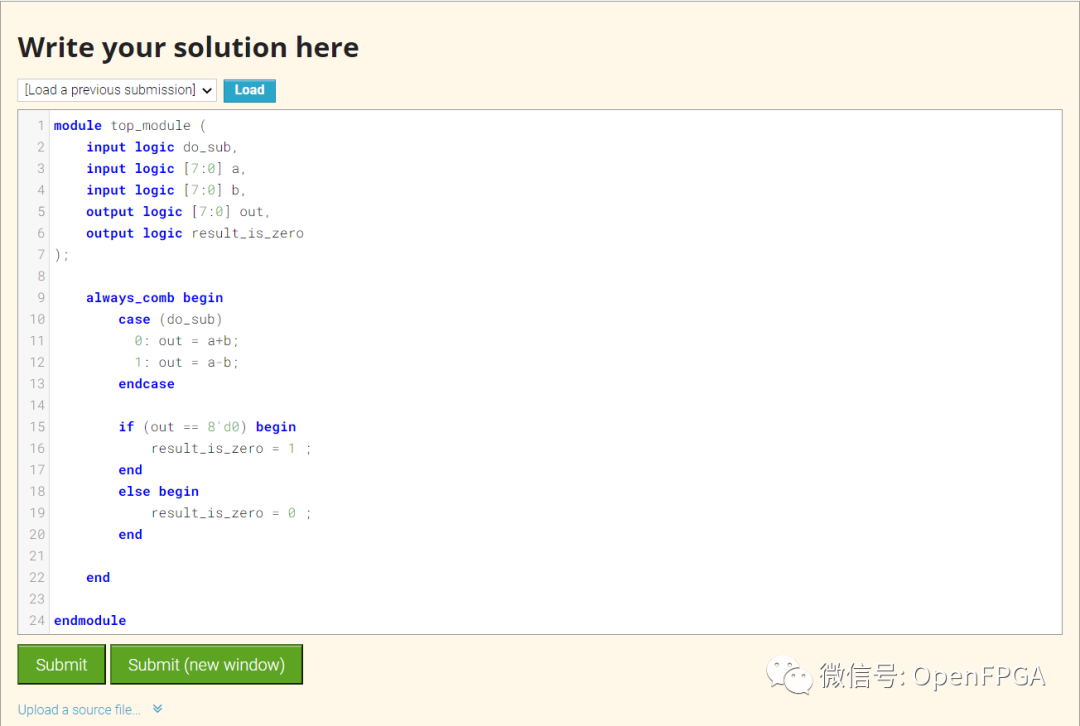

out条件举例不足。

module top_module (

input logic do_sub,

input logic [7:0] a,

input logic [7:0] b,

output logic [7:0] out,

output logic result_is_zero

);

always_comb begin

case (do_sub)

0: out = a+b;

1: out = a-b;

endcase

if (out == 8'd0) begin

result_is_zero = 1 ;

end

else begin

result_is_zero = 0 ;

end

end

endmodule

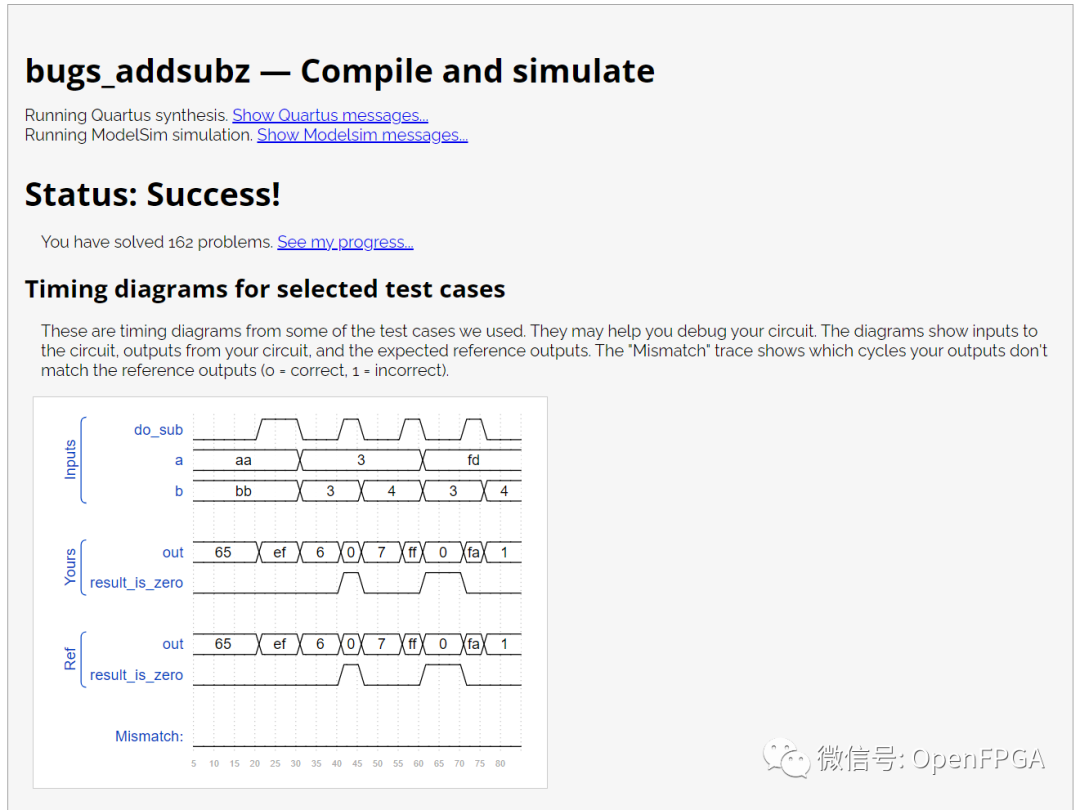

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

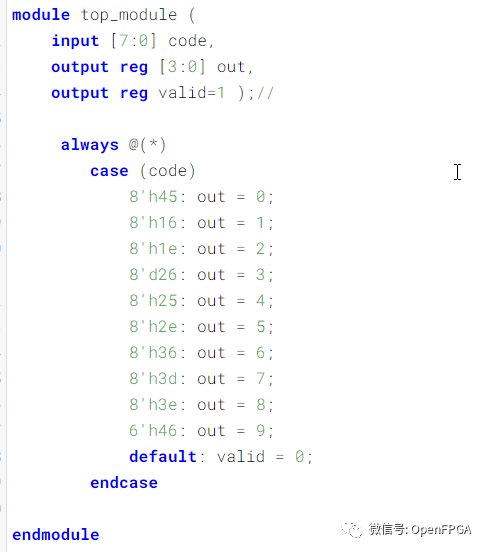

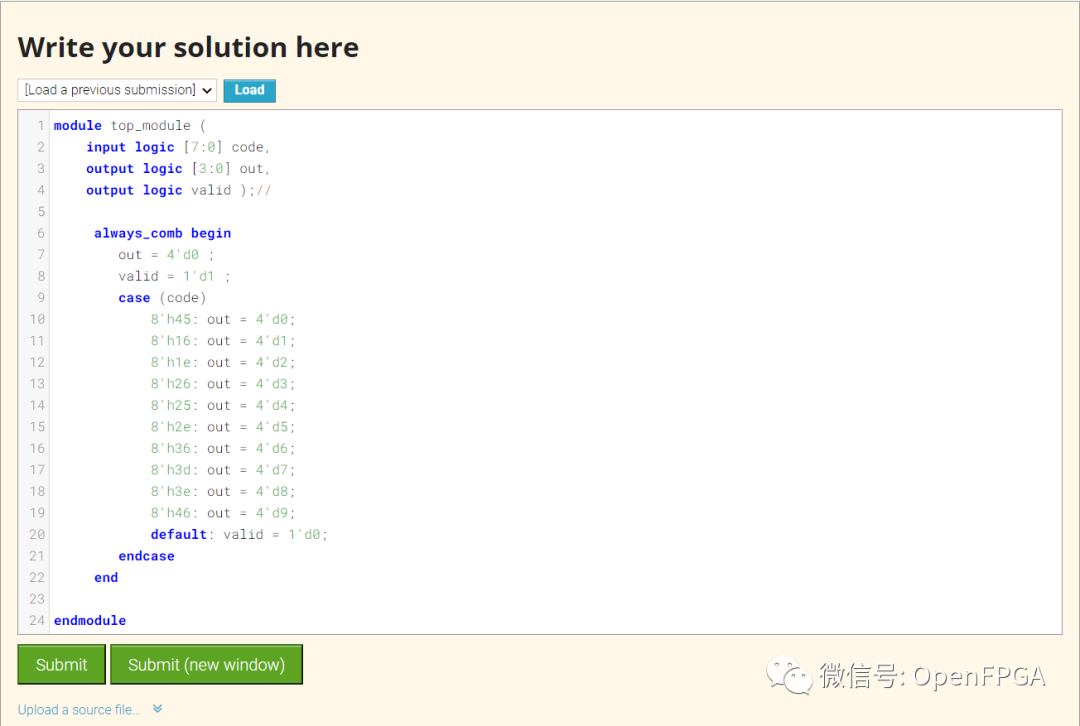

Problem 162-Bugs_case

题目说明

这个组合电路应该识别键 0 到 9 的 8 位键盘扫描码。它应该指示是否识别了 10 种情况中的一种(valid),如果是,则检测到哪个键。修复错误。

模块端口声明

module top_module (

input [7:0] code,

output reg [3:0] out,

output reg valid=1 );题目解析

信号定义时不能赋值,case最后一个选项位宽不对。

module top_module (

input logic [7:0] code,

output logic [3:0] out,

output logic valid );//

always_comb begin

out = 4'd0 ;

valid = 1'd1 ;

case (code)

8'h45: out = 4'd0;

8'h16: out = 4'd1;

8'h1e: out = 4'd2;

8'h26: out = 4'd3;

8'h25: out = 4'd4;

8'h2e: out = 4'd5;

8'h36: out = 4'd6;

8'h3d: out = 4'd7;

8'h3e: out = 4'd8;

8'h46: out = 4'd9;

default: valid = 1'd0;

endcase

end

endmodule

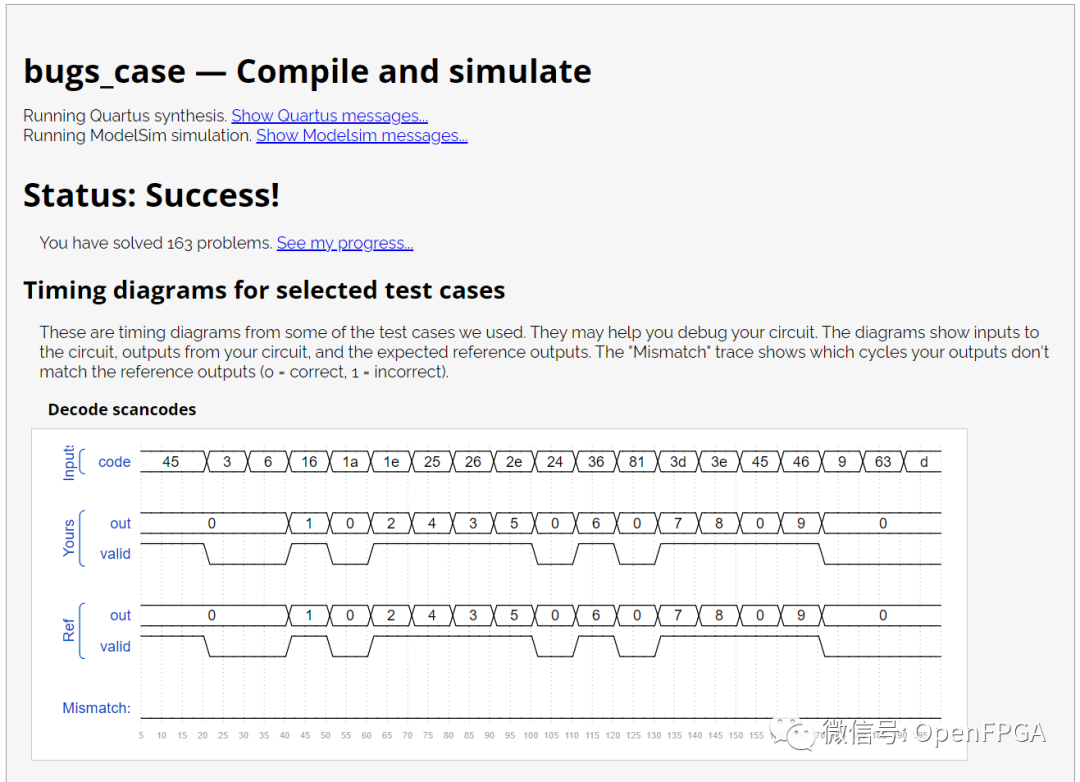

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

总结

今天的几道题就结束了,找bug开不开心~

最后我这边做题的代码也是个人理解使用,有错误欢迎大家批评指正,祝大家学习愉快~

代码链接:

https://github.com/suisuisi/SystemVerilog/tree/main/SystemVerilogHDLBits