目录

译码器的设计:

译码器和编码器是数字系统中广泛使用的多输入多输出组合逻辑部件。

实现译码的组合逻辑电路称为译码器。它的输入是一组二进制代码,输出是一组高低电平信号。每输入一组不同的代码,只有一个输出呈有效状态。

译码器的功能:对具有特定含义的输入代码进行"翻译",将其转换成相应的输出信号

译码器的分类:

译码器可分为以下四类:

变量译码器: 把输入的二进制代码的各种组合状态翻译成对应的输出信号。

码制变换译码器 :将一种代码变换为另一种代码的电路。

显示译码器:如将数据显示在七段数码管上时的译码。

地址译码器:将译码器输入端的输入地址信号翻译成相应的输出控制信号。

常用译码器:

常用的译码器有:双2:4线译码器,3:8线译码器,4:16线译码器和4:10线译码器等,其中4:10线译码器用于BCD码译码。下面就以3-8译码器为例子,介绍如何使用VHDL语言描述实现。

3-8译码器:

如图所示,是个3-8译码器(74LS138)

3个二进制输入端,对输入a, b, c的值进行译码,就可以确定哪一个输出端变为有效(低电平)

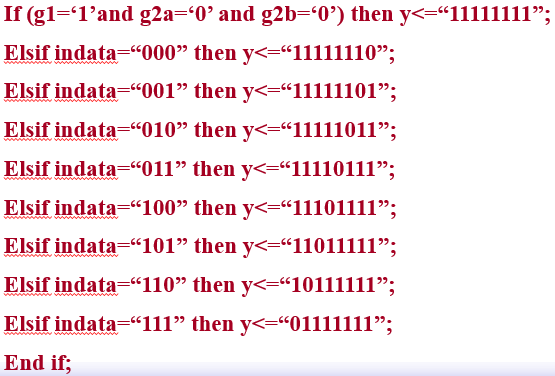

g1, g2a, g2b是选通信号,只有当g1=‘1’, g2a=‘0’和g2b=‘0’时,译码器才正常译码

3-8译码器的描述:

Case语句可用If语句进行改写:

小结:

本例设计的是一个3—8线译码器,有使能端,低电平有效。

这个程序的一、二句是库和程序包的语言。接下来是实体,主要是定义了一些输入、输出端口。需要注意的是要帮实体命名,如“

decoder_38”

,

并且工程名与实体名保持一致。还要有结束语,如

“

end decoder_38”

。

最后是结构体部分,其中“<=”是信号传输符号

,

“

indata

<=c & b & a

”

表示把c、b、a进行位合并并且赋值给信号

indata

。

进程语句是结构体的一种子程序,括号内的信号量是

process

的输入信号,这些信号无论哪个发生变化,都将启动

process

语句。