目录

编码器的设计:

与译码器类似,编码器同样是数字系统中广泛使用的多输入多输出组合逻辑部件。

什么是编码器(Decoder):

完成编码工作的组合逻辑电路称为译码器。它的输入是一组高低电平信号,输出是一组二进制代码。每输入一组高低电平信号,则输出不同的二进制代码。

编码器的功能:

将信号(如比特流)或数据进行编制、转换成用于通信,传输和存储的信号形式。

优先级编码器:

如图,74LS148是一个8输入,3位二进制码输出的优先级编码器。

当某一个输入有效时(低电平),就可以输出一个对应的3位二进制编码。

当同时有几个输入有效时,将输出优先级最高的那个输入对应的二进制编码。

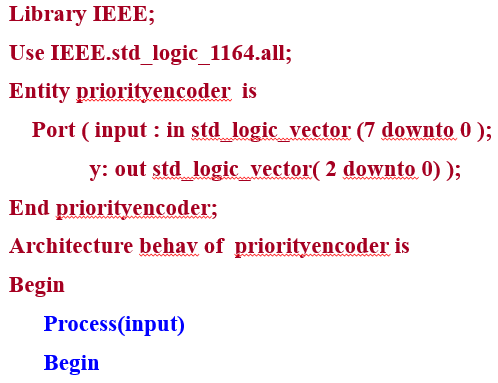

优先级编码器实现: