实验原理:

在数字电路中可以根据电路功能的不同分为,组合逻辑电路与时序逻辑电路。

组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

而时序逻辑从电路特征上看来,其特点为任意时刻的输出不仅取决于该时刻的输入,而且还和电路原来的状态有关。

组合逻辑电路在电路结构上,不涉及对信号跳变沿的处理,无存储电路,也没有反馈电路,通常可以通过真值表的形式表达出来。

时序逻辑电路在电路结构上,不管输入如何变化,仅当时钟的沿(上升沿或下降沿)到达时,才有可能使输出发生变化。

译码器(Decoder)是一种多输入多输出的组合逻辑电路,负责将二进制代码翻译为特定的对象(如逻辑电平等),功能与编码器相反。译码器一般分为通用译码器和数字显示译码器两大类,本节设计的是通用译码器。

以三八译码器为例,即将 3 种输入状态翻译成 8 种输出状态, 在 MCU 应用中,如果需要保证一定的速度情况下实现此功能,一般选取外挂一片 74HC38 或者 74LS38 等独立芯片,但 FPGA 提供了一个完整的想象以及实现空间,仅靠其自身即可实现设计要求。

Verilog HDL实现

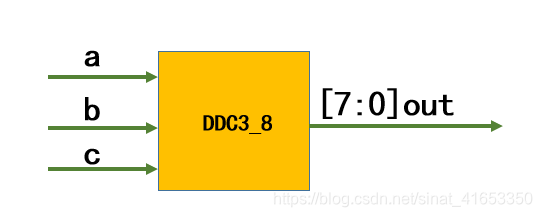

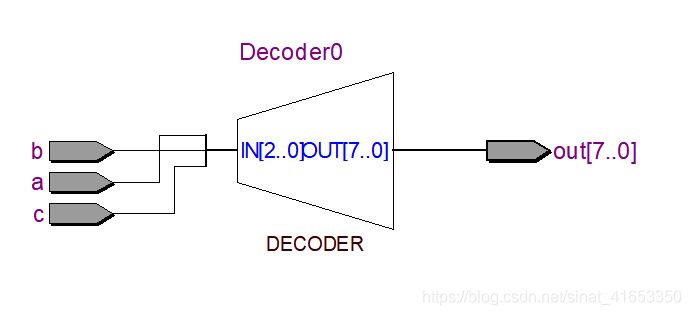

工程名称为:“DDC3_8”,架构图如下:

/

端口描述:

输入:a,b,c;

输出:out;

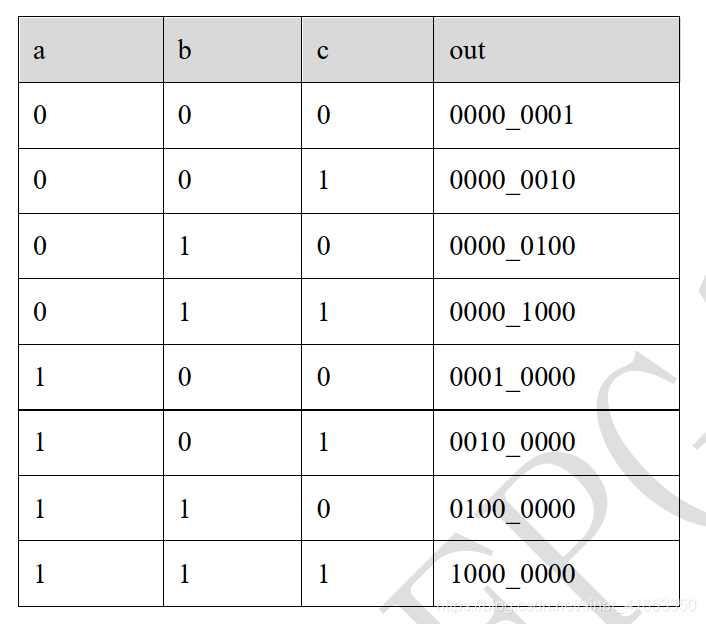

功能描述:三八译码器真值表*

*/

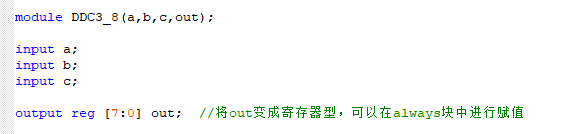

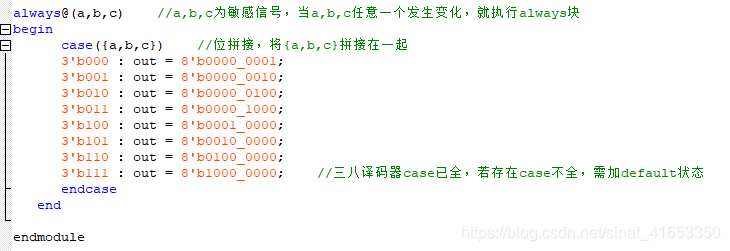

代码实现可分为两部分,分别是端口列表定义和组合逻辑实现。

使用数据选择器来实现真值表功能,由于该处已经将case中的所有情况穷举,因此不用书写default。{}为位拼接操作符,always@()括号里为敏感信号列表。由于输出数据out需在always块中赋值,所以前面将out定义成reg型。

进行分析和综合无错误后查看RTL视角

RTL Viewer:

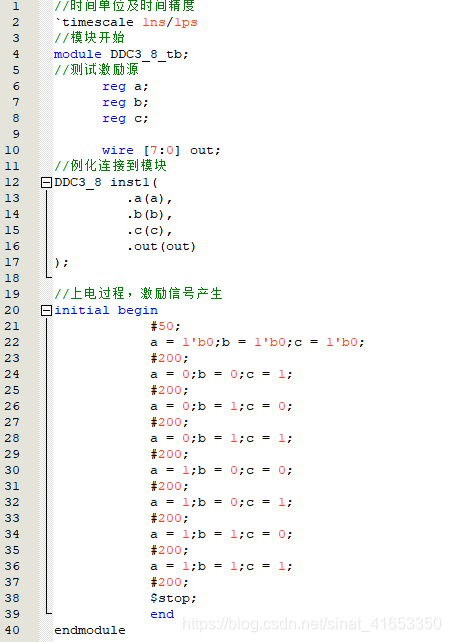

testbench文件编写

新建一个DDC3_8_tb.v文件,编写测试激励文件,整体代码如下,激励是不需要端口的,所有的信号自己内部产生,然后连接到需要测试的设计上。整体可分为四部分:时间单位定义,激励源定义,例化模块以及激励信号产生。

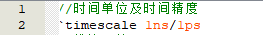

1.时间单位及精度

时标:`timescale 1ns/1ps

1) 前面的”`”是Esc键下面的键(和波浪线为同一键)。

2) “/”前面的1ns 为时间单位。

3) “/”后面的1ps为时间精度。

深入理解时标的意义:在激励中,有很多的 “# xx“,代表的意思是:延时xx ns。那么时间精度是什么呢?这个我们可以看看自己的存款余额,例如:100.21元。单位是:元,精度是:0.01元(也可以理解为:分)。对比一下,是不是一下子就理解了呢。但是,要注意,精度不能比单位大。

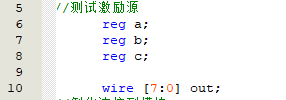

2.激励源定义

将设计的输入定义成reg的类型(在initial模块中赋值必须是reg类型),我们在激励当中对它们赋值,然后传输到设计当中。

将设计的输出定义成wire的类型,连接到设计的输出端口,在modelsim中查看输出波形是否正确。

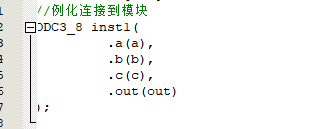

3.例化模块

有两种例化模块方法,这里选用括号里信号顺序可以随意变更,不易出错。

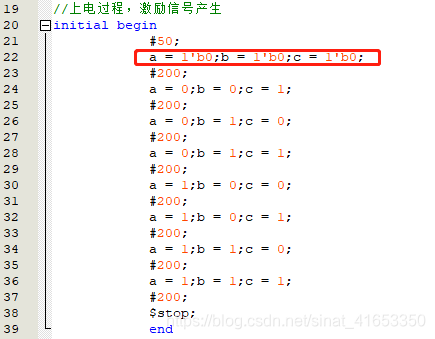

4.激励信号产生

initial 模块是顺序执行的。我们通过延时将输入在不同的时间段赋不同的值。”1’b1”:前面的“1“代表1bit,”‘b“代表用二进制表示(这个” ’“是单引号,一定要和tiemscale的”“区分开),后面的”1“代表高电平。$stop 是仿真的停止命令,具体的意思:当运行这个地方的时候,仿真自动停止。

激励仿真

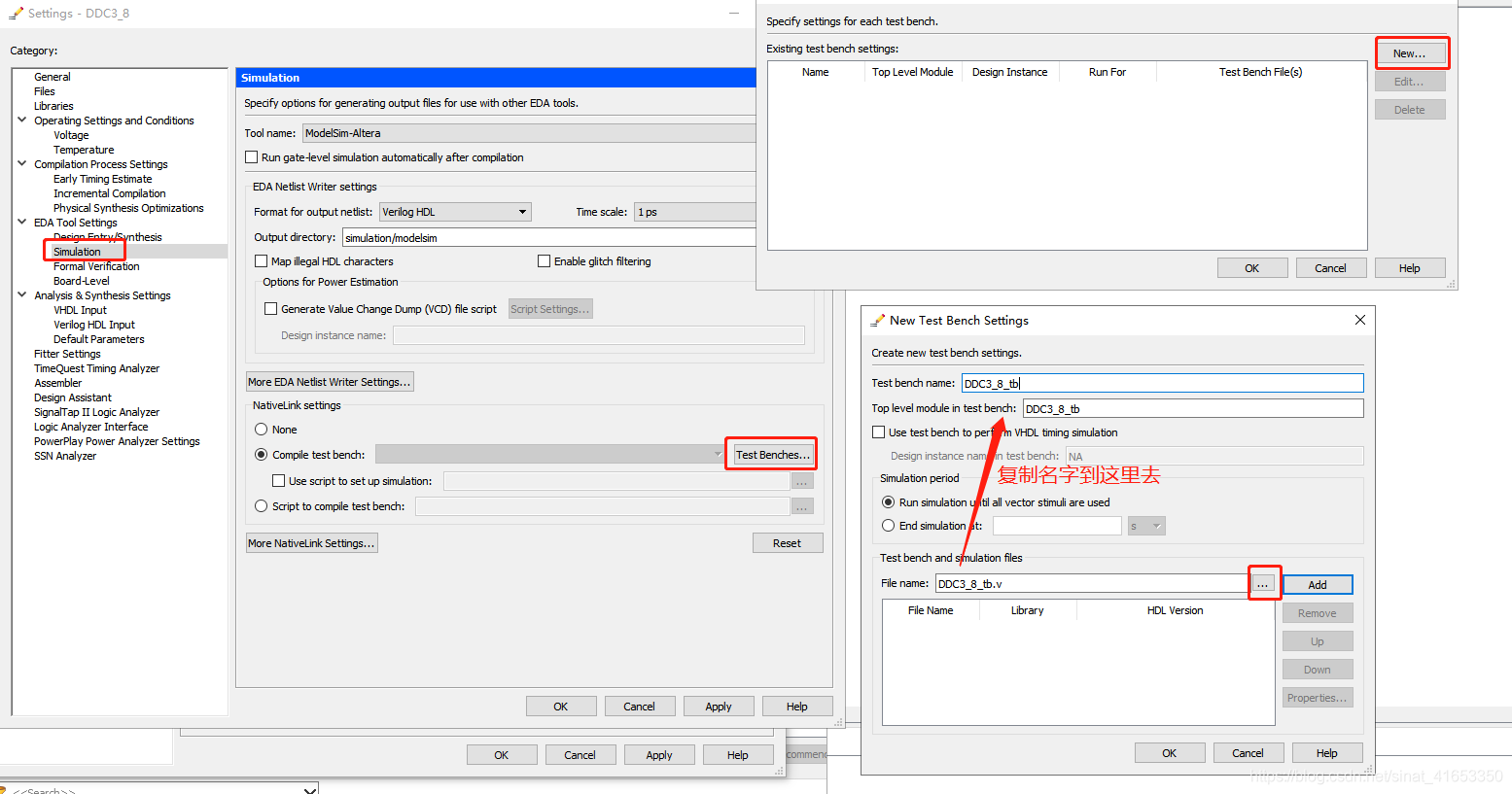

点击Assignment->setting->simulation,

按上图操作后,点击add后ok,保存。

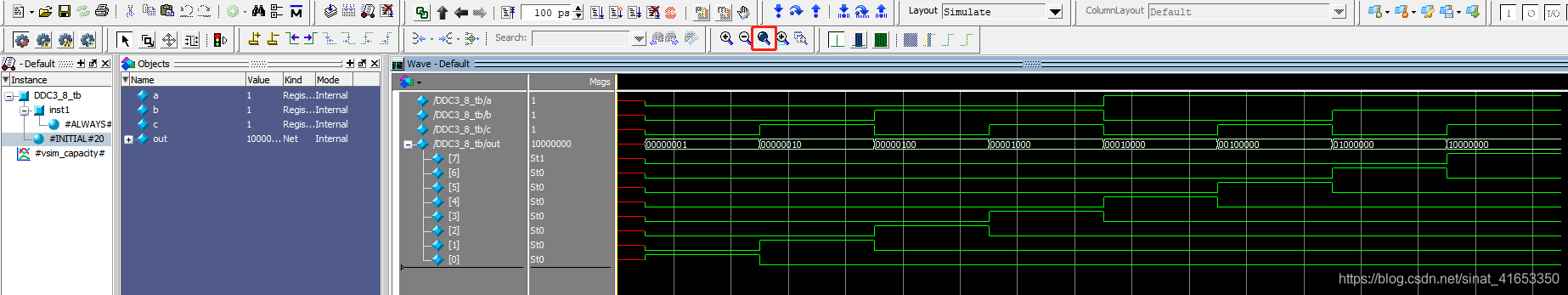

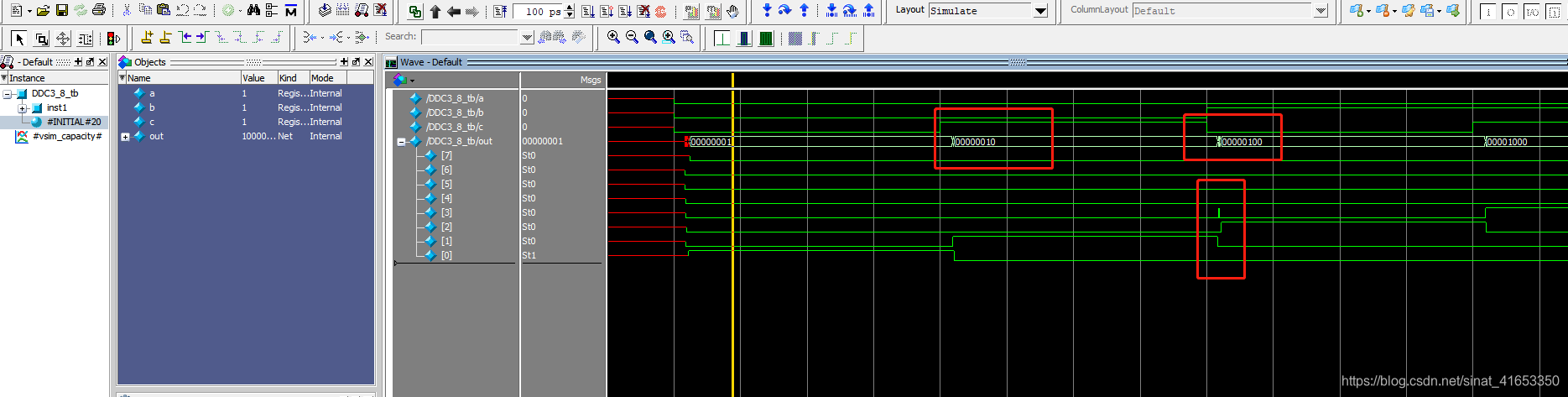

点击RTL Simulation ,进行前仿真。

由上图可知仿真没有错误,关闭Modelsim。

点击Gate Level simulation进行仿真。

发现整体数据存在一定延迟现象,但功能依然符合设计要求。

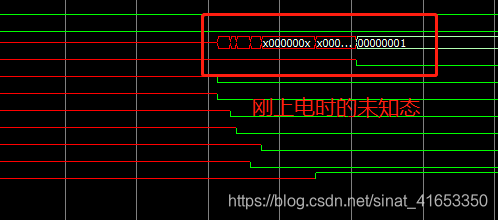

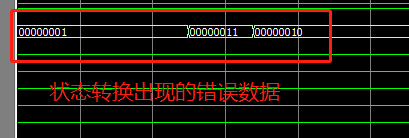

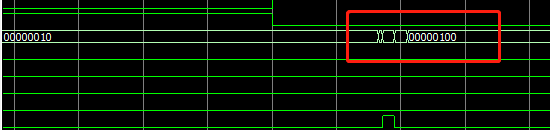

序仿真局部波形放大 0ns 处和数据转换处,可看出,刚开始上电时由于输入数据需要等待一段时间才会到达输出端口,因此存在一定时间的未知态,并在0000_0001 到 0000_0010 转换中出现了0000_0011(也可能是 0000_0000)这一数据。这是由于门电路在上面两个状态转换中, 其实际转换过程为0000_0001→0000_0011→0000_0010 或者 0000_0001→0000_0000→0000_0010。对于转换过程中出现的错误数据只能在后期进行数据筛选而没有办法避免。