目录

工程源码

GitHub - ningbo99128/verilog: 牛客网练习题工程

组合逻辑

VL11 4位数值比较器电路

至于为什么不选择更底层的题解?原因有,刷题是为了走数字ic设计,用这种门级电路搭出来的功能,其实没必要,面试也不会考。在代码上,底层到&、|、!、<<等位操作就可以了,没必要用xnor、or、and、not等描述。下面这个解题思路不错,还可以练习一下“例化”的for循环调用,挺好的。

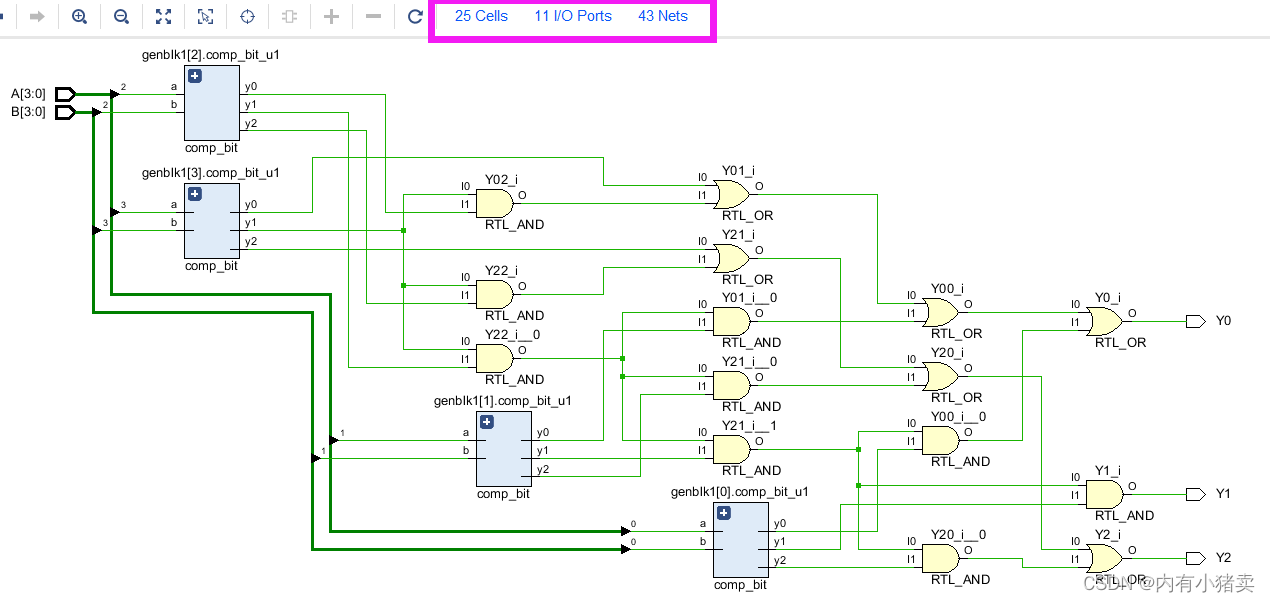

从RTL图中,可以看出代码的逻辑是先计算A[3]、B[3]和A[2]、B[2]和A[1]、B[1]和A[0]、B[0]等2位比较的结果,再通过真值表写出对应的逻辑表达式即可。

//根据题目的真值表

assign Y2 = result_y2[3]|(result_y1[3]&result_y2[2])|

(result_y1[3]& result_y1[2]&result_y2[1])|

(result_y1[3]& result_y1[2]&result_y1[1]&result_y2[0]);

assign Y1 = result_y1[3]&result_y1[2]&result_y1[1]&result_y1[0];

assign Y0 = result_y0[3]|(result_y1[3]&result_y0[2])|

(result_y1[3]& result_y1[2]&result_y0[1])|

(result_y1[3]& result_y1[2]&result_y1[1]&result_y0[0]); for循环例化

VL12 4bit超前进位加法器电路

多位加法器和超前进位加法器相比,为什么速度慢?

主要原因是高位相加时,要等待低位相加产生的进位,如果这个A、B是32位的,最高位要等31个1位全加器的耗时,才能等到进位。

超前进位加法器,就是把所有位的进位提前算出来,然后同时计算S[i] = A[i] + B[i] + C[i]。这样就快很多了。

注意:C_1是最初的进位,用来计算A_in[0]和B_in[0]的进位。

代码如下:

module lca_4(

input [3:0] A_in ,

input [3:0] B_in ,

input C_1 ,

output wire CO ,

output wire [3:0] S

);

wire [3:0] G; //G=A_in&B_in

wire [3:0] P; //P=A_in^B_in

wire [3:0] C;

genvar i;

generate

for(i = 0; i < 4;i = i + 1)

begin: PG_bit

assign G[i] = A_in[i] & B_in[i];

assign P[i] = A_in[i] ^ B_in[i];

end

endgenerate

assign C[0] = G[0] | (P[0]&C_1);

assign S[0] = P[0] ^ C_1;

genvar c_i;//c_i范围1-3

generate

for(c_i = 1; c_i < 4;c_i = c_i + 1)

begin: SC_bit

assign C[c_i] = G[c_i] | (P[c_i] & C[c_i-1]);

assign S[c_i] = P[c_i] ^ C[c_i-1];

end

endgenerate

assign CO = C[3];

endmoduleVL13 优先编码器电路①

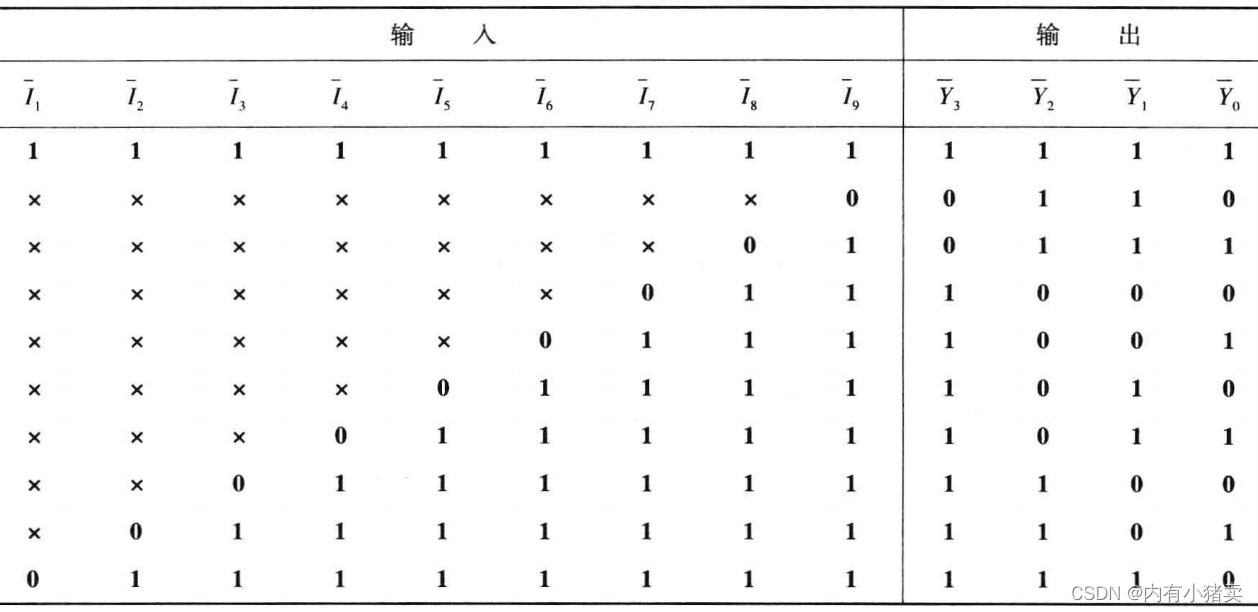

概念:优先编码器可以同时输入几个信号,但在设计时已经将各输入信号的优先顺序排好。当几个信号同时输入时,优先权最高的信号优先编码。

(9选4)优先编码器实现最方便的是使用 case语句,如下:

always @(*)begin

casex(I_n)

9'b111111111 : Y_n = 4'b1111;

9'b0xxxxxxxx : Y_n = 4'b0110;

9'b10xxxxxxx : Y_n = 4'b0111;

9'b110xxxxxx : Y_n = 4'b1000;

9'b1110xxxxx : Y_n = 4'b1001;

9'b11110xxxx : Y_n = 4'b1010;

9'b111110xxx : Y_n = 4'b1011;

9'b1111110xx : Y_n = 4'b1100;

9'b11111110x : Y_n = 4'b1101;

9'b111111110 : Y_n = 4'b1110;

default : Y_n = 4'b1111;

endcase

end case、casez、casex辨析:

1、在case语句中,敏感表达式中与各项值之间的比较是一种全等比较,每一位都相同才认为匹配。

2、在casez语句中,如果分支表达式某些位的值为高阻z,那么对这些位的比较就会忽略,不予考虑,而只关注其他位的比较结果。

3、在casex语句中,则把这种处理方式进一步扩展到对x的处理,即如果比较双方有一方的某些位的值是z或x,那么这些位的比较就不予考虑。

参考文章:Verilog语言中case、casex、casez的用法和区别_摆渡沧桑的博客-CSDN博客_casex和casez

VL14 用优先编码器①实现键盘编码电路

题目:

请使用优先编码器①实现键盘编码电路,可添加并例化题目中已给出的优先编码器代码。10个按键分别对应十进制数0-9,按键9的优先级别最高;按键悬空时,按键输出高电平,按键按下时,按键输出低电平;键盘编码电路的输出是8421BCD码。要求:键盘编码电路要有工作状态标志,以区分没有按键按下和按键0按下两种情况。

题目解析:

| 键盘状态 |

S[9:0] |

L[3:0] |

GS |

| 无按键按下 |

11_1111_1111 |

0000 |

0 |

| 按键0按下 |

11_1111_1110 |

0000 |

1 |

| 其他按键按下 |

xx_xxxx_xxx1 |

xx |

1 |

代码:

module key_encoder(

input [9:0] S_n ,

output wire[3:0] L ,

output wire GS

);

wire [3:0] L_reg;

encoder_0 u1_encoder_0(

.I_n(S_n[9:1]),

.Y_n(L_reg)

);

//有按键按下 GS == 1

assign GS = ~((&L_reg) & S_n[0]);

assign L = (GS == 1)? ~L_reg : 4'b0;

endmoduleVL15 优先编码器Ⅰ

VL15和VL13的区别是 这次题目8-3优先编码器只给定了wire型的输出变量,意味着要找到逻辑关系用assign来描述实现,而不能用case语句去描述。

解析:

①当EI=1,I=0时,EO=1,其余为0;因此EO = EI & ~(|I)。

②当EI=1,I ≠ 0时,GS = 1,其余为0;因此GS = EI & (|I)。

③同理,当EI=1,I = 8'b1xxx_xxxx、I = 8'b01xx_xxxx、I = 8'b0000_1xxx、I = 8'b0000_01xx4种状态时,Y[1] = 1。因此我们可以描述为assign Y[1] = EI & (I[7] | I[6] | (~I[7]&~I[6]&~I[5]&~I[4]&I[3]) | (~I[7]&~I[6]&~I[5]&~I[4]&~I[3]&I[2]) );

但是,为什么最终代码把红色部分省略了?

因为红色部分省略后并不影响表达式的逻辑功能,可以减少冗余。例如,I[7]和I[6]的状态1已经使用过,那么剩下的只有假状态。因此~I[7]&~I[6] 没有必要再写出来。

assign Y[2] = EI & (I[7] | I[6] | I[5] | I[4]);

assign Y[1] = EI & (I[7] | I[6] | (~I[5]&~I[4]&I[3]) | (~I[5]&~I[4]&I[2]));

assign Y[0] = EI & (I[7] | (~I[6]&I[5]) | (~I[6]&~I[4]&I[3]) | (~I[6]&~I[4]&~I[2]&I[0]));

assign GS = EI & (|I); //I的每一位相或

assign EO = EI & ~(|I);VL16 使用8线-3线优先编码器Ⅰ

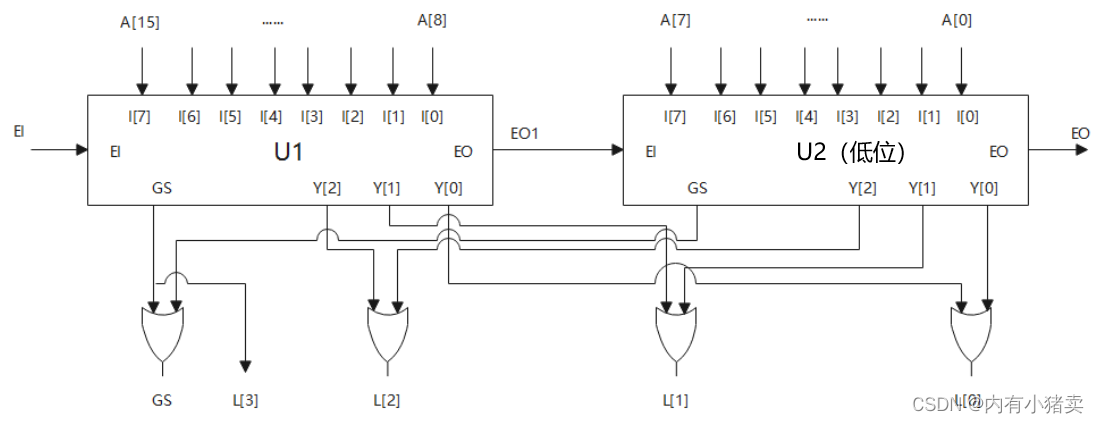

题目:请使用2片8线-3线优先编码器Ⅰ及必要的逻辑电路实现16线-4线优先编码器。优先编码器Ⅰ的真值表和代码已给出(VL15)。

解析:看逻辑图写代码

module encoder_164(

input [15:0] A ,

input EI ,

output wire [3:0] L ,

output wire GS ,

output wire EO

);

wire GS_1;

wire EO_1;

wire GS_2;

wire EO_2;

wire [2:0] Y_1;

wire [2:0] Y_2;

encoder_83 u1_encoder_83( //高位

.I(A[15:8]) ,

.EI(EI) ,

.Y (Y_1 ) ,

.GS(GS_1) ,

.EO(EO_1)

);

encoder_83 u2_encoder_83( //低位

.I(A[7:0]) ,

.EI(EO_1) ,

.Y (Y_2 ) ,

.GS(GS_2) ,

.EO(EO_2)

);

assign L[3] = GS_1;

assign L[2] = Y_1[2] | Y_2[2];

assign L[1] = Y_1[1] | Y_2[1];

assign L[0] = Y_1[0] | Y_2[0];

assign GS = GS_1 | GS_2;

assign EO = EO_2;

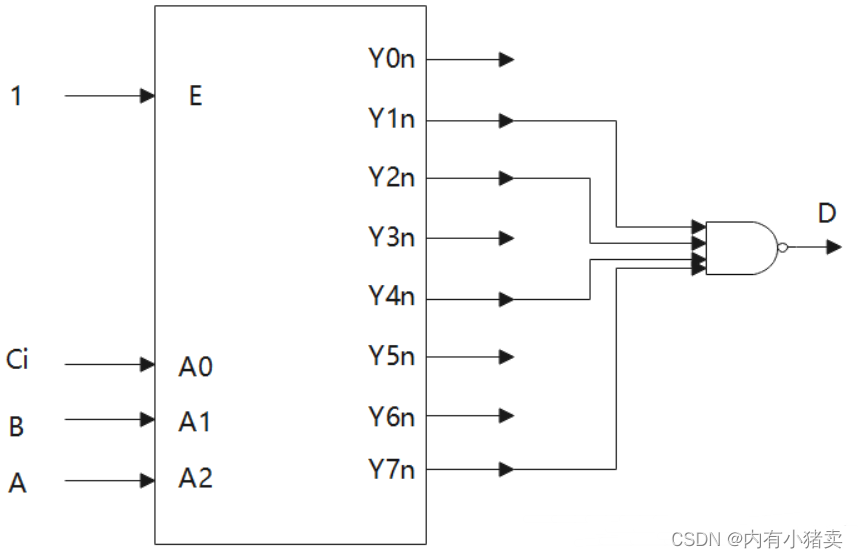

endmoduleVL17 用3-8译码器实现全减器

题目分析:

先写出一位全减器真值表,再给 D 和 Co 分别例化一个3-8译码器,再将有输出的位进行与非。

例如:采用3-8译码器和与非门实现D的逻辑功能。

代码实现:

module decoder1(

input A , //被减数

input B ,

input Ci , //借位

output wire D , //差

output wire Co //借位

);

wire D_0,D_1,D_2,D_3,D_4,D_5,D_6,D_7;

wire Co_0,Co_1,Co_2,Co_3,Co_4,Co_5,Co_6,Co_7;

decoder_38 u1_decoder_38( //差D

.E (E ),

.A0 (Ci ),

.A1 (B ),

.A2 (A ),

.Y0n (D_0 ),

.Y1n (D_1 ),

.Y2n (D_2 ),

.Y3n (D_3 ),

.Y4n (D_4 ),

.Y5n (D_5 ),

.Y6n (D_6 ),

.Y7n (D_7 )

);

decoder_38 u2_decoder_38( //借位Co

.E (E ),

.A0 (Ci ),

.A1 (B ),

.A2 (A ),

.Y0n (Co_0 ),

.Y1n (Co_1 ),

.Y2n (Co_2 ),

.Y3n (Co_3 ),

.Y4n (Co_4 ),

.Y5n (Co_5 ),

.Y6n (Co_6 ),

.Y7n (Co_7 )

);

//1、全减器真值表 2、按真值表代入

assign D = ~((D_1) & (D_2) & (D_4) & (D_7));

assign Co = ~((Co_1) & (Co_2) & (Co_3) & (Co_7));

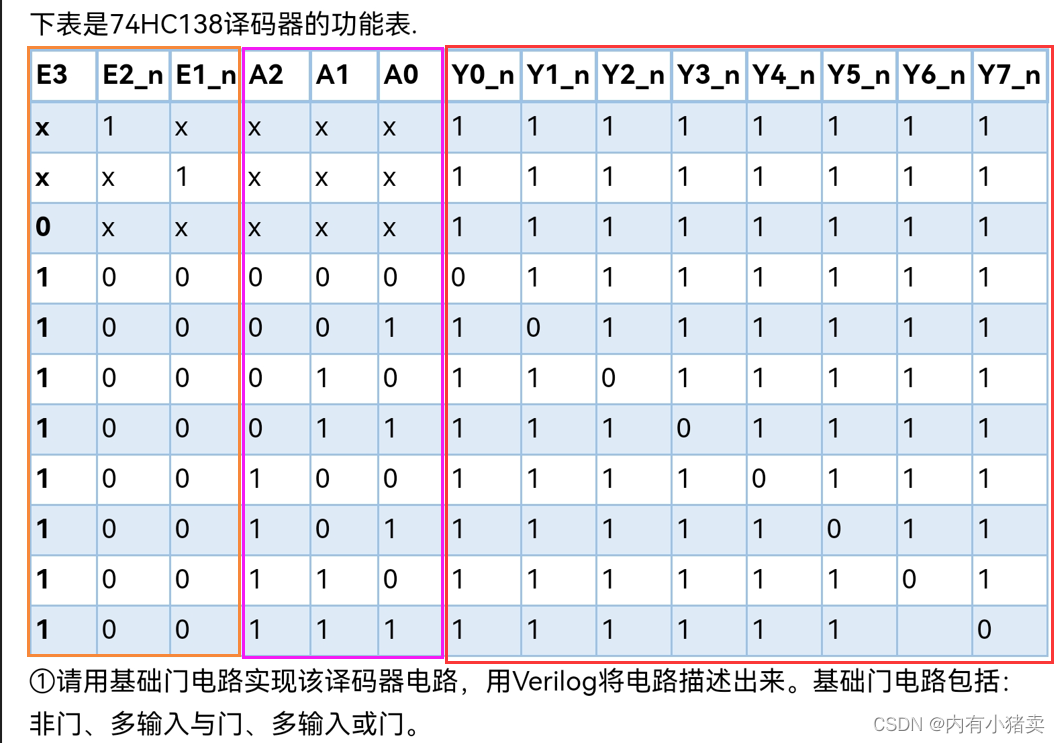

endmoduleVL18 实现3-8译码器①

看真值表写代码:

`timescale 1ns/1ns

module decoder_38(

input E1_n ,

input E2_n ,

input E3 ,

input A0 ,

input A1 ,

input A2 ,

output wire Y0_n ,

output wire Y1_n ,

output wire Y2_n ,

output wire Y3_n ,

output wire Y4_n ,

output wire Y5_n ,

output wire Y6_n ,

output wire Y7_n

);

wire E;

assign E = E3 & (~E2_n) & (~E1_n);

assign Y0_n = ~(E & (~A2) & (~A1) & (~A0));

assign Y1_n = ~(E & (~A2) & (~A1) & (A0));

assign Y2_n = ~(E & (~A2) & (A1) & (~A0));

assign Y3_n = ~(E & (~A2) & (A1) & (A0));

assign Y4_n = ~(E & (A2) & (~A1) & (~A0));

assign Y5_n = ~(E & (A2) & (~A1) & (A0));

assign Y6_n = ~(E & (A2) & (A1) & (~A0));

assign Y7_n = ~(E & (A2) & (A1) & (A0));

endmoduleVL19 使用3-8译码器①实现逻辑函数L

请使用3-8译码器①和必要的逻辑门实现函数L=(~A)·C+A·B

module decoder0(

input A ,

input B ,

input C ,

output wire L

);

decoder_38 u1_decoder_38(

.E1_n (0 ) ,

.E2_n (0 ) ,

.E3 (1 ) ,

.A0 (C ) ,

.A1 (B ) ,

.A2 (A ) ,

.Y0_n (Y0_n ) ,

.Y1_n (Y1_n ) ,

.Y2_n (Y2_n ) ,

.Y3_n (Y3_n ) ,

.Y4_n (Y4_n ) ,

.Y5_n (Y5_n ) ,

.Y6_n (Y6_n ) ,

.Y7_n (Y7_n )

);

//38译码器 有效输出为0

assign L = ~(Y1_n & Y3_n & Y6_n & Y7_n);

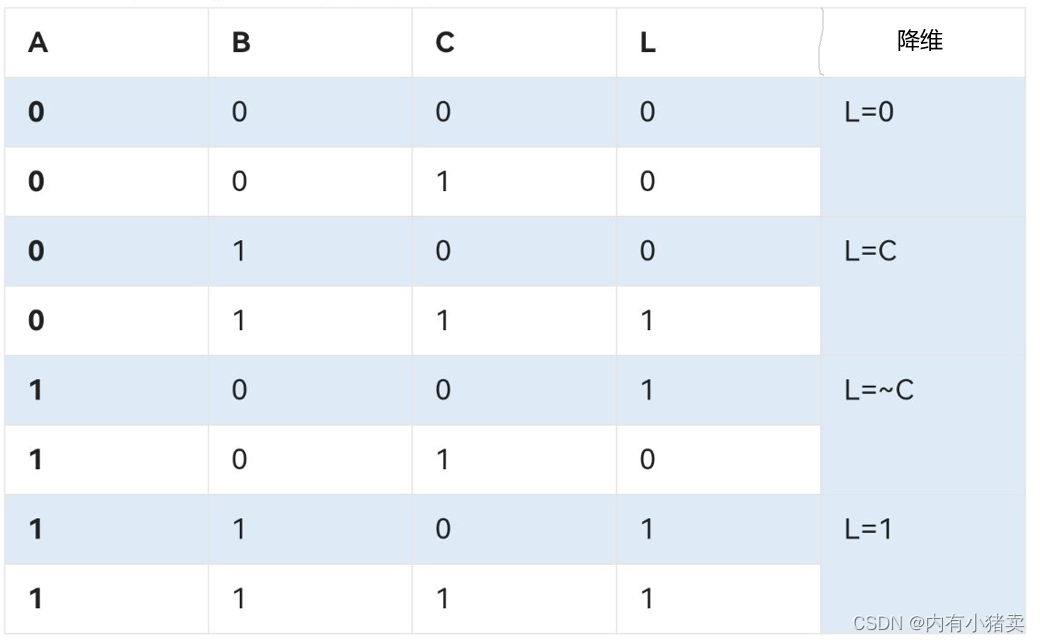

endmoduleVL20 数据选择器实现逻辑电路

题目分析:四选一数据选择器实现3变量逻辑电路,会要用到降维,否则表达的情况不够。

L = AB + AC' + BC = AC' + BC

`timescale 1ns/1ns

module data_sel(

input S0 ,

input S1 ,

input D0 ,

input D1 ,

input D2 ,

input D3 ,

output wire Y

);

assign Y = ~S1 & (~S0&D0 | S0&D1) | S1&(~S0&D2 | S0&D3);

endmodule

module sel_exp(

input A ,

input B ,

input C ,

output wire L

);

data_sel u0_data_sel( //高位

.S1(A ),

.S0(B ),

.D3(1 ),

.D2(~C ),

.D1(C ),

.D0(0 ),

.Y (L )

);

endmodule耶,到这里就结束了组合逻辑,下面就是时序逻辑学习啦!放一张哆啦A梦