一、实验目的

1.掌握组合逻辑电路的设计与测试方法

2.掌握中规模集成译码器的逻辑功能和使用方法

3.掌握触发器的应用

二、实验的设备与器件

1.+5V直流电源

2.连续脉冲源

3.单次脉冲源

4.逻辑电平开关

5.逻辑电平显示器

6.拨码开关

7.译码显示器

8.集成芯片:

9.CC4011x2(74LS00),CC4012x3(174LS20),74LS138x2,CC5411,74LS48,74LS112(或CC4027),

CC4081

三、实验内容

1、用与非门设计3输入的多数表决器,要求按文本所述的设计步骤进行,直达测试电路逻辑功能符合设计要求为止。

2、在Logisim软件中用3线8线译码器设计一个判断输入三位二进制数是否大于等于4的电路。

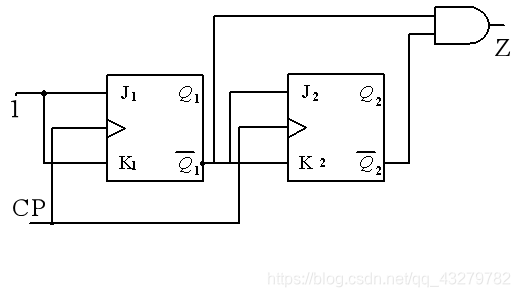

3、根据如下时序逻辑电路,分析其功能并在实验箱上用芯片验证结果。

四、实验过程与结果

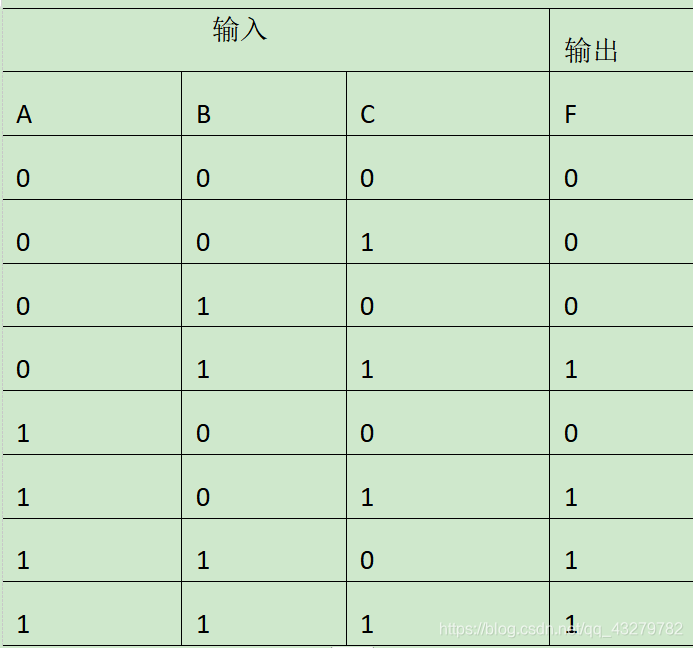

1.多数表决器的设计

(1)画出真值表

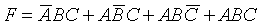

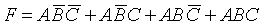

根据以上真值表,得出输出表达式如下

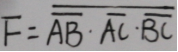

化简得:

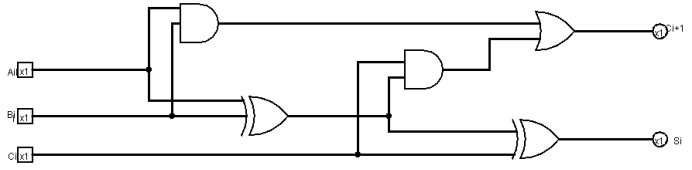

逻辑电路图如下图所示

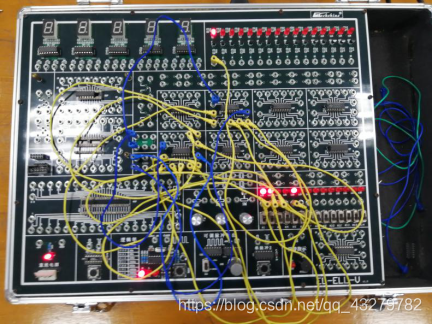

在实实验箱上用触发器芯片验证结果

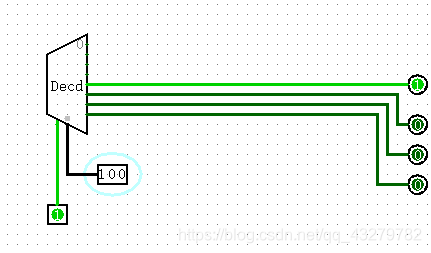

(2)三线八线译码器设计一个三位二进制输入是否大于4的电路

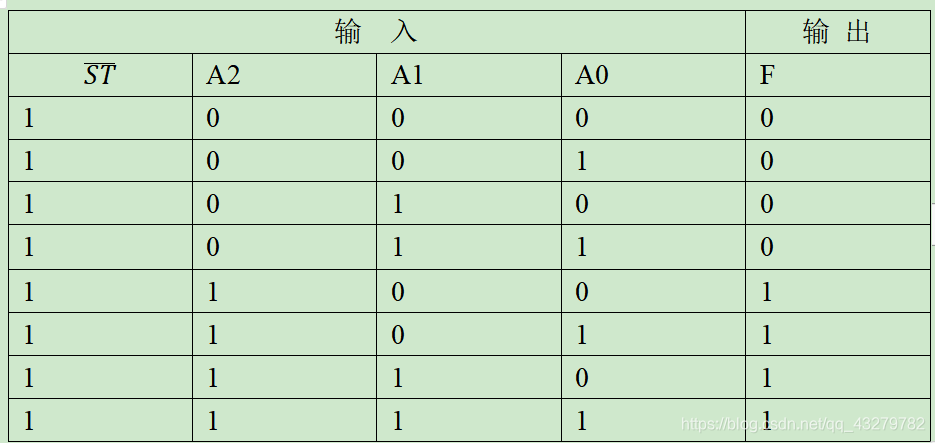

(1)列出真值表

根据以上真值表,得出输出表达式如下

在logism中测试如下

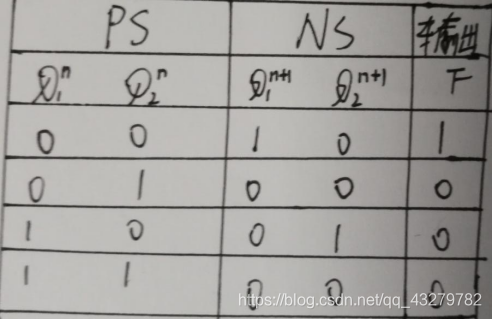

3时序逻辑电路的分析

(1)根据电路图写出输出函数表达式

(2)写出真值表

(3)写出电路功能

功能:模为4的加法器

五、实验心得

1.理解了芯片引脚的接入,以及logism的使用,但是仍然不熟练。

2.在logism中用几个输入就用几个引脚。

3.加强对表达式的化简以及画电路图。