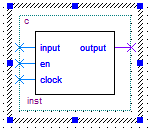

11)c部分

library ieee;

use ieee.std_logic_1164.all;

entity c is

port(input:in std_logic;

en:in std_logic;

clock:in std_logic;

output:out std_logic:='0'

);

end c;

architecture st of c is

signal i:std_logic:='0';

begin

process(en,clock)

begin

if (en='1' and clock='1') then--rising_edge(clock)

i<=input;

end if;

end process;

output<=i;

end st;

接口设计:

Clock:时钟信号

en:使能信号

input:输入信号

output:输出信号

功能实现:

存储进位c,借位z和移位c的值,用于JC,JZ操作。

仿真验证:

与cpu在同一文件中,与cpu同仿真。

下篇点此