作为一名数字电路设计工程师,为了避免设计一些垃圾出来。应该深入理解为什么一个电路具有延时以及如何修改这个电路以改善延时。设计者还必须有一些简单的模型能用手工快速估算性能并能理解为什么某些电路比另一些好。EDA工具能够精确快速的估算复杂的延时模型,所以逻辑努力方法不应当用来代替这样的工具。它的价值在于能进行快速粗略的手工计算并能展现电路设计的深层含义。

名词定义

驱动器 driver

对一个节点充电或者放电的门

负载 load

被驱动的门和导线

传播延时 propagation delay time

t p d t_{pd} tpd 表示输入越过50%至输出越过50%之间的最长时间,也称为最大延时。

污染延时 contamination delay time

t c d t_{cd} tcd 表示输入越过50%至输出越过50%之间的最短时间,也称为最小延时。

上升时间 rise time

t r t_{r} tr 表示一个波形从稳定值得20%上升至80%所需要的时间

下降时间 fall time

t f t_{f} tf 表示一个波形从稳定值得20%下降至80%所需要的时间

逻辑努力

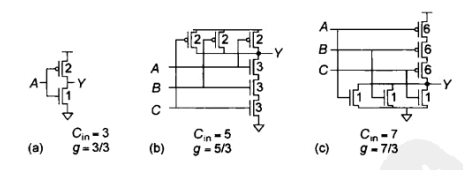

门的输入电容与一个能提供与这个门相同输出电流的反相器的输入电容之比,用 g g g表示。反相器的逻辑努力定义为1。逻辑努力反应一个逻辑门的复杂度。下图(b)是一个与非门,图(c)是一个或非门。对于同等输入数目而言,与非门要比或非门的逻辑努力小。

这里用到的是等效的概念。抑或是参照的意思,就像国际上对于质量单位千克的定义。

电气努力

定义为被驱动的外部负载电容与驱动门的输入电容之比。用b表示,也可以用h表示。

b = C o u t C i n b=\frac{C_{out}}{C_{in}} b=CinCout

RC延时模型

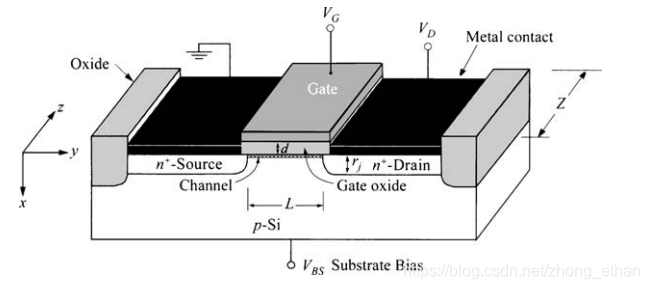

信号经过一个逻辑门发生延时的根本原因是对电容充放电需要时间。下图是一个MOS管的结构图。栅极与衬底之间的电容称为栅电容,源极或漏极与衬底之间的电容称为扩散电容。逻辑门翻转时,MOS管主要工作在线性区,源漏之间的电流与源漏之间电压成正比,此时可用一个线性电阻R表征。NMOS的载流子是电子,PMOS的载流子是空穴。电子的迁移率大约为空穴的两倍。因此,为了使PMOS具有和NMOS相同的电阻R,PMOS管的沟道宽度必须是NMOS管的两倍。栅电容,扩散电容也因此是NMOS管的两倍。也可以这么说,如果PMOS与NMOS沟道宽度一致,那么PMOS的沟道电阻是NMOS沟道电阻的2倍。

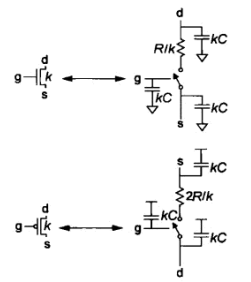

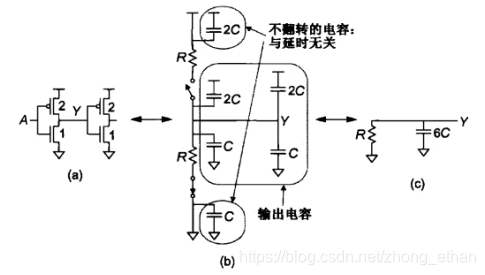

晶体管的RC等效电路如下所示,上面是一个沟道宽度为单位宽度K倍的NMOS管。下面是一个沟道宽度为单位宽度K倍的PMOS管。

反相器的等效电路如下图所示

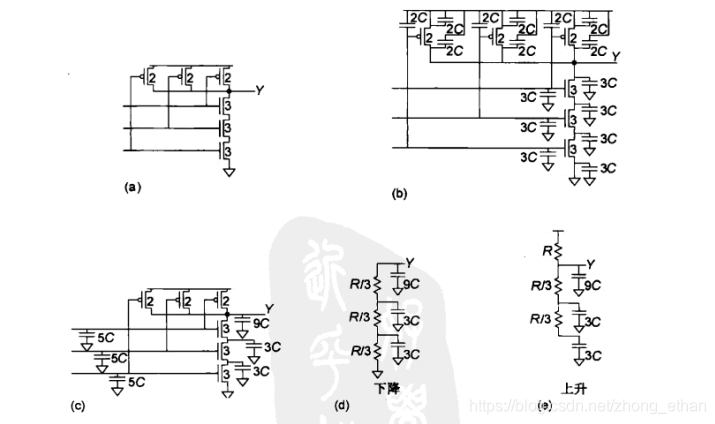

一个三输入与非门的等效电路如下图所示

Elmore延时

Elmore延时模型把从信号源发生翻转到其中一个叶子节点发生变化之间的延时估计为将在每个节点 i i i上的电容 C i C_{i} Ci乘以从信号源至该节点 i i i及叶子节点公共路劲的等效电阻 R i s R_{is} Ris的积全部相加所得到的的和。用公式表示为:

t p d = Σ i R i s C i t_{pd} = \Sigma_{i}R_{is}C_{i} tpd=ΣiRisCi

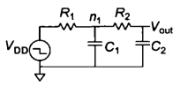

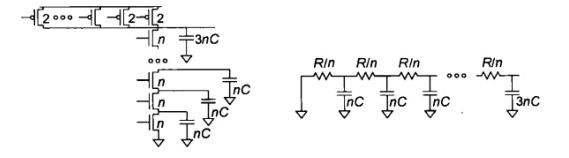

举个例子。下图是一个二阶RC系统。

n 1 n_{1} n1节点的延时为 R 1 C 1 R_{1}C_{1} R1C1, V o u t V_{out} Vout节点的延时为 R 1 C 1 + ( R 1 + R 2 ) C 2 R_{1}C_{1}+(R_{1}+R_{2})C_{2} R1C1+(R1+R2)C2。

参考上面反相器的等效电路,忽略其寄生电容,一个扇出为1的理想反相器的延时 τ = 3 R C \tau = 3RC τ=3RC。表示归一化延时d时就是相对这一反相器的延时。

线性延时模型

一个门的归一化延时以 τ \tau τ为单位表示为

d = f + p d = f +p d=f+p

p是未连接负载时的寄生延时,f是努力延时,也称为单级努力,取决于这个门的复杂程度和扇出。

f = g b f=gb f=gb (记忆方法:努力延时等于几把)

电气努力 b = C o u t C i n b=\frac{C_{out}}{C_{in}} b=CinCout

逻辑努力 g = C i n C i n v e r t e r g = \frac{C_{in}}{C_{inverter}} g=CinverterCin

从上面公式很容易理解,努力延时本质上是由负载电容引起的延时。

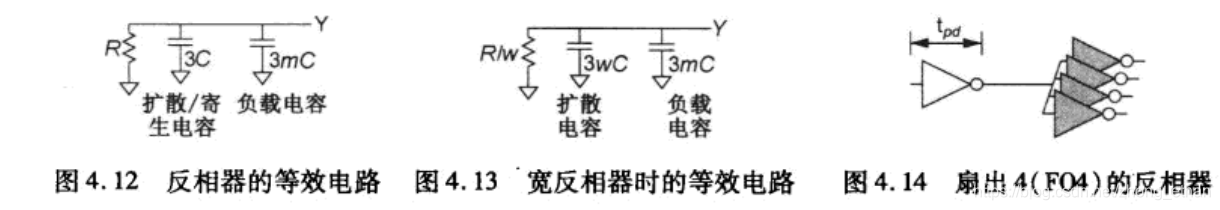

该公式可由Elmore延时公式推出。参考下面例子,图中是一个反相器驱动m个单位反相器,下降沿跳变时的等效电路:

图4.12是一个单位反相器驱动m个单个反相器,根据Elmore公式 ,延时 = (3C+3mC)R = 3RC + 3mRC;

图4.13是一个沟道宽度w倍单位尺寸的反相器驱动m个单位反相器,延时 = (3wC + 3mC)R/w = 3RC + 3m/w RC;

定义扇出h为负载电容与输入电容之比,负载电容为3mC,输入电容为3wC,扇出h = m/w。

定义理想反相器的延时 t = 3RC,则归一化延时 t = 1 + h。

寄生延时

寄生延时是门驱动零负载时的延时。假设晶体管的宽度选择成是每个门的电阻均为R,那么反相器的输出端上有三个单位的扩散电容,所以一个反相器的寄生延时为 τ = 3 R C \tau=3RC τ=3RC。把 τ \tau τ 作为一个单位,那么反相器的归一化寄生延时为1。反相器的归一化延时为

d = h + 1 d = h +1 d=h+1

一个三输入与非门的归一化延时为:

d = ( 5 / 3 ) h + 3 d = (5/3) h +3 d=(5/3)h+3

下面计算n输入与非门的寄生延时。注意这里是寄生延时,非总的延时,也非归一化延时。

输出节点上,n个PMOS管贡献 2 n C 2nC 2nC个电容,最相邻的NMOS贡献 n C nC nC个电容。当输入为1时,除了使输出节点上的电容放电以外,还必须使所有内部节点上的扩散电容放电。它的Elmore延时为:

输出节点上,n个PMOS管贡献 2 n C 2nC 2nC个电容,最相邻的NMOS贡献 n C nC nC个电容。当输入为1时,除了使输出节点上的电容放电以外,还必须使所有内部节点上的扩散电容放电。它的Elmore延时为:

t p d = R ( 3 n C ) + ∑ i = 1 n − 1 ( i R n ) ( n C ) = ( n 2 2 + 5 2 n ) R C t_{pd}=R(3nC) + \sum_{i=1}^{n-1} (\frac{iR}{n})(nC)=(\frac{n^2}{2}+\frac{5}{2}n)RC tpd=R(3nC)+∑i=1n−1(niR)(nC)=(2n2+25n)RC

路径逻辑努力

使一个具有特定功能电路的延时最小是我们的最终目的。对于一个多级网络的延时,路劲延时D是各个延时的和。

D = ∑ d i = D F + P D = \sum d_i = D_{F} +P D=∑di=DF+P

D F = ∑ f i D_F = \sum f_i DF=∑fi

P = ∑ P i P = \sum P_i P=∑Pi

路径努力延时是各级努力的和。当一组数的积是常数时,这组数的和在选择所有的数都相等时达到最小,也就是说,当路劲中的各级都承担相同的努力时,路劲延时达到最小。

定义路劲努力F为路径逻辑努力,电气努力和分支努力的积。

F = G B H F=GBH F=GBH

路径逻辑努力定义为:

G = ∏ g i G = \prod g_{i} G=∏gi

路径电气努力H定义为该路径必须驱动的输出电容除以该路径表现出的输入电容:

H = C o u t ( p a t h ) C i n ( p a t h ) H=\frac{C_{out}(path)}{C_{in}(path)} H=Cin(path)Cout(path)

路径分支努力B是各级间分支努力的积:

B = ∏ b i B = \prod b_i B=∏bi

b = = C o n p a t h + C o f f n p a t h C o n p a t h b= =\frac{C_{onpath}+C_{offnpath}}{C_{onpath}} b==ConpathConpath+Coffnpath

各级努力的积是F,与门的尺寸无关。如果一个路径有N级,并且每级承担相同的努力,那么这一努力必定是:

f i = g i b i = F 1 / N f_i = g_i b_i = F^{1/N} fi=gibi=F1/N

路径的最小延时为:

D = N F 1 / N + P D=NF^{1/N}+P D=NF1/N+P

同时,选择门的尺寸以达到这一最小延时也很方便,我们只要知道一个门所驱动的输出电容,就可以求出这个门的最佳输入电容:

C i n = C o u t × g i f i C_{in}=\frac{C_{out}\times g_i}{f_i} Cin=fiCout×gi

我们可以从路径末端的负载开始,右后向前的应用电容转换公式来决定每级的尺寸。

选择最优级数

在一个路径的末端添加反相器可以不改变他的功能。我们计算一下应当添加多少个反相器可以使延时最小。现有 n 1 n_1 n1级逻辑块,路径努力为F,添加 N − n 1 N-n_1 N−n1个反相器使总级数为N级。新路径延时为:

D = N F 1 / N + ∑ i = 1 n 1 p i + ( N − n 1 ) P i n v D=NF^{1/N}+\sum_{i=1}^{n_1}p_i+(N-n_1)P_{inv} D=NF1/N+∑i=1n1pi+(N−n1)Pinv

p i n v p_{inv} pinv为反相器寄生延时,当为1时,对上述公式求导并使导数为0,得到最优单级努力为3.59。也就是说,当路径设计成 N = l o g 4 F N=log_{4}F N=log4F个级数时延时最小。

小结

应用逻辑努力的方法步骤如下:

(1)计算路径努力 F = G B H F=GBH F=GBH

(2)估算最优级数 N = l o g 4 F N = log_4 F N=log4F

(3)估算最小延时 D = N F 1 / N + P D=NF^{1/N}+P D=NF1/N+P

(4)确定最优单级努力 f = F 1 / N f=F^{1/N} f=F1/N

(5)从路径末端开始,右后向前计算各级尺寸 C i n = C o u t × g i f i C_{in}=\frac{C_{out}\times g_i}{f_i} Cin=fiCout×gi

附录 DC综合

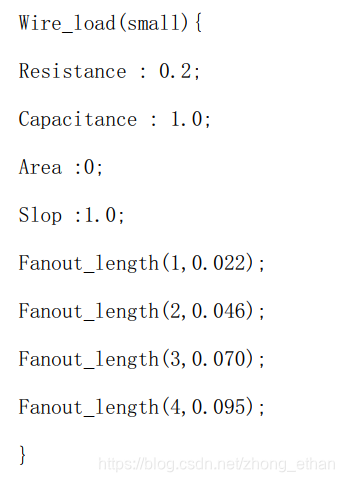

DC是基于路径分析的,每个路径上有cell延时和wire延时。对于cell延时,dc是根据input_transition和out_load对应的查找表来计算的;对于wire延时,dc是根据wire_load_model中的fanout_length,resistance,capacitance以及area来计算的。

查找表长这个样子