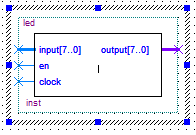

12)led部分

library ieee;

use ieee.std_logic_1164.all;

entity led is

port(input:in std_logic_vector(7 downto 0):="ZZZZZZZZ";

en:in std_logic;

clock:in std_logic;

output:out std_logic_vector(7 downto 0):="ZZZZZZZZ"

);

end led;

architecture st of led is

signal i:std_logic_vector(7 downto 0):="ZZZZZZZZ";

begin

process(en,clock)

begin

if (en='1' and clock='0') then--rising_edge(clock)

i<=input;

else

i<="ZZZZZZZZ";

end if;

end process;

output<=i;

end st;

接口设计:

Clock:时钟信号

en:使能信号

input:输入信号

output:输出信号

功能实现:

存储总线上输出的led_out的值,并将其进行输出。在执行led_out指令的时候输出总线上的值,否则就输出高阻态。

仿真验证:

与cpu在同一文件中,与cpu同仿真。

下篇点此