SPI, the abbreviation of English Serial Peripheral Interface, as the name suggests is the serial peripheral interface. SPI, is a high-speed, full-duplex, synchronous communication bus, and only occupies four lines on the pins of the chip, saving the pins of the chip, saving space on the PCB layout, providing convenience, positive Because of this simple and easy-to-use feature, more and more chips now integrate this communication protocol.

SPI is a ring bus structure composed of ss (cs), sck, sdi, and sdo. Its timing is actually very simple, mainly under the control of sck, two bidirectional shift registers exchange data.

Send on the rising edge, receive on the falling edge, and send the high bit first.

When the rising edge comes, the level on sdo will be sent to the register of the slave device.

When the falling edge comes, the level on sdi will be received into the register of the master device.

Assuming that the master and slave are ready for initialization: and the master's sbuff=0xaa (10101010) and the slave's sbuff=0x55 (01010101), the following will demonstrate the data situation of the 8 clock cycles of the spi step by step (assuming the rising edge sends data ).

-------------------------------------------------- -pulse

master sbuff slave sbuff sdi sdo

----------------------------------------- ----------

0 00-0 1 0101010 0 1010101 0 0

------------------------------ ---------------------

1 0--1 0 101010x 1010101 1 0 1 1 1--0 0101010 0

1 0101011 0 1 ------- --------------------------------------------

2 0--1 1010100x 01010110 102 1--0 10101001010101101

0

---------------------------------------------------

3 0--1 0101001x 10101101 013 1--0 01010010101011010

1

---------------------------------------------------

4 0--1 1010010x 01011010 104 1--0 10100101010110101

0

---------------------------------------------------

5 0--1 0100101x 10110101 0 1

5 1--0 01001010 10110101 0 1

---------------------------------------------------

6 0--1 1001010x 01101010 1 0

6 1--0 10010101 01101010 1 0

---------------------------------------------------

7 0--1 0010101x 11010101 0 1

7 1--0 00101010 11010101 0 1

---------------------------------------------------

8 0--1 0101010x 10101010 1 0

8 1--0 01010101 10101010 1 0

---------------------------------------------------

这样就完成了两个寄存器8位的交换,上面的0--1表示上升沿、1--0表示下降沿,sdi、 sdo相对于主机而言的。根据以上分析,一个完整的传送周期是16位,即两个字节,因为,首先主机要发送命令过去,然后从机根据主机的名准备数据,主机在下一个8位时钟周期才把数据读回来。

SPI总线是Motorola公司推出的三线同步接口,同步串行3线方式进行通信:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于 CPU与各种外围器件进行全双工、同步串行通讯。

SPI总线有四种工作方式(SP0, SP1, SP2, SP3),其中使用的最为广泛的是SPI0和SPI3方式。

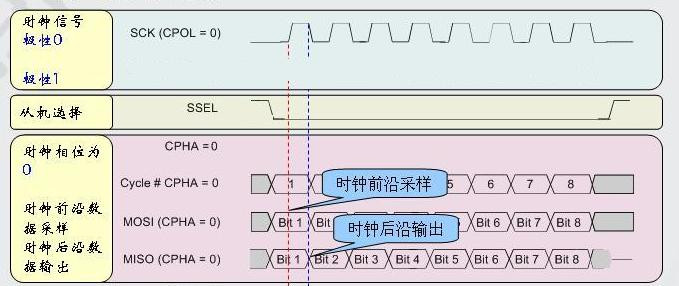

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。如果 CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。 SPI主模块和与之通信的外设音时钟相位和极性应该一致。

SPI时序图详解-SPI接口在模式0下输出第一位数据的时刻

SPI接口在模式0下输出第一位数据的时刻

SPI接口有四种不同的数据传输时序,取决于CPOL和CPHL这两位的组合。图1中表现了这四种时序,

时序与CPOL、CPHL的关系也可以从图中看出。

CPOL是用来决定SCK时钟信号空闲时的电平,CPOL=0,空闲电平为低电平,CPOL=1时,

空闲电平为高电平。CPHA是用来决定采样时刻的,CPHA=0,在每个周期的第一个时钟沿采样,

CPHA=1,在每个周期的第二个时钟沿采样。

只关注模式0的时序。

我们来关注SCK的第一个时钟周期,在时钟的前沿采样数据(上升沿,第一个时钟沿),

在时钟的后沿输出数据(下降沿,第二个时钟沿)。首先来看主器件,主器件的输出口(MOSI)输出的数据bit1,

在时钟的前沿被从器件采样,那主器件是在何时刻输出bit1的呢?bit1的输出时刻实际上在SCK信号有效以前,

比 SCK的上升沿还要早半个时钟周期。bit1的输出时刻与SSEL信号没有关系。再来看从器件,

主器件的输入口MISO同样是在时钟的前沿采样从器件输出的bit1的,那从器件又是在何时刻输出bit1的呢。

从器件是在SSEL信号有效后,立即输出bit1,尽管此时SCK信号还没有起效。关于上面的主器件

和从器件输出bit1位的时刻,可以从图3、4中得到验证。

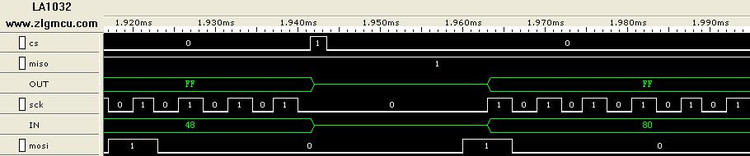

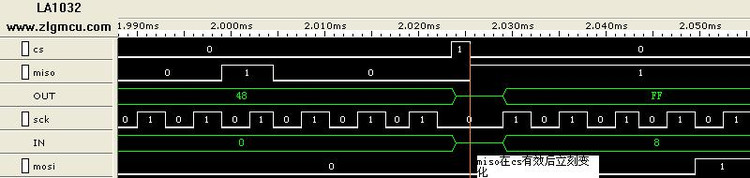

注意图3中,CS信号有效后(低电平有效,注意CS下降沿后发生的情况),故意用延时程序

延时了一段时间,之后再向数据寄存器写入了要发送的数据,来观察主器件输出bit1的情况(MOSI)。

可以看出,bit1(值为1)是在SCK信号有效之前的半个时钟周期的时刻开始输出的(与CS信号无关),

到了SCK的第一个时钟周期的上升沿正好被从器件采样。

图4中,注意看CS和MISO信号。我们可以看出,CS信号有效后,从器件立刻输出了bit1(值为1)。

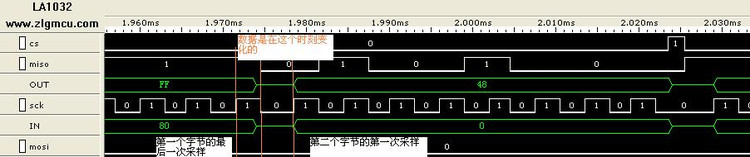

通常我们进行的spi操作都是16位的。图5记录了第一个字节和第二个字节间的相互衔接的过程。

第一个字节的最后一位在SCK的上升沿被采样,随后的SCK下降沿,从器件就输出了第二个字节的第一位。

SPI总线协议介绍(接口定义,传输时序)

一、技术性能

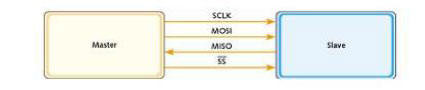

SPI接口是Motorola 首先提出的全双工三线同步串行外围接口,采用主从模式(Master Slave)架构;支持多slave模式应用,一般仅支持单Master。

时钟由Master控制,在时钟移位脉冲下,数据按位传输,高位在前,低位在后(MSB first);SPI接口有2根单向数据线,为全双工通信,目前应用中的数据速率可达几Mbps的水平。

-------------------------------------------------------

二、接口定义

SPI接口共有4根信号线,分别是:设备选择线、时钟线、串行输出数据线、串行输入数据线。

(2)MISO:主器件数据输入,从器件数据输出

(3)SCLK :时钟信号,由主器件产生

(4)/SS:从器件使能信号,由主器件控制

-------------------------------------------------------

三、内部结构