The digitization of a signal requires three steps: sampling, quantization and coding. Sampling refers to replacing the original continuous signal in time with a sequence of signal samples at regular intervals, that is, discretizing the analog signal in time. Quantization uses a finite number of amplitude values to approximate the original continuously changing amplitude value, changing the continuous amplitude of the analog signal into a limited number of discrete values with a certain interval. Encoding is to use binary numbers to represent the quantized value according to a certain rule, and then convert it into a binary or multi-valued digital signal stream. The above-mentioned digitization process is also called pulse code modulation.

Discuss here two methods of FPGA realization of signal generator :

First, use the IP core RAM core or ROM core integrated on FPGA to realize the generation of sine wave signal.

1. Use MATLAB to compile mif files or directly use Mif_Maker2010 to generate mif files:

first, MATLAB realizes signal generation and mif file generation

clc,clear;

N=2^8; %N为采样点数

s_p=0:255;%正弦波一个周期的采样点数

sin_data=sin(2*pi*s_p/N); %sin_data是初步采样值,浮点数% 编写到这里,大家可以在任务行中显示此时的波形

fix_p_sin_data=fix(sin_data*127); %定点化 fix()函数可以直接去除小数点后的值,使之成为整数

for i=1:N

fix_p_sin_data(i) = N/2+fix_p_sin_data(i)

end%下面是mif文件固定格式,不可更改

fid=fopen('E:\FPGA\1_Verilog\sin\sp_ram_256x8.mif','w+');

fprintf(fid,'WIDTH=8;\n');

fprintf(fid,'DEPTH=256;\n');

fprintf(fid,'ADDRESS_RADIX=UNS;\n');

fprintf(fid,'DATA_RADIX=UNS;\n');

fprintf(fid,'CONTENT BEGIN \n');

for i=1:N

fprintf(fid,'%d:%d; \n',i-1,fix_p_sin_data(i));

end

fprintf(fid,'END; \n');

fclose(fid);The above MATLAB code realizes one cycle of a sine wave and generates a mif file of this sine wave. The generated mif file has a width of 8 and a depth of 256, which is used in the subsequent design of RAM core and ROM core. The generated mif file can be viewed in the two forms of Quertus II core text as shown in the figure below. It

should be noted that the generated mif file can only be an unsigned integer, because it is a digital signal generator, which can only achieve integer signal processing.

The next step is to use Mif_Maker2010 to generate a mif file, which I will put after the text.

Realize waveform generation through global parameter settings. Then save as a mif file to generate a mif file containing the waveform.

2. The generation of RAM core and ROM core

First establish a sin project, and then start the establishment of IP core

This is to select the type of rhodopsin nuclear memory, as well as the width and depth of ram or rom, which should correspond to the previous mif file.

This is to select the type of rhodopsin nuclear memory, as well as the width and depth of ram or rom, which should correspond to the previous mif file.

Here, select the previously generated mif file as the data contained in the memory. It should be noted that it is best to put the generated mif file in the project directory, otherwise it will have a great impact on the subsequent simulation. (Lesson of blood, it took me 8 hours to find out the reason. I will talk about

it later.) Everything I didn’t talk about before is directly next, and finally finish, the generation of a rom core with a width of 8 bits for address and data bits is completed. , The process of RAM core generation is consistent with this process, so I won’t repeat it here.

3. Next, we mainly look at the following two files

首先是inst文件

rom1port rom1port_inst (

.address ( address_sig ),

.clock ( clock_sig ),

.q ( q_sig )

);

这是一个例化过程的模板,直接拷贝,修改接口即可完成对rom核的例化。

接下来是rom1port.v文件

// synopsys translate_off

`timescale 1 ps / 1 ps

// synopsys translate_on

module rom1port (

address,

clock,

q);

input [7:0] address;

input clock;

output [7:0] q;

`ifndef ALTERA_RESERVED_QIS

// synopsys translate_off

`endif

tri1 clock;

`ifndef ALTERA_RESERVED_QIS

// synopsys translate_on

`endif

wire [7:0] sub_wire0;

wire [7:0] q = sub_wire0[7:0];

altsyncram altsyncram_component (

.address_a (address),

.clock0 (clock),

.q_a (sub_wire0),

.aclr0 (1'b0),

.aclr1 (1'b0),

.address_b (1'b1),

.addressstall_a (1'b0),

.addressstall_b (1'b0),

.byteena_a (1'b1),

.byteena_b (1'b1),

.clock1 (1'b1),

.clocken0 (1'b1),

.clocken1 (1'b1),

.clocken2 (1'b1),

.clocken3 (1'b1),

.data_a ({

8{

1'b1}}),

.data_b (1'b1),

.eccstatus (),

.q_b (),

.rden_a (1'b1),

.rden_b (1'b1),

.wren_a (1'b0),

.wren_b (1'b0));

defparam

altsyncram_component.address_aclr_a = "NONE",

altsyncram_component.clock_enable_input_a = "BYPASS",

altsyncram_component.clock_enable_output_a = "BYPASS",

altsyncram_component.init_file = "sp_ram_256x8.mif",

altsyncram_component.intended_device_family = "Cyclone IV E",

altsyncram_component.lpm_hint = "ENABLE_RUNTIME_MOD=NO",

altsyncram_component.lpm_type = "altsyncram",

altsyncram_component.numwords_a = 256,

altsyncram_component.operation_mode = "ROM",

altsyncram_component.outdata_aclr_a = "NONE",

altsyncram_component.outdata_reg_a = "CLOCK0",

altsyncram_component.widthad_a = 8,

altsyncram_component.width_a = 8,

altsyncram_component.width_byteena_a = 1;

endmodule

// ============================================================

// CNX file retrieval info

// ============================================================

// Retrieval info: PRIVATE: ADDRESSSTALL_A NUMERIC "0"

// Retrieval info: PRIVATE: AclrAddr NUMERIC "0"

// Retrieval info: PRIVATE: AclrByte NUMERIC "0"

// Retrieval info: PRIVATE: AclrOutput NUMERIC "0"

// Retrieval info: PRIVATE: BYTE_ENABLE NUMERIC "0"

// Retrieval info: PRIVATE: BYTE_SIZE NUMERIC "8"

// Retrieval info: PRIVATE: BlankMemory NUMERIC "0"

// Retrieval info: PRIVATE: CLOCK_ENABLE_INPUT_A NUMERIC "0"

// Retrieval info: PRIVATE: CLOCK_ENABLE_OUTPUT_A NUMERIC "0"

// Retrieval info: PRIVATE: Clken NUMERIC "0"

// Retrieval info: PRIVATE: IMPLEMENT_IN_LES NUMERIC "0"

// Retrieval info: PRIVATE: INIT_FILE_LAYOUT STRING "PORT_A"

// Retrieval info: PRIVATE: INIT_TO_SIM_X NUMERIC "0"

// Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Cyclone IV E"

// Retrieval info: PRIVATE: JTAG_ENABLED NUMERIC "0"

// Retrieval info: PRIVATE: JTAG_ID STRING "NONE"

// Retrieval info: PRIVATE: MAXIMUM_DEPTH NUMERIC "0"

// Retrieval info: PRIVATE: MIFfilename STRING "../../sp_ram_256x8.mif"

// Retrieval info: PRIVATE: NUMWORDS_A NUMERIC "256"

// Retrieval info: PRIVATE: RAM_BLOCK_TYPE NUMERIC "0"

// Retrieval info: PRIVATE: RegAddr NUMERIC "1"

// Retrieval info: PRIVATE: RegOutput NUMERIC "1"

// Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "0"

// Retrieval info: PRIVATE: SingleClock NUMERIC "1"

// Retrieval info: PRIVATE: UseDQRAM NUMERIC "0"

// Retrieval info: PRIVATE: WidthAddr NUMERIC "8"

// Retrieval info: PRIVATE: WidthData NUMERIC "8"

// Retrieval info: PRIVATE: rden NUMERIC "0"

// Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all

// Retrieval info: CONSTANT: ADDRESS_ACLR_A STRING "NONE"

// Retrieval info: CONSTANT: CLOCK_ENABLE_INPUT_A STRING "BYPASS"

// Retrieval info: CONSTANT: CLOCK_ENABLE_OUTPUT_A STRING "BYPASS"

// Retrieval info: CONSTANT: INIT_FILE STRING "../../sp_ram_256x8.mif"

// Retrieval info: CONSTANT: INTENDED_DEVICE_FAMILY STRING "Cyclone IV E"

// Retrieval info: CONSTANT: LPM_HINT STRING "ENABLE_RUNTIME_MOD=NO"

// Retrieval info: CONSTANT: LPM_TYPE STRING "altsyncram"

// Retrieval info: CONSTANT: NUMWORDS_A NUMERIC "256"

// Retrieval info: CONSTANT: OPERATION_MODE STRING "ROM"

// Retrieval info: CONSTANT: OUTDATA_ACLR_A STRING "NONE"

// Retrieval info: CONSTANT: OUTDATA_REG_A STRING "CLOCK0"

// Retrieval info: CONSTANT: WIDTHAD_A NUMERIC "8"

// Retrieval info: CONSTANT: WIDTH_A NUMERIC "8"

// Retrieval info: CONSTANT: WIDTH_BYTEENA_A NUMERIC "1"

// Retrieval info: USED_PORT: address 0 0 8 0 INPUT NODEFVAL "address[7..0]"

// Retrieval info: USED_PORT: clock 0 0 0 0 INPUT VCC "clock"

// Retrieval info: USED_PORT: q 0 0 8 0 OUTPUT NODEFVAL "q[7..0]"

// Retrieval info: CONNECT: @address_a 0 0 8 0 address 0 0 8 0

// Retrieval info: CONNECT: @clock0 0 0 0 0 clock 0 0 0 0

// Retrieval info: CONNECT: q 0 0 8 0 @q_a 0 0 8 0

// Retrieval info: GEN_FILE: TYPE_NORMAL rom1port.v TRUE

// Retrieval info: GEN_FILE: TYPE_NORMAL rom1port.inc TRUE

// Retrieval info: GEN_FILE: TYPE_NORMAL rom1port.cmp TRUE

// Retrieval info: GEN_FILE: TYPE_NORMAL rom1port.bsf TRUE

// Retrieval info: GEN_FILE: TYPE_NORMAL rom1port_inst.v TRUE

// Retrieval info: GEN_FILE: TYPE_NORMAL rom1port_bb.v TRUE

// Retrieval info: LIB_FILE: altera_mf

通过查看信息,可以看到rom核设置的一些信息,我那个仿真不出结果就是在这里的mif文件位置查到不在工程文件夹下,才找到的原因。3. Top file design

/* time: 2020.9.1

主要功能:实现正弦信号的产生,可以通过对信号的地址加的数字修改输出信号的频率

端口定义: clock:时钟信号

reset:复位信号

o_wave:输出信号

==================================================================*/

module sin(clock, reset, o_wave);

input clock, reset;

output [7:0] o_wave;

reg [7:0] addr;

wire [7:0] o_wave;

always @(posedge clock or negedge reset)begin

if(!reset)

begin

addr <= 8'b0;

end

else

begin

addr <= addr + 8'd2; //修改这里可以修改输出的频率

end

end

rom1port rom1port_inst (

.address ( addr ),

.clock ( clock ),

.q ( o_wave )

);

endmodule

The RTL circuit is shown in the figure below. The

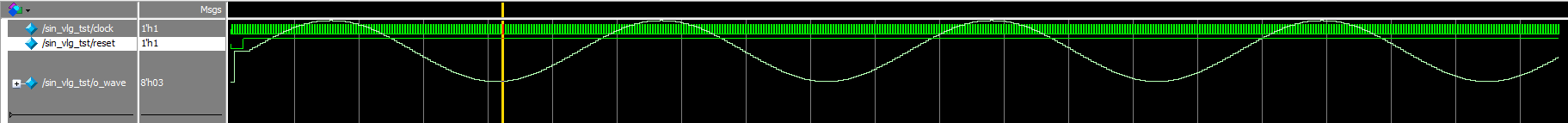

simulation circuit is shown in the figure below:

here it is better to use co-simulation, because manual simulation will cause problems and will output high impedance. For manual simulation, please refer to another document reproduced by me:

2. NCO (Numerically Controlled Oscillator)

2. NCO (Numerically Controlled Oscillator)

Use the IP core to set, automatically generate and then instantiate the IP core with the top file.

Disclaimer: This article is only suitable for learning, and its content contains excerpts and summaries from the book. We welcome everyone to add and make progress together.