作为一名系统软件工程师,需要对verilog语言有一定的了解,学习verilog过程中免不了要进行仿真。工程上常见的verilog仿真软件基本就是国外EDA三大厂的:Mentor公司的ModelSim,cadence公司的NC-Sim/NC-Verilog和Synopsys公司的VCS。

对于个人学习来讲,这些收费的大型软件并不是很适合。在此推荐一款轻量版的verilog仿真平台,很适合初学者及小型化仿真需求者:Icarus Verilog + gtkwave。前者可以认为是个仿真器,后者是个看波形的软件。

Icarus Verilog开源,可支持windows和linux。官网下载地址: http://bleyer.org/icarus/

Icarus Verilog的详细使用教程 如下:

Windows环境

-

安装软件: 软件下载地址 http://bleyer.org/icarus/

新版本中软件带的有gtkwave。安装时,会默认安装。

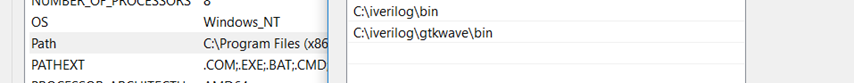

安装后,确认iverilog是否已经添加到系统变量中,如果没有,则手动添加一下 C:\iverilog\gtkwave\bin 和 C:\iverilog\bin (此处默认安装在C盘)

Windows下也可以免安装,直接将别人的安装文件拷贝过来也能用。但也需要在系统变量里添加安装文件的路径。

-

编写 Verilog代码和testbench。文章最后为一个应用实例。

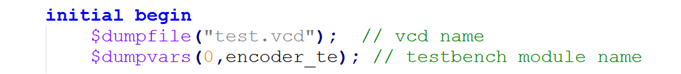

注意:testbench中需要以下两句,这两行主要是给gtkwave这个工具使用的,具体含义参考

https://zhidao.baidu.com/question/13428173.html

-

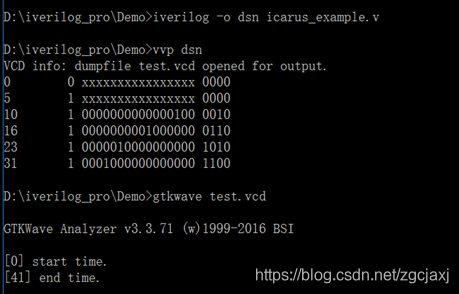

编译仿真

a) Windows系统下,win +R ,输入cmd 打开命令行; cd 进入 .v文件所在的文件夹(此步骤也可以省略,但在b步骤中需要指定 文件路径)

b) 执行 iverilog -o dsn icarus_example.v得到文件dsn. (此处是将testbench和verilog源代码写在了同一个.v文件中 )

c) 执行 vvp dsn

-

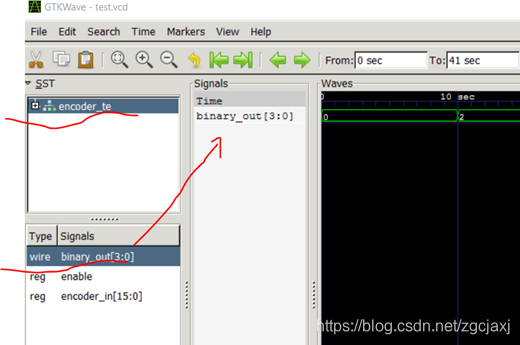

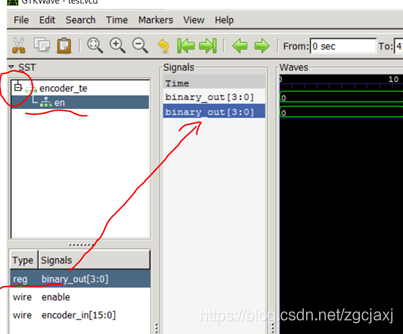

用gtkwave打开vcd仿真波形

a) 执行 gtkwave test.vcd (vcd的名字是在testbench中命名的,此处为 test.vcd) 打开仿真波形

Ubuntu 环境

- 下载并安装软件,需要联网。在root权限下,

执行 apt-get install Verilog

执行 apt-get install gtkwave - 编写 Verilog代码和testbench。

- 编译仿真 (同window环境)

a) 执行 iverilog -o dsn icarus_example.v得到文件dsn.

b) 执行 vvp dsn - 用gtkwave打开vcd仿真波形

a) 执行 gtkwave test.vcd (vcd的名字是在testbench中命名的,此处为 test.vcd) 打开仿真波形

附例源码 icarus_example.v

module encoder(binary_out,encoder_in,enable);

output [3:0] binary_out;

input enable;

input [15:0] encoder_in;

reg [3:0] binary_out;

always @ (enable or encoder_in)

begin

binary_out = 0;

if(enable) begin

if(encoder_in == 16'h0002) begin

binary_out = 1;

end if(encoder_in == 16'h0004) begin

binary_out = 2;

end if(encoder_in == 16'h0008) begin

binary_out = 3;

end if(encoder_in == 16'h0010) begin

binary_out = 4;

end if(encoder_in == 16'h0020) begin

binary_out = 5;

end if(encoder_in == 16'h0040) begin

binary_out = 6;

end if(encoder_in == 16'h0080) begin

binary_out = 7;

end if(encoder_in == 16'h0100) begin

binary_out = 8;

end if(encoder_in == 16'h0200) begin

binary_out = 9;

end if(encoder_in == 16'h0400) begin

binary_out = 10;

end if(encoder_in == 16'h0800) begin

binary_out = 11;

end if(encoder_in == 16'h1000) begin

binary_out = 12;

end if(encoder_in == 16'h2000) begin

binary_out = 13;

end if(encoder_in == 16'h4000) begin

binary_out = 14;

end if(encoder_in == 16'h8000) begin

binary_out = 15;

end

end

end

endmodule

module encoder_te();

reg enable;

reg [15:0] encoder_in;

wire [3:0] binary_out;

initial begin

$dumpfile("test.vcd"); // vcd name

$dumpvars(0,encoder_te); // testbench module name

$monitor("%g\t %b %b %b",

$time,enable,encoder_in,binary_out);

enable = 0;

#5 enable = 1;

#5 encoder_in = 16'h0004;

#6 encoder_in = 16'h0040;

#7 encoder_in = 16'h0400;

#8 encoder_in = 16'h1000;

#10 $finish;

end

encoder en(binary_out,encoder_in,enable);

endmodule

参考Wiki http://iverilog.wikia.com/wiki/Main_Page

参考 使用方法

http://www.cnblogs.com/zhuangzhuang1988/archive/2012/03/30/2425052.html