使用Modelsim仿真简单的Verilog文件,可分为以下几个步骤:

1 打开Modelsim

2 更改项目文件夹,建立项目

3 建立项目文件和测试文件

4 编译源文件

5 启动仿真、添加波形

下面以一个十进制计数器为例,建立仿真。

1 更改项目文件夹,并建立项目

2 在该项目下建立两个源文件,一个要仿真的源文件,一个是testbeach源文件

文件内容

//十进制计数器

module test(

input clk,

input nrst,//低电平同步复位

output reg [3:0] CNT

);

always @(posedge clk)

begin

if(!nrst)

CNT<=4'd0;

else

begin

if(CNT==4'd9)

CNT=4'd0;

else CNT<=CNT+1'd1;

end

end

endmoduletestbeach

`timescale 1ns/1ns

module test_tb();

reg clk;

reg rst;

wire [3:0] CNT;

test i1

(

.clk(clk),

.nrst(rst),

.CNT(CNT)

);

initial

begin

clk = 0;

rst = 0;

#100

rst = 1;

#10000;

$stop;

end

always #20 clk = ~clk;

endmodule

3 在项目目录下,空白处右键选择compile all

4 在Library目录下面,选择work下的test_tb(自己建立的testbe文件)右键选择仿真

5 等待仿真界面弹出,添加信号

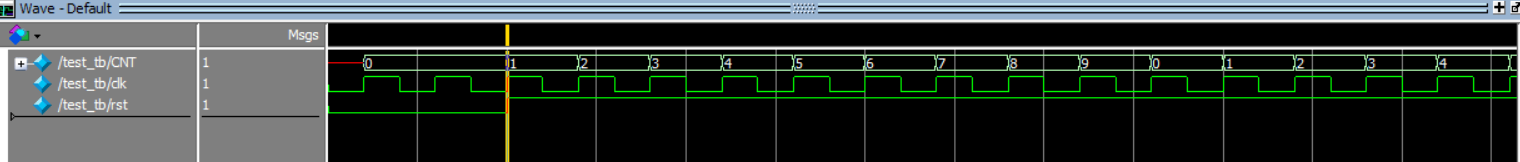

5 电机run -all 分析波形信号

6 仿真波形