由于前面文章已经讲解了ip的使用方式,此文讲解利用PLL核产生相位可调的时钟信号,以及IO delay原语,这些在高速接口中经常用到。注意此文针对的是ECP5系列芯片。

一、利用PLL核产生相位可调的时钟信号

1)配置PLL核。

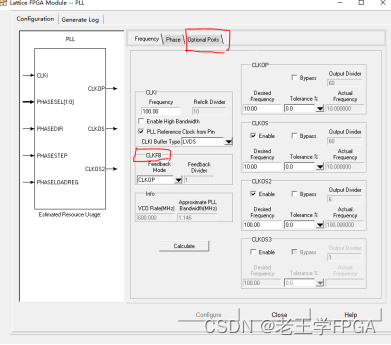

打开pll核配置界面如下所示,使能需要的时钟信号,设置输入时钟频率以及相应的输出时钟频率。(其中要注意CLKFB选项,待动态调整相位的时钟不能作为此选项的配置,这里我们选择CLKOS作为待调整时钟,此时CLKFB选项可选为CLKOP),点击OptionalPorts,进入动态相位调整使能选项。

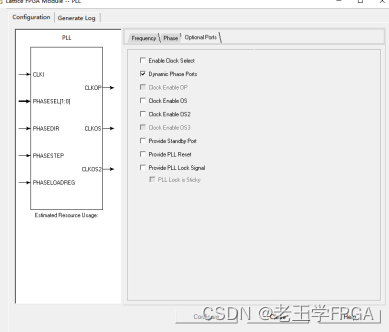

如下,勾选动态相位端口,左侧显示了PLL模块端口示意图。

2)参数配置与例化

配置完pll后,在Hierarchy 窗口找到创建的PLL核,右击>Goto sourace definition ,打开pll的HDL文件,进行顶层例化和参数配置。

创建的pll核HDL源码如下,源码包括了pll的端口和相关参数的定义,根据需要配置相关参数。在顶层中例化pll核,并按时序要求生成相关信号,综合后配置引脚,生成bit流即可。

3)主要信号\参数说明

端口信号说明:

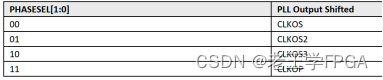

PHASESEL[1:0]信号为片选信号,决定使能哪一路输出时钟做动态相位调整。

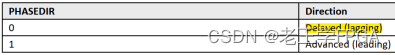

PHASEDIR 决定了相位要调整成“超前”还是”滞后”。

PHASESTEP和PHASELOADREG分别是两种工作模式下触发信号,下降沿有效。

如下,设置PHASESEL不同的参数值,选择某一路时钟做相位调整(一个时间点只能调整一路时钟)。

如下,设置PHASEDIR不同参数值,选择相位调整的方向。

如下,如果选用PHASESTEP信号(下降沿触发)来触发相位调整,则遵循下面时序。

此种触发下,每次相移的步长(单位:度)由下面公式计算:

(CLKO<n>_FPHASE/(8*CLKO<n>_DIV)*360

n,代表待调整相位的时钟的下标,如CLKOP,这里n就是P

公式中的参数可在创建的PLL核的hdl文件中找到,CLKO<n>_DIV为软件自动计算的固定值,参数CLKO<n>_FPHASE可以根据自己需求调整

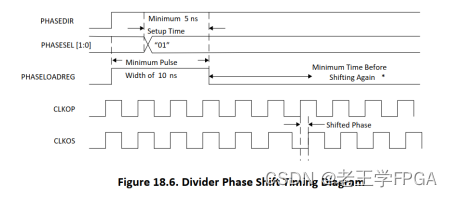

如下,如果选用PHASELOADREG信号(下降沿触发)来触发相位调整,则遵循下面时序。

此种触发下,每次相移的步长(单位:度)由下面公式计算:

[(CLKO<n>_CPHASE – CLKO<n>_DIV)/( CLKO<n>_DIV + 1)] * 360

n,代表待调整相位的时钟的下标。如CLKOP,这里n就是P

公式中的参数可在创建的PLL核的hdl文件中找到,CLKO<n>_DIV为软件自动计算的固定值,参数CLKO<n>_CPHASE可以根据自己需求调整

二、IO delay原语

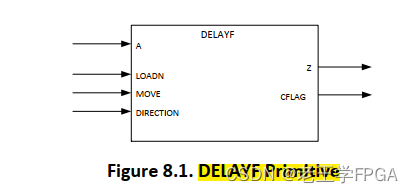

利用DELAYF原语可以将输入信号延时后输出,延时的最小单位为25ps,最大延时为127*25ps。

其模块示意图如下:

端口说明:

A 输入信号

LOADN 复位信号,对输入信号做动态延时调整时,此信号必须设为0

MOVE 延时动态调整触发信号,下降沿有效

DIRECTION 在MOVE下降沿被采集;置0时,增加对输入信号的延时,置1时减少对输入信号的延时

CFLAG 延时溢出标志,表示不能再增加延时了

原语:

module DELAYF (

input A, LOADN, MOVE, DIRECTION,

output Z, CFLAG );

parameter DEL_MODE = "USER_DEFINED";

parameter DEL_VALUE = 0;

endmodule

DEL_MODE: "ECLK_ALIGNED", "ECLK_CENTERED",

"ECLK_CENTERED_MIPI", "ECLK_CENTERED_SLVS", "SCLK_ALIGNED",

"SCLK_CENTERED", "SCLK_ZEROHOLD", "USER_DEFINED" (default)

DEL_VALUE :0-127