SRIO结构

【写在前面:在学习SRIO后续知识时发现有很多概念很难理解,查资料发现我对SRIO构架那部分学习太过敷衍,特此用一篇博文来学习交流一下SRIO构架。】

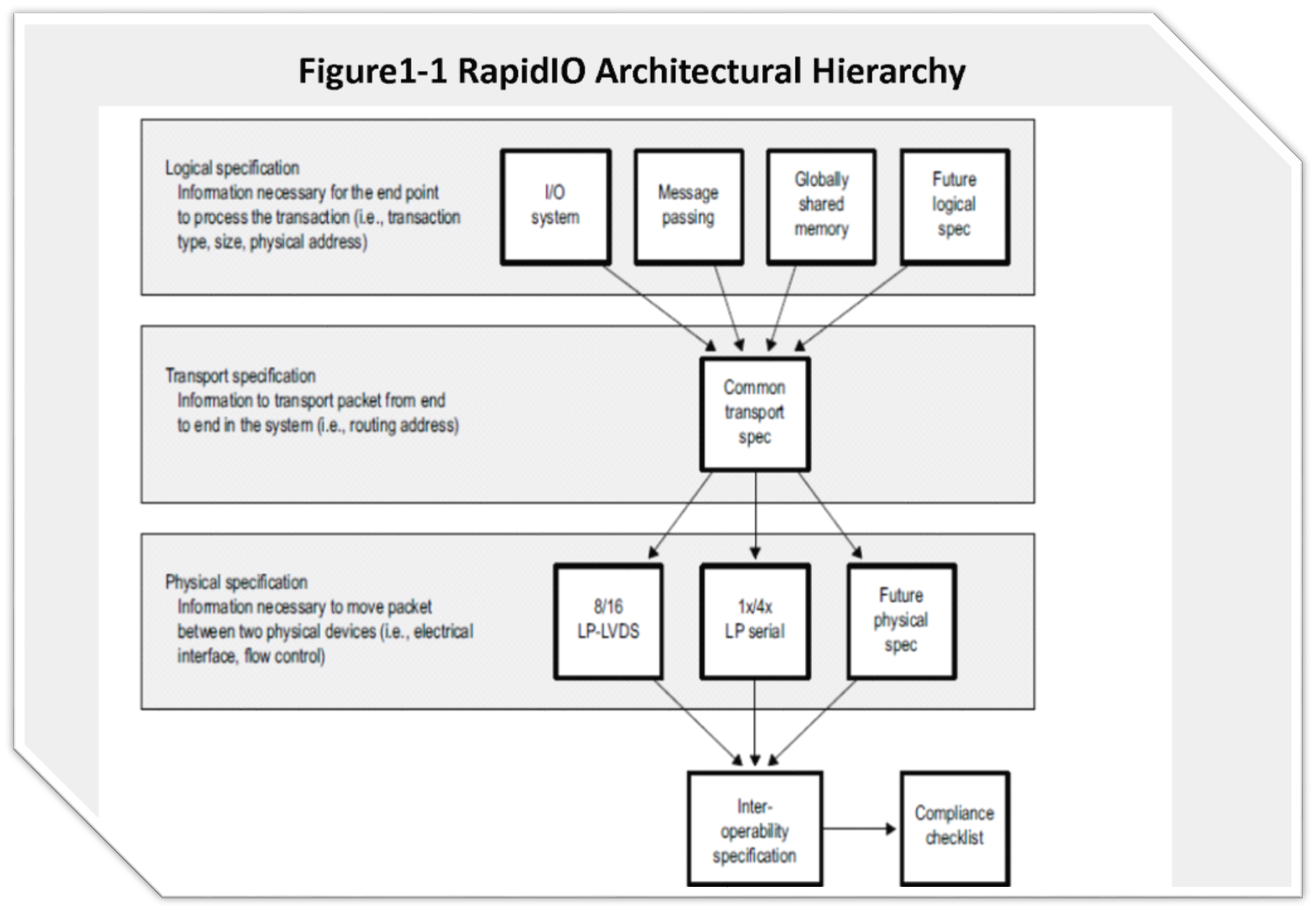

RapidIO层次构建

SRIO模块由三层构建而成。

逻辑层 确定终端处理传输的协议,包括包的格式。

传输层 定义了在系统中正确路由信息包的寻址方案。

物理层 包含设备级的接口信息,如电气特性、错误管理数据和基本的流量控制数据。

传输层与逻辑层和物理层是上下兼容的。

Figure1-1说明了RapidIO各层之间的关系。

逻辑层包含终端处理传输(transaction)的必要信息,如传输类型、大小、物理地址。

传输层包含系统中终端相互传输包(packet)的信息,如寻址。

物理层包含物理设备之间相互传递包(packet)时所需的信息,如电接口,流的控制。

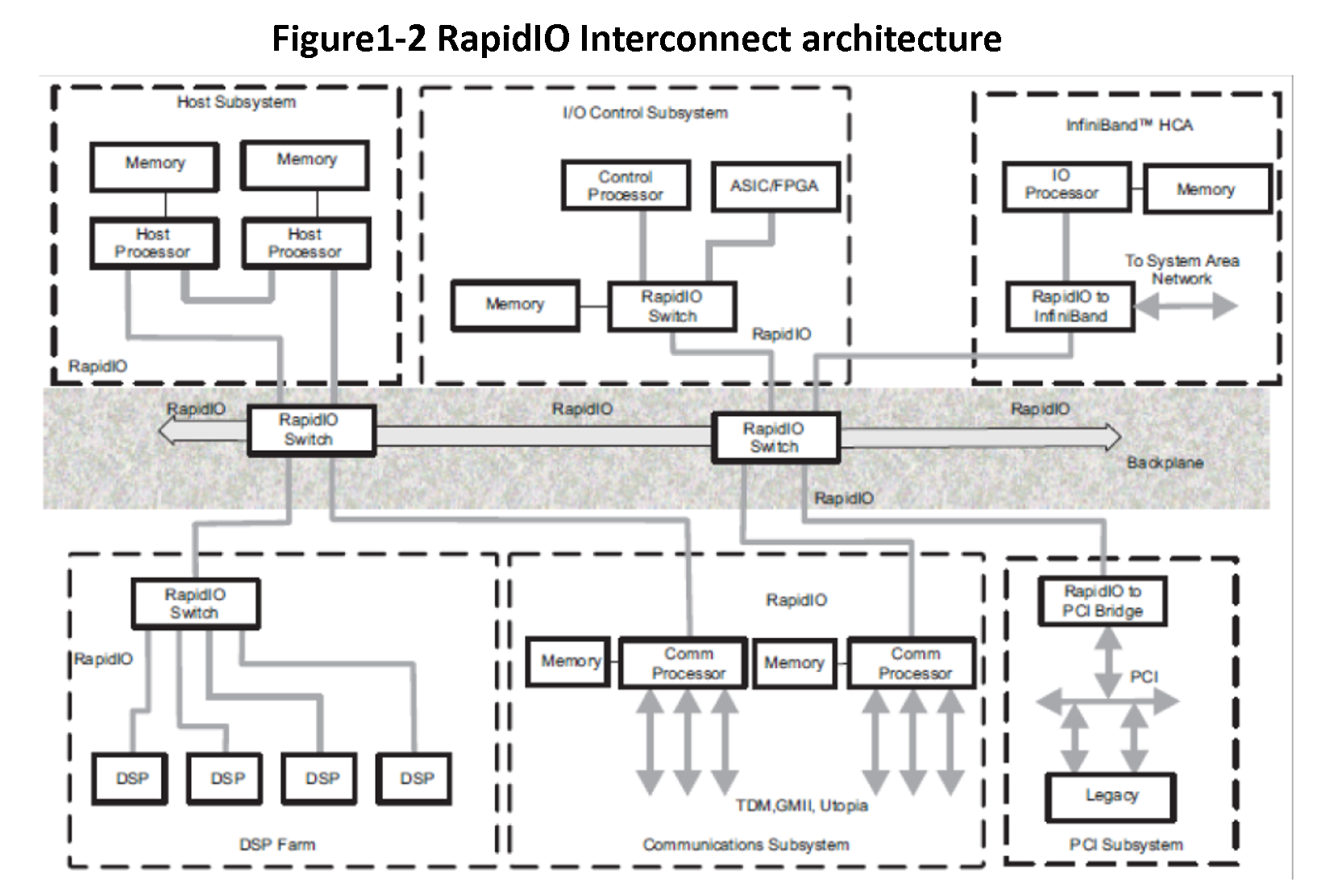

RapidIO互联结构

RapidIO的互连结构被定义为一个独立于物理层实现的分组交换协议。

Figure1-2显示的是SRIO互联系统。

图中可以看到,RapidIO遍布各个模块。

物理层 1x/4x LP-Serial(长浮点串口) 规格

现在有两种SRIO贸易协会认可的物理层规格:

1、 8/16 LP-LVDS

2、 1x/4x LP-Serial

第一种规格是点对点同步时钟源DDR接口;第二种规格是点对点,交流耦合,时钟恢复接口。而且两种规格不兼容。

SRIO遵从第二种规格,即1x/4x LP-Serial规格,SRIO中的串行/解串技术也是由这种规格分配的。

该规格适用于4个频率点,即1.25,2.5,3.125和5Gbps,这定义了每个I/O差分对的总带宽。

有一个8位/ 10位编码方案,确保时钟恢复电路的充足的数据转换。由于8位/ 10位编码方案的开销,每个差分对各自的有效数据带宽是1,2,2.5,4 Gbps。SRIO只同时为1X和4X的port指定频率。

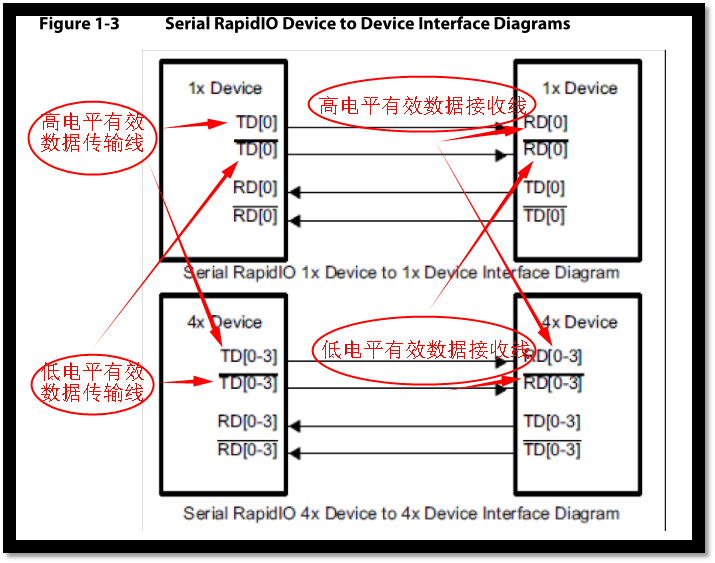

一个1X port被定义为一个TX(transanction)和一个RX(receive)的差分对。类似于一个IO口的差分对。4 X port就是4个1X的组合。一个4X port也可以被配置为4个1X port。

SRIO提供了支持从1G到16G带宽的可升级接口。

Figure1-3显示了怎样连接两个1X设备(或两个4X设备),一个设备的positive transmit data line (TDx) 【高电平有效传输数据线TDx】和另一个设备的positive receive data line (RDx)相连,低电平有效传输数据线 TDx和低电平有效接收数据线RDx相连。

SRIO中RapidIO支持的功能

以下是支持的功能:

1、遵从RapidIO互联协议REV2.1.1;

2、LP- Serial协议REV2.1.1;

3、4个可操作的1Xports;

2个可操作的2Xports,使用2Xport时可以用2个1Xport或1个2Xport;

1个可操作的4Xport,使用4Xport时可以用1个4Xport或4个1Xport;

4、在TI SerDes(串行/解串器)集成时钟恢复功能;

5、运行不同的port时使用不同的波特率,但是只支持倍频,比如2.5G和5G是支持的,但是3.125G和5G是不支持的;

6、硬件错误处理,包括CRC(循环冗余校验(Cyclic Redundancy Check, CRC));

7、差分CML(Current-Mode Logic 电流型逻辑(电路))信号支持AC和DC耦合;

8、能对不用的port进行掉电(powerdown);

9、支持1.25, 2.5, 3.125, and 5 Gbps rates;

10、支持读,写,写/反馈,流数据的写入,out-going Atomic(什么意思?外向原子?),维护操作;

11、向CPU产生中断(门铃包和内部调度);

12、支持8位和16位的设备ID;

13、支持接收34位的地址;

14、支持产生34位,50位和66位地址;

15、支持数据类型:位,半字,字,双字;

16、是BIG-ENDIAN(big endian是指低地址存放最高有效字节(MSB),与之对应的是small endian)模式的;

17、DirectIO传输;

18、消息(Message)传递;

19、数据payload最高256位;

20、单个消息最多包含16个包;

21、时钟域切换支持Elastic Store FIFO(FIFO弹性存储);

22、Short Run and Long Run compliant(不太懂,百度得到的结果只有经济学中的短期和长期,long run指的是不变成本和可变成本都能快速可变的时期,随着市场的自身的调节,市场的供求能达到平衡;short run是不变成本很难改变,商品的价格与不变成本具有粘滞性的时期;short和long是相对而言的,不一定short就比long小。T-T我不是在看DSP吗T_T?)

23、支持错误管理拓展;

24、支持拥挤(多个核同时访问同一地址)控制扩展;

25、支持多点ID;

26、支持长短控制符;

27、支持IDLE1和IDLE2;(IDLE为系统挂起命令,是为了节省系统消耗)

28、基于优先级和频率的严格优先级段交至协议单元;

以下是不支持的功能

1、不支持全局内存共享协议(GSM);

2、不兼容8/16 LP-LVDS规格;

3、不支持RapidIO原子操作目标;

规格

支持的两个REV2.1.1规格上面已经提到过了,不再赘述。

serial RapidIO AC specification(串行RapidIO交流协议)两种驱动,称为long run和short run。

long run协议适用于至少50cm长的长底板应用和至少两个连接设备的应用;

short run协议适用于低功率应用,它通常用于同一个板子上或者底板较短的连接上。

这两类规格的不同在于驱动的Vod。(什么是Vod,很明显不是点播技术)

Target atomic operations(目标原子操作)包括增长,减少,测试和交换,置位和清除操作在L2缓存或寄存器中是不支持的。

对外部设备的Atomic request operations(原子请求操作)是支持的。

(atomic到底是个啥啊?)

外部设备需求

SRIO提供了基于RapidIO Physical Layer 1x/4x LP-Serial 协议的对所有外部设备的无缝接口。这些设备包括ASIC(专用集成电路)、microprocessor(微处理器)、DSP和来自多个供应商的交换机设备。

附:由于作者的个人习惯,“specification”=“规格”=“协议”,三词通用,希望读者不要认为这三个词意思不同。

参考文献

PS:欢迎大家与我讨论文章中的问题,包括反对我的观点。