Rapidio(SRIO) 在ISE上的应用

软件: ISE 14.7

芯片: XILINX V7 325T ffg900

语言:Verilog

引言

近期,在ISE上完成了Rapidio(SRIO)高速接口的驱动。将期间重要过程、遇到的问题及解决方案进行整理,方便诸君需要时查看,少走弯路。

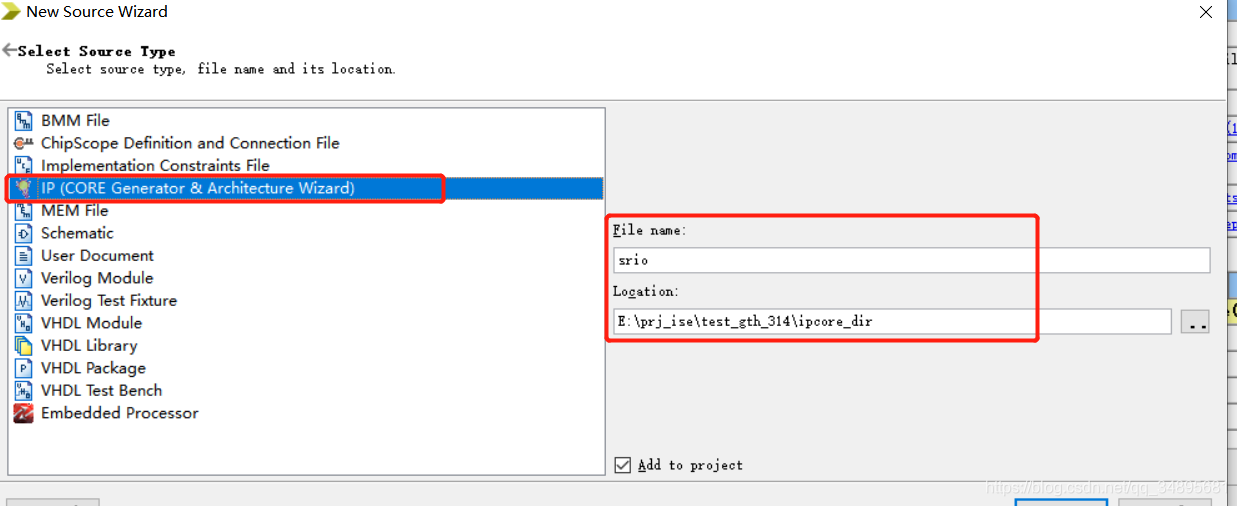

1.1 Rapidio(SRIO)IP的调用

图1

图2

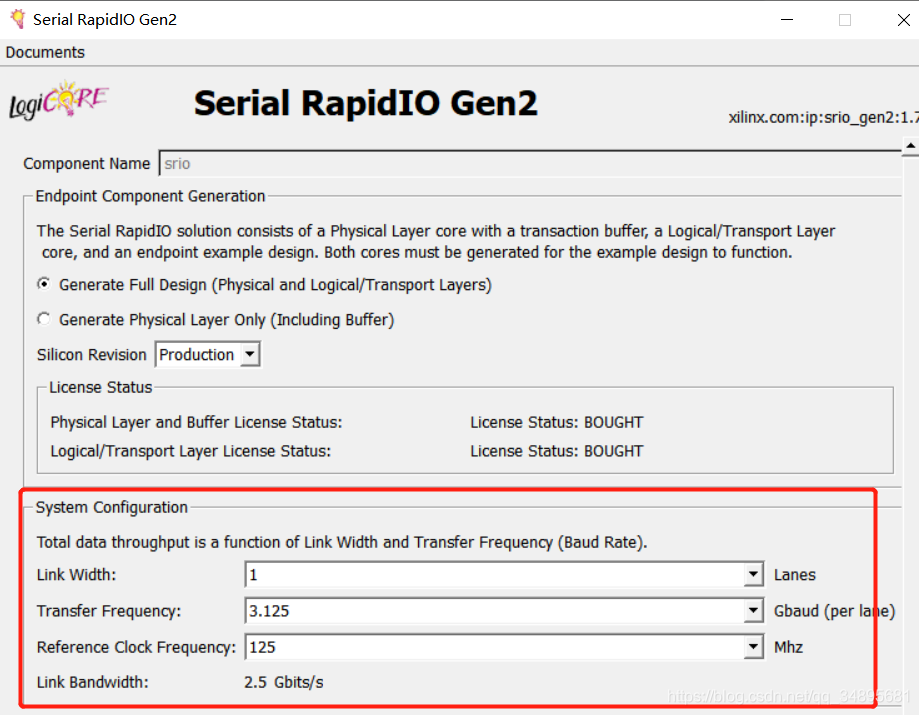

在图2的IP中搜索 Serial Rapidio Gen2,打开参数设置界面如图3。

图3

方框中是系统参数设置,从上到下是:链路宽度、传输速度和参考时钟频率

其他设置默认,点击Genarte,生成IP。

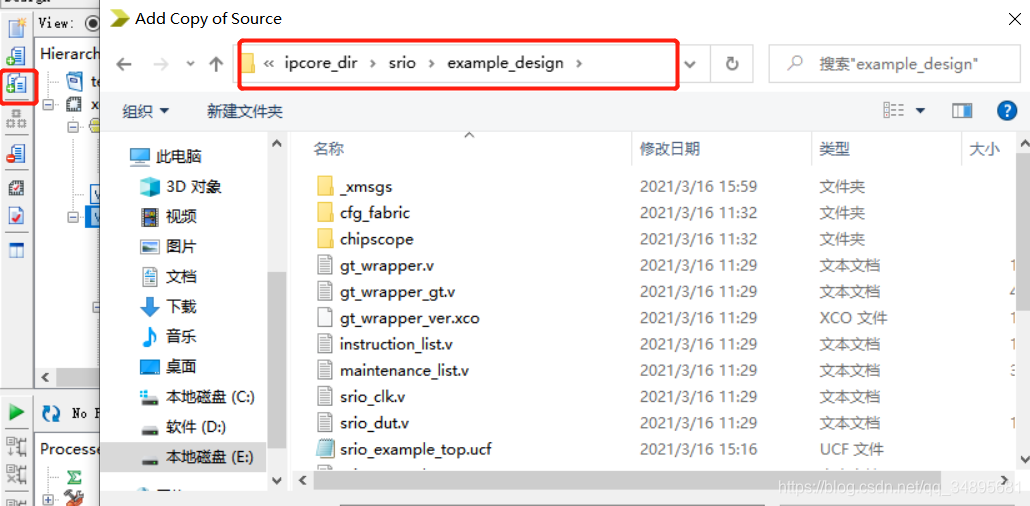

图4

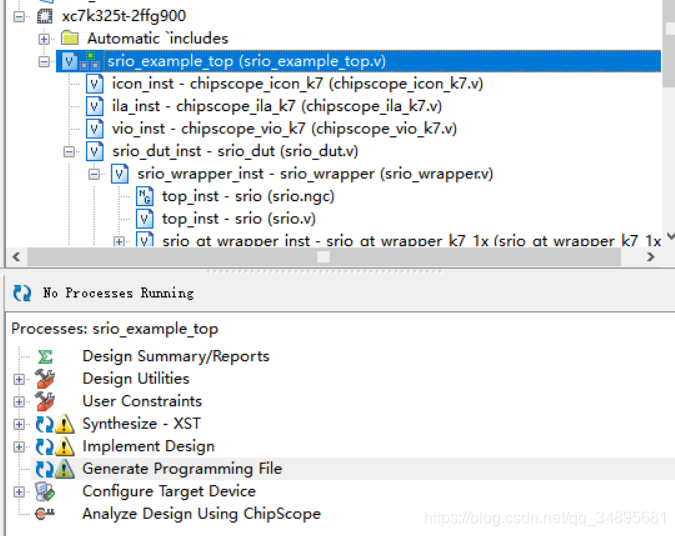

在工程的 “**\ipcore_dir\srio\example_design”路径下,添加IP自带的工程文件,最后工程如下图5。

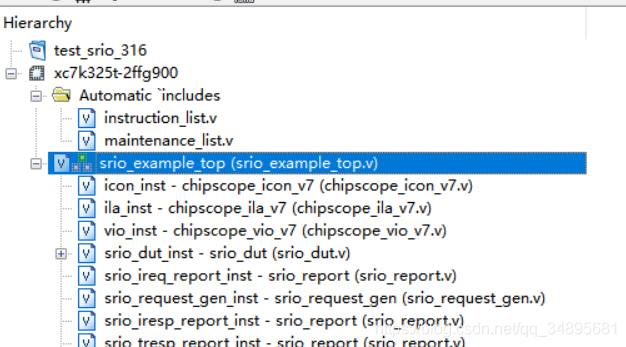

图5

1.2 Rapidio(SRIO)例子工程编译时遇到的问题

开始综合编译如上的例子工程。

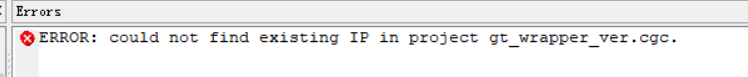

综合时会发现报错,如下:

图6

这不是ISE的例子嘛怎么会报错??就是这么神奇。

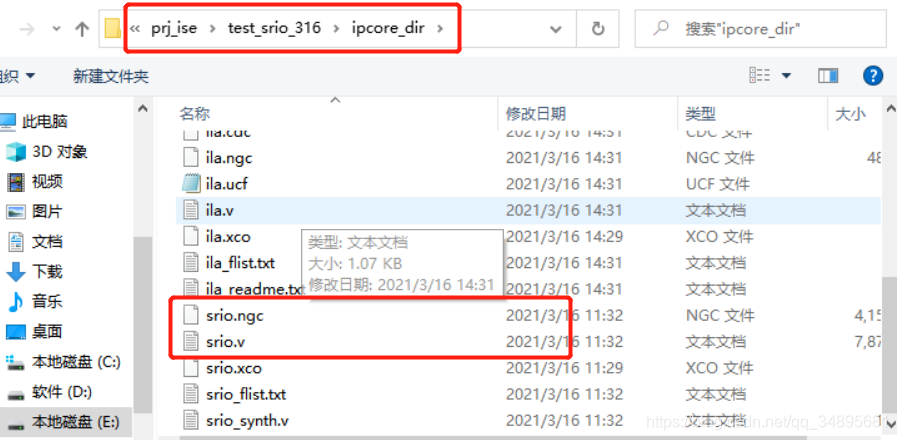

想办法,那如果将IP核用对应的 .v和 .ngc(网表文件)代替如何?

图7

在如上(图7)中找到这两个文件所在,加入到工程中,并将rapidio的ip核移除。

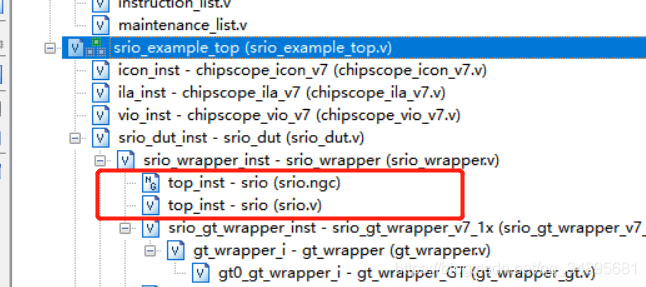

效果如下所示

图8

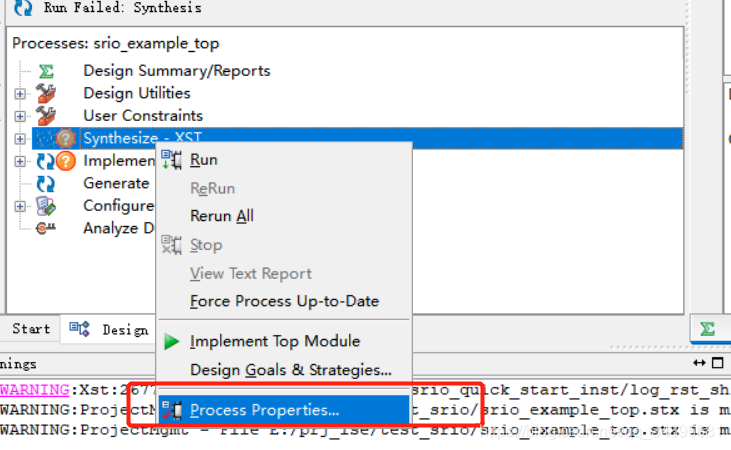

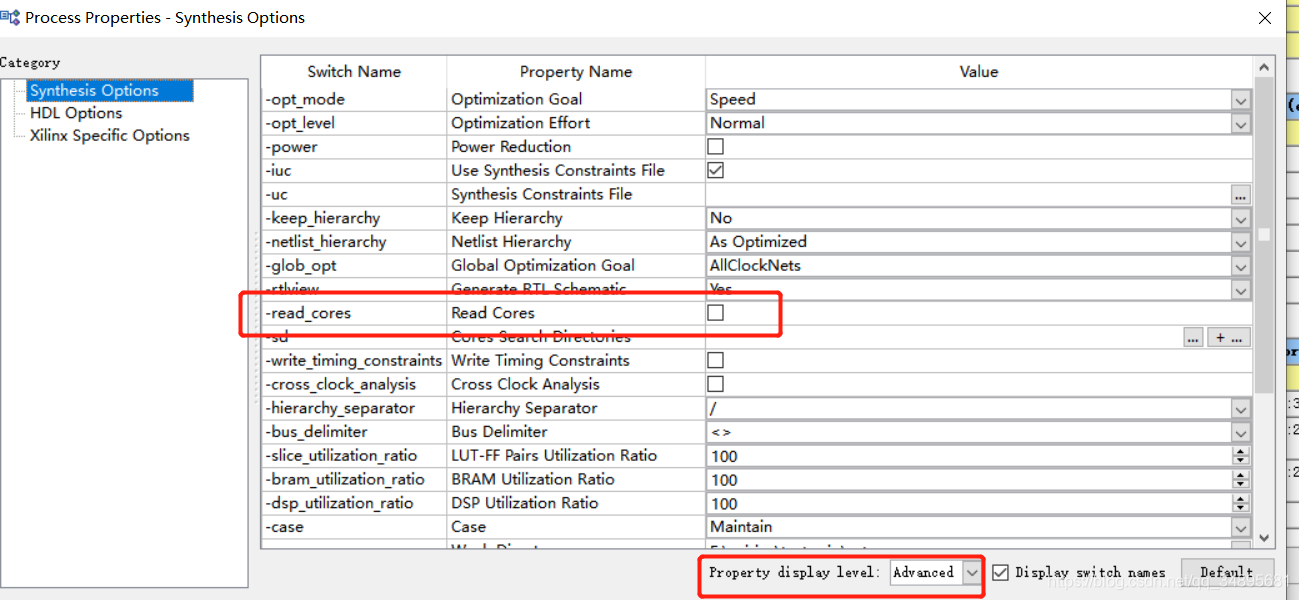

因为我们将ip用网表文件和.v文件代替,故重要的一步来了,如下图9,要设置综合器的属性。

图9

将属性的显示模式设置为高级,找到 read cores 这一项,并将后面方框中的对号取消掉,

如图10所示。如果不进行这一步,会依旧报不知名的错误。

图10

设置完之后,重新进行综合编译直到成功生成比特流,如下图。

约束文件使用的也是例子自动生成的,如果使用具体的管脚,需要自行编辑约束文件。

2.1 总结

本文展示的主要内容是Rapidio IP在使用时,ISE会报错的问题及解决方法。但是需要主要的是,上面使用的芯片的 K7 325TFFG900 ,而当我使用V7的 690T1761 时,工程在编译的时候依然会报错,如下

ERROR:LIT:199 - The component GTXE2_CHANNEL symbol

"srio_dut_inst/srio_wrapper_inst/srio_gt_wrapper_inst/gt_wrapper_i/gt0_gt_wrapper_i/gtxe2_i" is not supported in this device package or family.

ERROR:LIT:199 - The component GTXE2_COMMON symbol

"srio_dut_inst/srio_wrapper_inst/srio_gt_wrapper_inst/gt_wrapper_i/gtxe2_common_0_i" is not supported in this device package or family.

貌似是器件不支持,解决不了,只得去vivado了。如果有人知道解决方案,可以下方评论告知,感激不尽。

相关问题,可以评论私聊交流,共同学习,一起进步~