版权声明:本文为博主原创文章,未经博主允许不得转载。 https://blog.csdn.net/haiyonghao/article/details/52494747

SRIO Functional Description

SRIO管脚

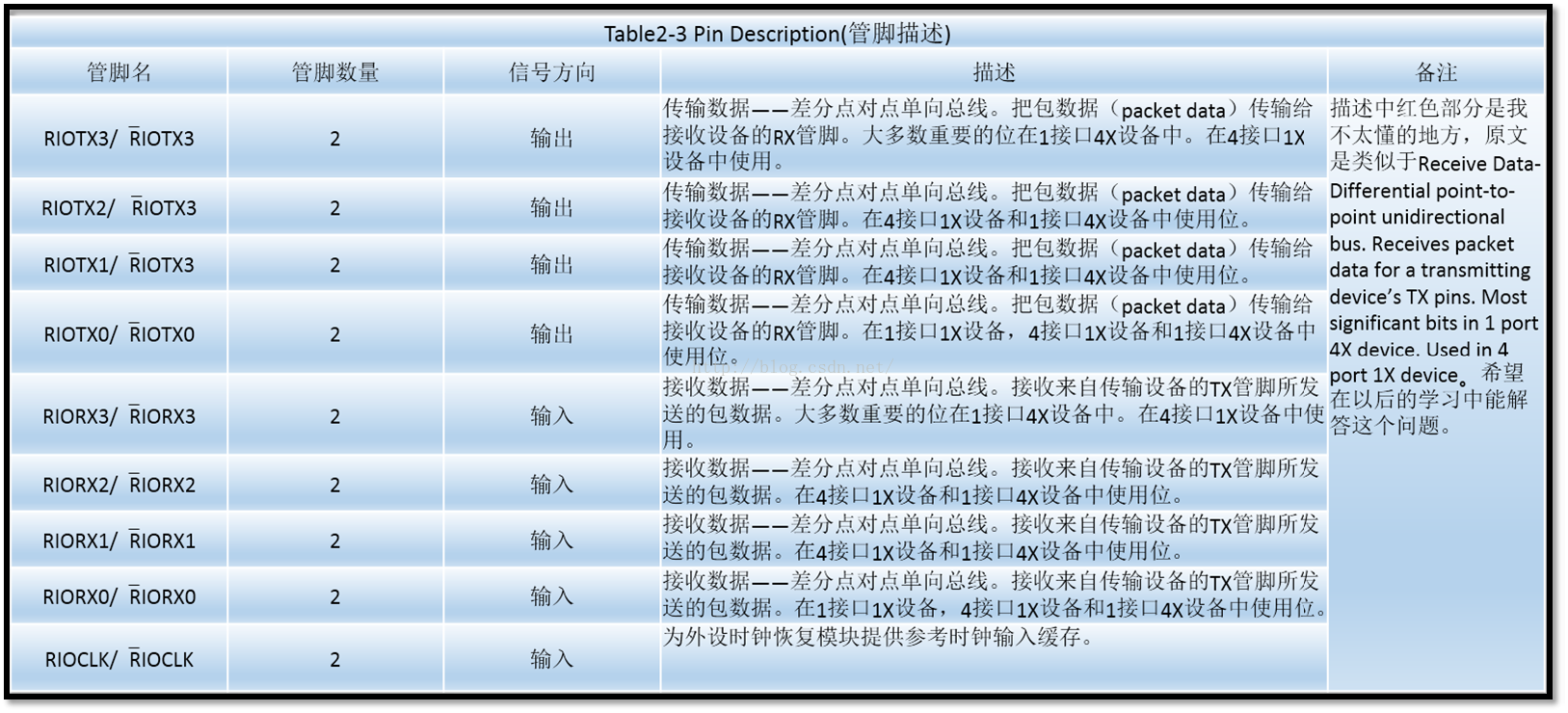

【SRIO管脚部分官方文档给的信息较少,只有一个表格,不过笔者会对表格里的描述进行详细解析】

SRIO设备管脚是基于Current-Mode Logic (CML)【电流模式逻辑】的高速差分信号,传输和接收信号的缓存自身都包含有时钟恢复区域。参考时钟输入是不纳入SerDes宏的,参考时钟使用的是差分缓存输入的,与晶振产商提供的LVDS和LVPECL接口兼容的时钟信号。Table 2-3 描述了SRIO的外设管脚。

大意了,处理图的时候忘记加上红色标记了,笔者不太明白的就是:“在接口设备中使用位”是什么意思,相信是因为现在我的学习深度还不够,以后一定会解答这个问题,先在这里记住,以后回来解释。

参考文献

PS:欢迎大家与我讨论文章中的问题,包括反对我的观点。