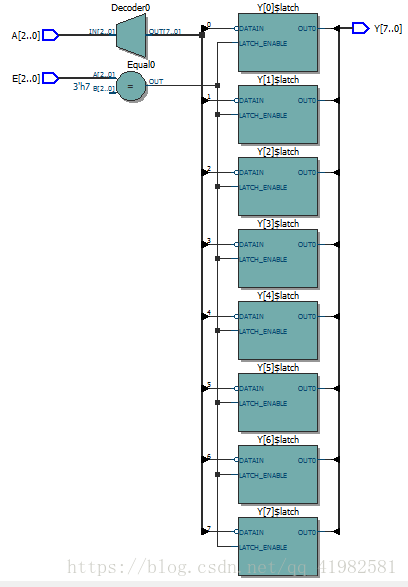

//3-8线译码器

module cy4(input[2:0] E,//输入端口声明

input[2:0] A,//输入端口声明

output reg[7:0]Y//输出端口声明

);

always @(A,E)

if(E == 3'b111)

begin

case(A)

3'b000: Y <= 8'b1111_1110;

3'b001: Y <= 8'b1111_1101;

3'b010: Y <= 8'b1111_1011;

3'b011: Y <= 8'b1111_0111;

3'b100: Y <= 8'b1110_1111;

3'b101: Y <= 8'b1101_1111;

3'b110: Y <= 8'b1011_1111;

3'b111: Y <= 8'b0111_1111;

default: Y <= 8'b1111_1111;

endcase

end

else;

endmodule

测试脚本代码:

`timescale 1 ns/ 1 ps

module cy4_vlg_tst();

reg [2:0] A;

reg [2:0] E;

wire [7:0] Y;

cy4 i1 (

.A(A),

.E(E),

.Y(Y)

);

initial

begin

E = 3’b111;

1000;

A = 3’b000;

100;

A = 3’b001;

100;

A = 3’b010;

100;

A = 3’b011;

100;

A = 3’b100;

100;

A = 3’b101;

100;

A = 3’b110;

100;

A = 3’b111;

100;

display(“Running testbench”);

end

endmodule