之前仔细的记录过一次PWM蜂鸣器的实验,见博文:全过程实现一个最简单的FPGA项目之PWM蜂鸣器控制,这里就不再仔细的写下全过程了,因为都是一样的过程,只记录一下做这个小实验的思路即可。

3-8译码器实验

| SW3 |

SW6,SW5,SW4 |

复位 |

点亮LED |

| X |

X,X,X |

0 |

全灭 |

| OFF |

X,X,X |

1 |

全灭 |

| ON |

OFF,OFF,OFF |

1 |

D2点亮 |

| ON |

OFF,OFF,ON |

1 |

D3点亮 |

| ON |

OFF,ON,OFF |

1 |

D4点亮 |

| ON |

OFF,ON,ON |

1 |

D5点亮 |

| ON |

ON,OFF,OFF |

1 |

D6点亮 |

| ON |

ON,OFF,ON |

1 |

D7点亮 |

| ON |

ON,ON,OFF |

1 |

D8点亮 |

| ON |

ON,ON,ON |

1 |

D9点亮 |

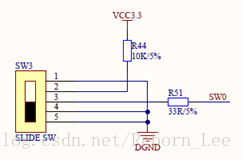

如上图,使用拨码开关来代表3-8译码器的输入,当拨码开关处于“ON”状态时,SW0输出低电平;当拨码开关处于“OFF”状态时,SW0输出高电平。

根据此,编写Verilog 设计代码。

Verilog HDL语言描述

module sp6(

input ext_clk_25m, //外部输入25MHz时钟信号

input ext_rst_n, //外部输入复位信号,低电平有效

input[3:0] switch, //4个拨码开关接口,ON -- 低电平;OFF -- 高电平

output reg[7:0] led //8个LED指示灯接口

);

//-------------------------------------

always @ (posedge ext_clk_25m or negedge ext_rst_n)

if(!ext_rst_n) led <= 8'hff; //所有LED关闭

else if(switch[0]) led <= 8'hff; //SW3处于OFF状态,所有LED关闭

else begin //SW3处于ON状态,点亮的LED位由SW4/SW5/SW6这3个拨码开关输入结果决定

case(switch[3:1])

3'b111: led <= 8'b1111_1110; //D2点亮

3'b110: led <= 8'b1111_1101; //D3点亮

3'b101: led <= 8'b1111_1011; //D4点亮

3'b100: led <= 8'b1111_0111; //D5点亮

3'b011: led <= 8'b1110_1111; //D6点亮

3'b010: led <= 8'b1101_1111; //D7点亮

3'b001: led <= 8'b1011_1111; //D8点亮

3'b000: led <= 8'b0111_1111; //D9点亮

default: ;

endcase

end

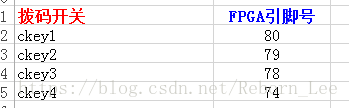

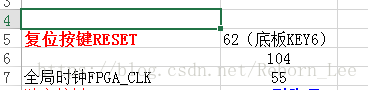

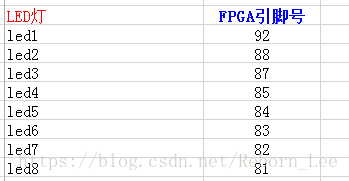

endmodule查表或查看电路图可知,复位以及全局时钟、LED灯和拨码开关的引脚编号:

根据这些来编写引脚约束:

# PlanAhead Generated physical constraints

NET "led[7]" LOC = P81;

NET "led[6]" LOC = P82;

NET "led[5]" LOC = P83;

NET "led[4]" LOC = P84;

NET "led[3]" LOC = P85;

NET "led[2]" LOC = P87;

NET "led[1]" LOC = P88;

NET "led[0]" LOC = P92;

NET "switch[1]" LOC = P79;

NET "switch[0]" LOC = P80;

NET "switch[2]" LOC = P78;

NET "switch[3]" LOC = P74;

NET "ext_clk_25m" LOC = P55;

NET "ext_rst_n" LOC = P62;

由于实验使用资源少,所以没必要进行时序约束,因此,直接进行综合、实现、产生可配置文件、板上调试即可。

调试的结果与第一个表格结果一致。