【前驱知识–主存储器扩展】

主存储器表达方法:字线(地址线) × 位线(数据线)

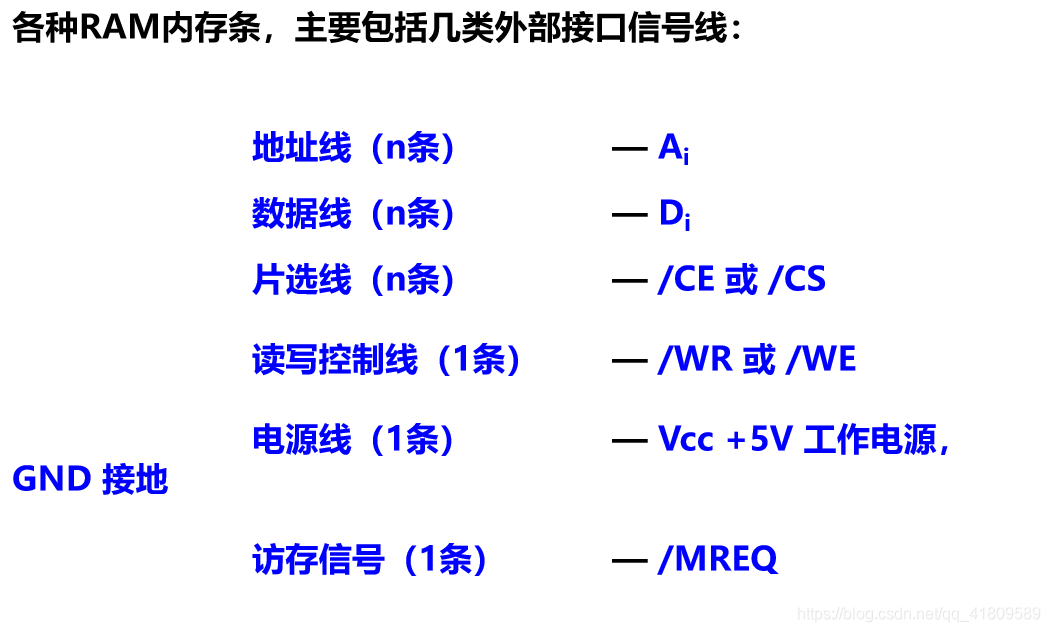

*CS片选信号线、WE读写控制信号线、A地址线、D数据线。

-

位扩展(数据线扩充)

例如:两片16K×4 扩充到 16K×8。

计算地址线数目,遇K取10(遇M取20),16为2的4次方,10+4=14条地址线。将 两个芯片的14条地址线两两分别并在一起,两条片选信号线、两条读写信号线分别两两并一起;两芯片各4条数据线,按顺序接到D0-D3 和 D4-D7。

-

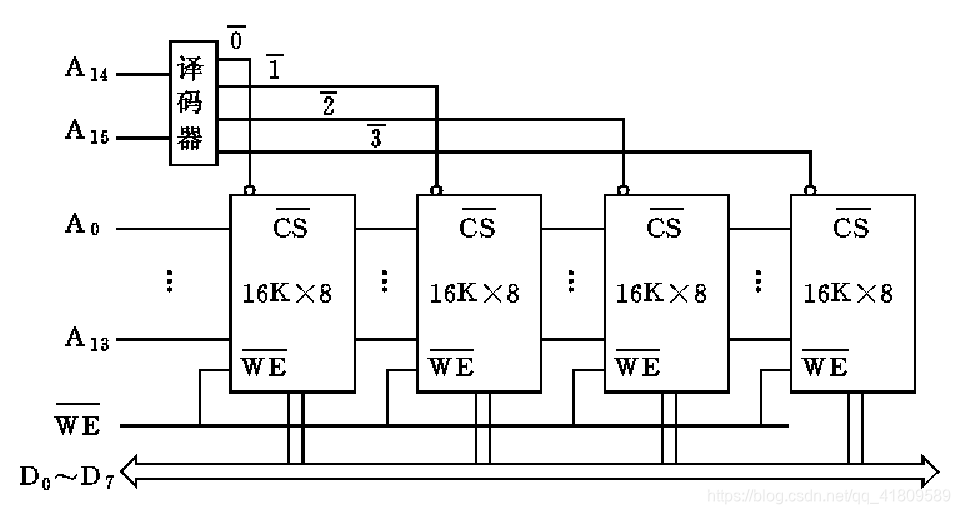

字扩展(地址线扩充)

例如:四片16K × 8 扩充到 64K × 8。

四片地址线 各14条: 所有A0并连在一起… …所有A13并连在一起

四片数据线各8条:所有D0并连在一起… …所有D7并连在一起

四片读写信号线各1条:全部并连在一起,共享一条。

四片片选信号线各1条:由扩展出的高位地址线 A14、A15,通过译码产生4个片选信号。

片选信号相当于班号,来区分相同芯片的地址,在地址前加上由CPU多出来的地址线译码出来的信号就可完成字扩展。 -

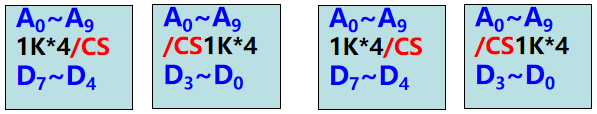

位字扩展(先位后字)

1)字、位同时扩展时:先位扩展,后字扩展。

2)各芯片的片选信号线:并联(位扩展),分开(字扩展)

3)各芯片的片内地址线:条条相并联。

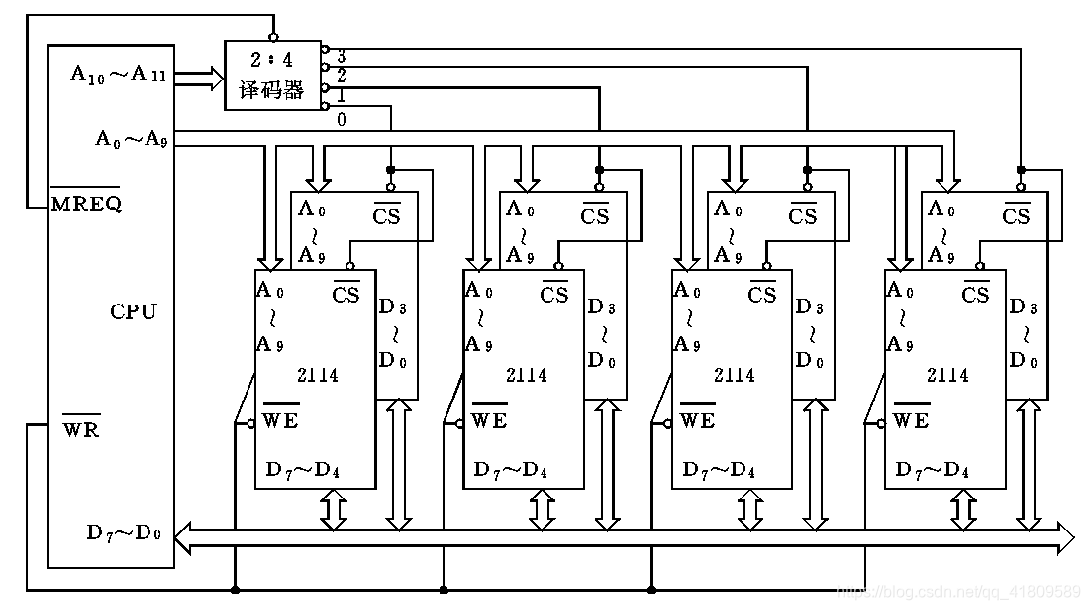

例如:现有芯片Intel2114 1K×4,扩展成 4 K×8 的存储器。

地址线12条,数据线8条。

两个高位地址线,用来译码形成4个片选信号。

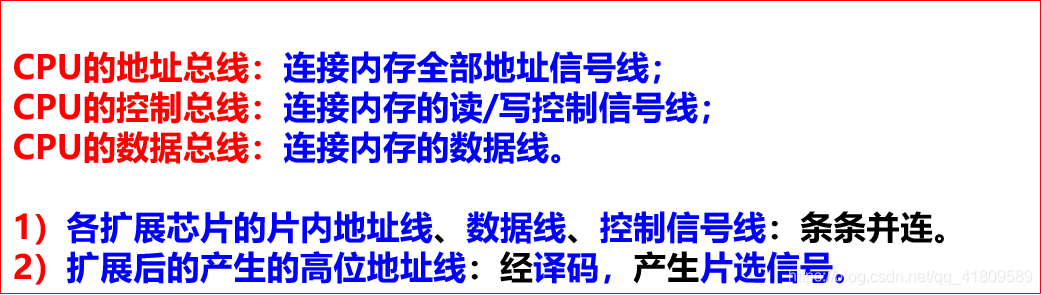

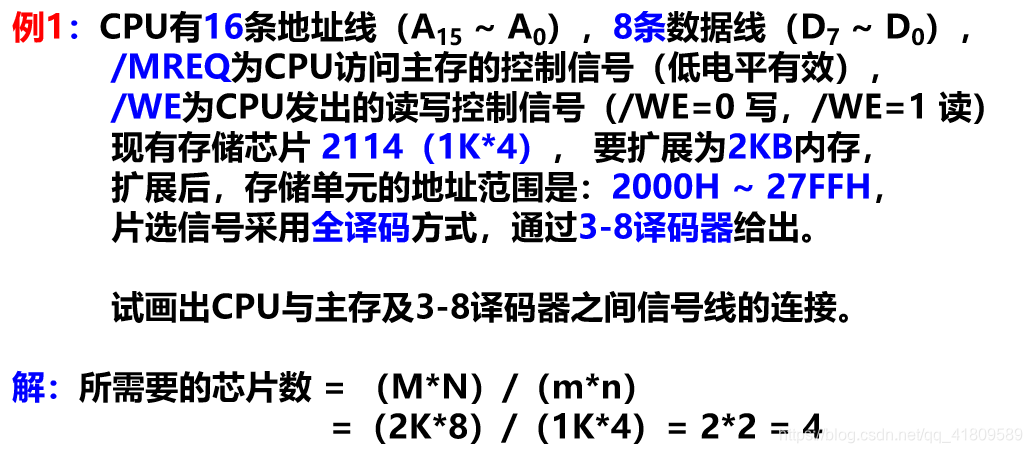

【主存信号线与CPU的连接】

开始画图,开始画图,开始画图

-

先画出四个芯片

-

再把CPU简单画一下,把芯片简单连一下

-

再简单按照模板把CPU和芯片连线完善一下,把3-8译码器亮出来。两个芯片为一个整体时,只要一个读写和一个片选即可,故要把两个芯片连接起来。

-

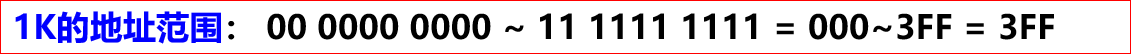

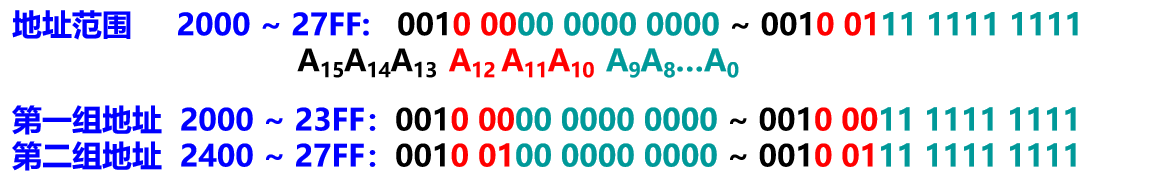

根据题中的地址范围,算出A13、A14、A15哪个是0,哪个是1,根据上面提到过的,G1接1,G2A和G2B接0。

-

对照上面的范围,可以知道A13为1,高电平,所以A13接G1,/MREQ和低电平连一起接G2A和G2B均可。A10,A11,A所对应产生的值在图中可以看出只有000和001两种片选信号,故只输出两根线Y0,Y1即可。

扫描二维码关注公众号,回复: 4939384 查看本文章

到此,CPU与主存及3-8译码器之间信号线的连接就已经结束了,不过这种问题还有好多种情况,要灵活变换,只要理解清楚两种扩展和3-8译码器的用法以及一些其他的基本知识,就能很熟练地解决这种题。以上只是个人理解,有什么不对的地方希望大家大方赐教。