鱼弦:CSDN内容合伙人、CSDN新星导师、全栈领域创作新星创作者 、51CTO(Top红人+专家博主) 、github开源爱好者(go-zero源码二次开发、游戏后端架构 https://github.com/Peakchen)

软件:Quartus II+EDA实验箱

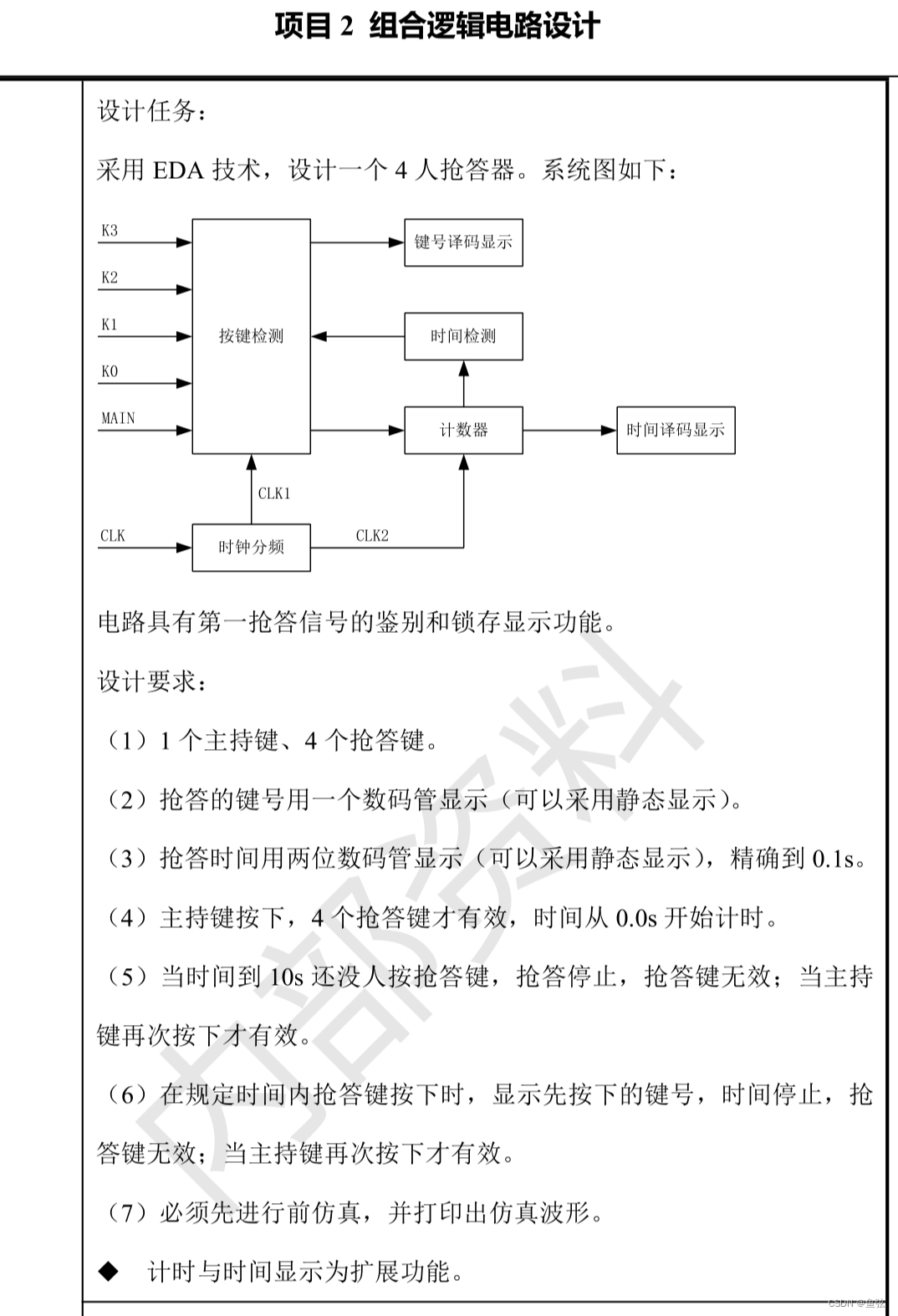

原理详细解释:

四人抢答器的设计基于Verilog语言,使用了组合逻辑电路和时序逻辑电路。以下是对各部分的解释:

-

时钟输入(clk):用于同步电路的时钟信号,控制时序逻辑的运行。

-

抢答键输入(key):四个抢答键的输入信号,检测抢答键是否按下。

-

主持键输入(masterKey):主持键的输入信号,控制抢答器的启动和停止。

-

键号数码管显示(disp1):根据抢答键输入确定的抢答键号,在数码管上进行显示。

-

时间数码管显示(disp2):根据计数器的值,将时间显示在数码管上。

-

计数器(count)ÿ