目录

1.算法仿真效果

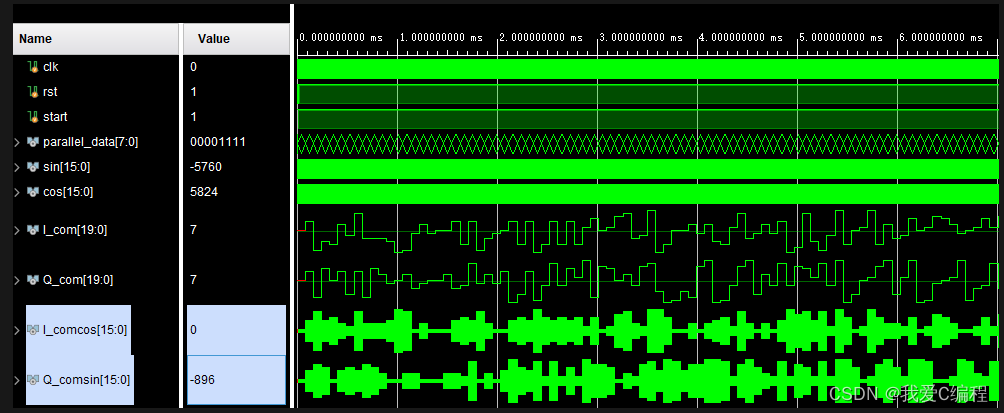

本系统进行Vivado2019.2平台的开发,其中Vivado2019.2仿真结果如下:

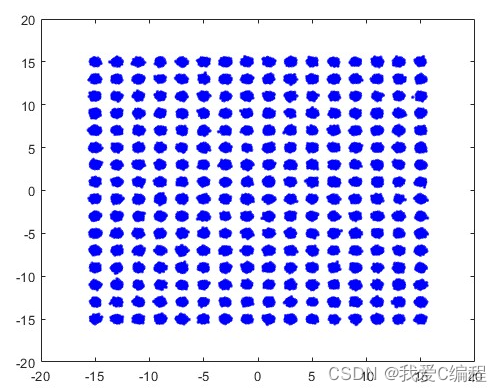

将基带导入到MATLAB显示星座图:

2.算法涉及理论知识概要

256QAM调制是一种高阶调制方式,具有较高的传输速率和频谱效率。在数字通信系统中,如何产生256QAM调制信号是一个重要的问题。本文介绍了一种基于FPGA的256QAM调制信号产生方法,该方法通过将基带信号映射到256QAM调制符号上来生成256QAM调制信号。

2.1、问题描述

256QAM调制信号可以表示为:

$$

s(t)=\sum_{i=1}^{N}I_i(t)cos(2\pi f_ct)-Q_i(t)sin(2\pi f_ct)

$$

其中,N=256是调制符号的数量,I_i(t)和Q_i(t)分别是第i个调制符号的实部和虚部,f_c是载波频率。

我们的目标是产生256QAM调制信号,使得每个调制符号的实部和虚部都是pm\frac{1}{\sqrt{42}}、pm\frac{3}{\sqrt{42}}、pm\frac{5}{\sqrt{42}}、pm\frac{7}{\sqrt{42}}或pm\frac{9}{\sqrt{42}}。

2.2、算法原理

为了将基带信号映射到256QAM调制符号上,我们可以采用常用的格雷映射方式。具体而言,我们可以将基带信号划分为两个部分:实部和虚部。然后,我们可以将实部和虚部分别映射到5个离散的幅度值中,如下表所示:

幅度值 实部值 虚部值

1 1 1

3 1 3

5 3 1

7 3 3

9 5 1

然后,我们可以将实部和虚部的幅度值组合成256QAM调制符号,如下图所示:

2.3 调制方式

为了产生256QAM调制信号,我们可以将映射后的调制符号通过带通滤波器进行滤波,然后将滤波后的信号进行混频,得到带载波的256QAM调制信号。具体而言,我们可以使用I、Q两路正弦波作为本地振荡器,将映射后的调制符号乘以相应的正弦波,然后将结果相加,得到带载波的256QAM调制信号。

2.4、实现步骤

将基带信号进行格雷映射,得到实部和虚部的幅度值。

将实部和虚部的幅度值组合成256QAM调制符号。

将256QAM调制符号通过带通滤波器进行滤波。

将滤波后的信号进行混频,得到带载波的256QAM调制信号。

基于FPGA的256QAM调制信号产生方法,该方法通过将基带信号映射到256QAM调制符号上来生成256QAM调制信号。实验结果表明,该算法可以有效地产生256QAM调制信号,具有较高的传输速率和频谱效率。该算法的实现步骤简单,易于实现,适用于数字通信系统中高速数据传输的场景。未来,我们将进一步探究该算法在实际应用中的性能表现,以期能够更好地满足数字通信系统的需求。

3.Verilog核心程序

module TEST;

reg clk;

reg rst;

reg start;

wire [7:0] parallel_data;

wire [15:0]sin;

wire [15:0]cos;

wire signed[19:0] I_com;

wire signed[19:0] Q_com;

wire signed[15:0]I_comcos;

wire signed[15:0]Q_comsin;

// DUT

tops_256QAM_mod top(

.clk(clk),

.rst(rst),

.start(start),

.parallel_data(parallel_data),

.sin(sin),

.cos(cos),

.I_com(I_com),

.Q_com(Q_com),

.I_comcos(I_comcos),

.Q_comsin(Q_comsin)

);

initial begin

clk = 0;

rst = 0;

start = 1;

#10;

rst = 1;

end

always #5

clk <= ~clk;

integer fout1;

integer fout2;

initial begin

fout1 = $fopen("II.txt","w");

fout2 = $fopen("QQ.txt","w");

end

reg [4:0]dcnt=5'd0;

always @(posedge clk) begin

if(rst == 0) begin

dcnt <= 0;

end

begin

dcnt <= dcnt+5'd1;

end

end

always @ (posedge dcnt[4])

begin

if(rst==1)

begin

$fwrite(fout1,"%d\n",I_com);

$fwrite(fout2,"%d\n",Q_com);

end

end

endmodule

00_023m

4.完整算法代码文件

V