目录

1.算法仿真效果

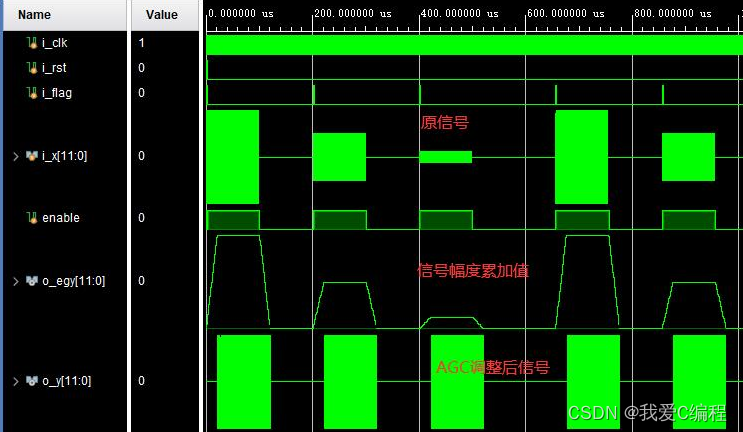

Vivado2019.2仿真结果如下:

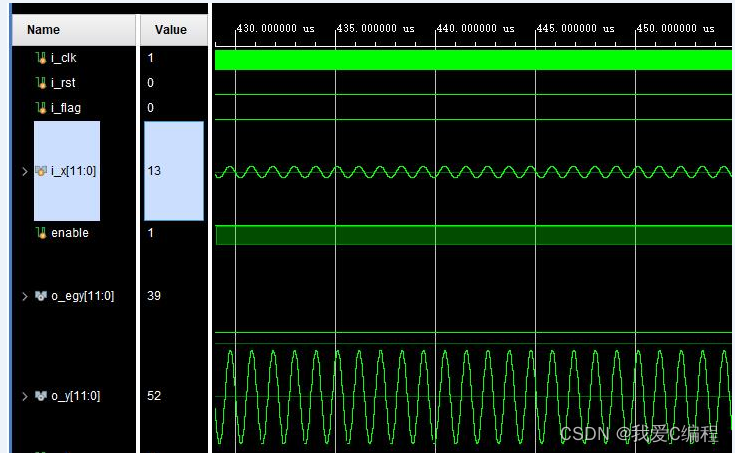

放大后可以看到:

2.算法涉及理论知识概要

数字AGC(Automatic Gain Control)是一种广泛应用于通信系统中的自动增益控制技术。它可以自动调节接收信号的增益,以使信号的强度保持在适当的范围内,从而保证接收到的信号质量。

数字AGC广泛应用于通信系统中,如无线电通信、卫星通信、雷达系统等。在这些应用中,数字AGC可以保证接收到的信号强度始终在适当的范围内,从而保证通信的质量和可靠性。以无线电通信为例,数字AGC可以使接收机在强信号和弱信号之间自动切换,从而避免强信号引起的失真和弱信号引起的噪声。数字AGC还可以减少对电池的能量消耗,延长电池寿命。在卫星通信中,数字AGC可以使接收机在不同的天线方向之间自动切换,并根据信号的强度进行自动调节,从而保证接收到的信号质量和可靠性。在雷达系统中,数字AGC可以保证雷达接收到的回波信号强度始终在适当的范围内,从而保证雷达的探测距离和探测精度。总之,数字AGC是一种非常重要的技术,在通信系统、雷达系统等领域有着广泛的应用和发展前景。

在文中,我们将详细介绍基于FPGA的数字AGC的原理和工作过程实现步骤。数字AGC的基本原理是在接收信号经过前端放大器之后,将信号进行采样、ADC转换、数字滤波等处理,得到信号的强度值,并将其与设定的阈值进行比较,然后根据比较结果对前端放大器的增益进行自动调节,使信号的强度保持在适当的范围内。具体来说,数字AGC的工作过程如下:

采样:接收信号经过前端放大器之后,将其进行采样,得到一系列的采样值。

ADC转换:将采样值通过ADC转换成数字信号。

数字滤波:对ADC转换后的数字信号进行数字滤波,去除高频噪声和低频漂移。

平方运算:对数字滤波后的信号进行平方运算,得到信号的功率值。

移动平均:对平方运算后的信号进行移动平均,得到信号的平均功率值。

比较:将平均功率值与设定的阈值进行比较,得到比较结果。

自动调节:根据比较结果对前端放大器的增益进行自动调节,使信号的强度保持在适当的范围内。

以上就是数字AGC的基本原理。下面我们将介绍如何在FPGA中实现数字AGC。

3.Verilog核心程序

..................................................................

//signal 延迟

reg signed[11:0]dly_x[2149:1];

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

for(i=1;i<=2149;i=i+1)

dly_x[i]<=12'd0;

end

else begin

dly_x[1]<=i_x;

for(i=2;i<=2149;i=i+1)

dly_x[i]<=dly_x[i-1];

end

end

//flag 延迟

reg signed[2148:0]dly_flag;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

dly_flag<=2149'd0;

end

else begin

dly_flag<={dly_flag[2147:0],i_flag};

end

end

wire signed[11:0]w_y = dly_x[2149];

assign o_flag= dly_flag[2048];

//自动增益

wire [19 : 0] gains;

blk_agc blk_agc_u (

.clka(i_clk), // input wire clka

.rsta(i_rst), // input wire rsta

.addra(o_egy), // input wire [8 : 0] addra

.douta(gains), // output wire [19 : 0] douta

.rsta_busy() // output wire rsta_busy

);

reg signed[19:0]wgains;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

wgains <= 20'b0;

end

else begin

if(o_flag == 1'b1)

wgains <= gains;

else

wgains <= wgains;

end

end

endmodule

00_013m4.完整算法代码文件

V