目录

1.算法仿真效果

本系统进行了两个平台的开发,分别是:

Vivado2019.2

Quartusii18.0+ModelSim-Altera 6.6d Starter Edition

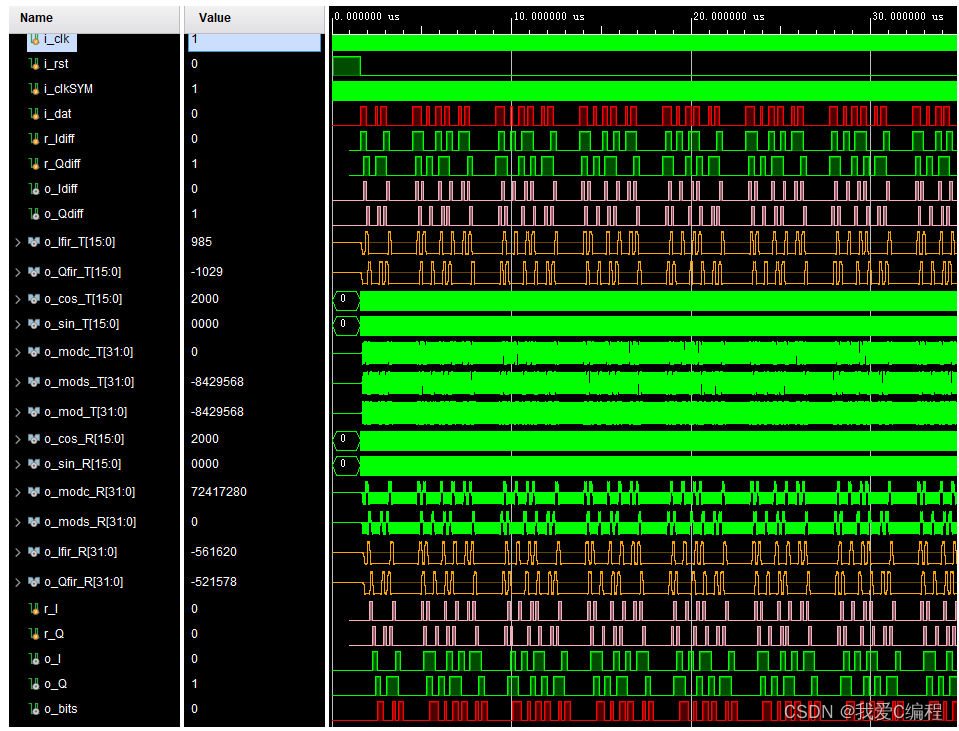

其中Vivado2019.2仿真结果如下:

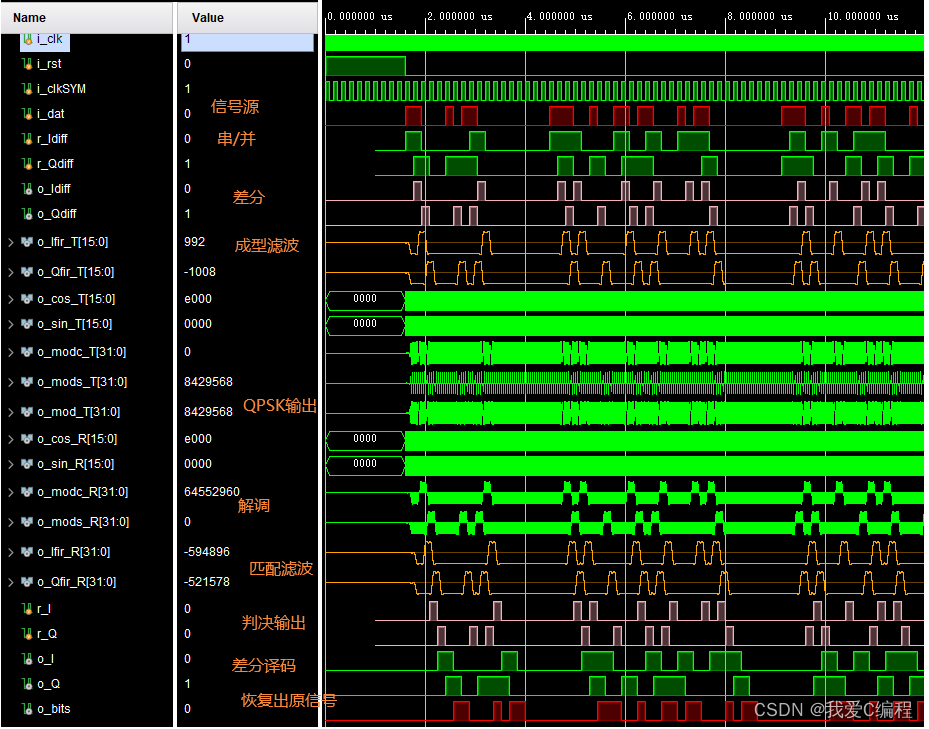

将上面的各个信号放大,各个信号含义如下:

Quartusii18.0+ModelSim-Altera 6.6d Starter Edition的测试结果如下:

Quartusii18.0+ModelSim-Altera 6.6d Starter Edition的测试结果如下:

2.算法涉及理论知识概要

DQPSK调制解调通信系统是一种数字通信系统,用于将数字信息转换为电信号进行传输。DQPSK代表差分四相移键控调制,是一种数字调制技术,它在发送端对数字信息进行编码,并在接收端对信号进行解码。DQPSK调制解调通信系统具有高效、可靠和抗干扰等优点,在现代通信系统中得到广泛应用。

一、DQPSK调制原理

DQPSK调制是通过改变信号的相位来传输数字信息的调制方式。在DQPSK调制中,每个符号代表两个比特,因此,DQPSK调制器需要将两个连续的比特组合在一起来形成一个符号。DQPSK调制器使用了差分编码器来避免相位漂移问题,这是一种将相邻符号之间的相位差编码为一个比特的技术。

下面是DQPSK调制器的数学公式:

每个符号代表两个比特,因此,输入比特串b1和b2可以组成一个符号s,公式如下:

$s = \cos(\theta_1+\theta_0)$

其中,$\theta_1$是上一个符号的相位,$\theta_0$表示本次符号的相位。

DQPSK调制器需要根据上一个符号和本次符号的相位来计算相位差,公式如下:

$\Delta\theta = \arctan\left(\frac{\sin(\theta_1+\theta_0)\cos(\theta_0)-\cos(\theta_1+\theta_0)\sin(\theta_0)}{\cos(\theta_1+\theta_0)\cos(\theta_0)+\sin(\theta_1+\theta_0)\sin(\theta_0)}\right)$

最后,DQPSK调制器需要将相位差映射到相位平面上,公式如下:

$s = \cos(\theta_1+\theta_0+\Delta\theta)$

二、DQPSK解调原理

DQPSK解调器需要根据接收到的信号来计算出相位差,然后将相位差解码为数字信息。DQPSK解调器使用低通滤波器来滤除高频噪声,并将接收到的信号分为两个时间窗口。接下来是DQPSK解调器的数学公式:

接收到的信号r可以表示为:

$r = s\cos(\theta_0)+n$

其中,$\theta_0$是本地参考信号的相位,n是接收到的噪声。

接下来,将接收到的信号r分为两个时间窗口r1和r2:

$r_1 = r_{T/2-1:0}$

$r_2 = r_{T-1:T/2}$

其中,T是一个符号的持续时间。

计算相位差,公式如下:

$\Delta\theta = \arctan\left(\frac{h\sin(2\pi fT)(r_1\cos(\theta_0)-r_2\sin(\theta_0))}{h\cos(2\pi fT)(r_2\cos(\theta_0)+r_1\sin(\theta_0))}\right)$

其中,h是低通滤波器的传递函数,f是载波频率。

最后,将相位差解码为数字信息,公式如下:

$b_1 = \Delta\theta > 0$

$b_2 = |\Delta\theta| > \pi/2$

这里,如果相位差$\Delta\theta$大于0,则将$b_1$设置为1,否则设置为0;如果相位差的绝对值大于$\pi/2$,则将$b_2$设置为1,否则设置为0。

三、DQPSK调制解调算法的实现过程

下面是DQPSK调制解调算法的实现过程:

产生本地参考信号

在DQPSK调制解调通信系统中,发送端和接收端需要使用相同频率和相位的载波信号。因此,需要在接收端产生一个本地参考信号,用于解调接收到的信号。本地参考信号可以使用一个简单的正弦波振荡器产生,公式如下:

$\theta_0(nT) = \theta_0((n-1)T) + 2\pi f_0 T$

其中,$f_0$是载波频率,$T$是一个符号的持续时间。

进行DQPSK调制

DQPSK调制器需要将两个连续的比特组合在一起来形成一个符号,然后根据上一个符号和本次符号的相位来计算相位差,最后将相位差映射到相位平面上。

3.Verilog核心程序

module TEST();

reg i_clk;

reg i_rst;

reg i_clkSYM;

reg i_dat;

wire o_Idiff;

wire o_Qdiff;

wire signed[15:0]o_Ifir_T;

wire signed[15:0]o_Qfir_T;

wire signed[15:0]o_cos_T;

wire signed[15:0]o_sin_T;

wire signed[31:0]o_modc_T;

wire signed[31:0]o_mods_T;

wire signed[31:0]o_mod_T;

wire signed[15:0]o_cos_R;

wire signed[15:0]o_sin_R;

wire signed[31:0]o_modc_R;

wire signed[31:0]o_mods_R;

wire signed[31:0]o_Ifir_R;

wire signed[31:0]o_Qfir_R;

wire o_I;

wire o_Q;

wire o_bits;

//DQPSK调制

TDQPSK TQPSKU(

.i_clk (i_clk),

.i_rst (i_rst),

.i_clkSYM(i_clkSYM),

.i_dat (i_dat),

.o_Idiff(o_Idiff),

.o_Qdiff(o_Qdiff),

.o_Ifir (o_Ifir_T),

.o_Qfir (o_Qfir_T),

.o_cos (o_cos_T),

.o_sin (o_sin_T),

.o_modc (o_modc_T),

.o_mods (o_mods_T),

.o_mod (o_mod_T)

);

//DQPSK解调

RDQPSK RQPSKU(

.i_clk (i_clk),

.i_rst (i_rst),

.i_clkSYM(i_clkSYM),

.i_med (o_mod_T[25:10]),

.o_cos (o_cos_R),

.o_sin (o_sin_R),

.o_modc (o_modc_R),

.o_mods (o_mods_R),

.o_Ifir (o_Ifir_R),

.o_Qfir (o_Qfir_R),

.o_I(o_I),

.o_Q(o_Q),

.o_bits(o_bits)

);

initial

begin

i_clk = 1'b1;

i_clkSYM=1'b1;

i_rst = 1'b1;

#1600

i_rst = 1'b0;

end

always #5 i_clk=~i_clk;

always #80 i_clkSYM=~i_clkSYM;

initial

begin

i_dat = 1'b0;

#1440

repeat(10)

begin

#160 i_dat = 1'b1;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

#160 i_dat = 1'b1;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b1;

#160 i_dat = 1'b1;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

#160 i_dat = 1'b0;

#160 i_dat = 1'b1;

#160 i_dat = 1'b1;

#160 i_dat = 1'b0;

end

$stop();

end

endmodule

00_016m4.完整算法代码文件

V