论文地址:https://arxiv.org/pdf/1909.00948.pdf

发表时间:2019年

最先进的神经网络结构,如ResNet,MobileNet和DenseNet,在低MACss和小参数模型上取得了卓越的精度。然而,这些指标对于预测推断时间可能并不准确。我们认为,访问中间特征图的内存传输可能是主导推理延迟的一个因素,特别是在实时目标检测和高分辨率视频语义分割等任务中。我们提出了一个谐波密集连接的网络,以实现在低MACss和内存流量方面的高效率。与FC-DenseNet-103、DenseNet-264、ResNet-50、ResNet-152和SSD-VGG相比,新的网络分别减少了35%、36%、30%、32%、45%的推理时间。我们使用包括Nvidia分析器和ARMScale-Sim在内的工具来测量内存流量,并验证推理延迟与内存流量消耗确实成正比,并且所提出的网络消耗的内存流量较低。我们的结论是,在设计高分辨率应用程序的神经网络结构时,应该考虑内存流量

1. Introduction

卷积神经网络(CNN)已经在计算机视觉任务中很流行,因为计算能力的爆炸性增长使复杂的网络像AlexNet[22,23],VGG-net[32]和Inception[34]可以被训练。为了将这些令人着迷的研究成果投入大规模使用,在边缘设备上进行神经网络推断是不可避免的。然而,边缘计算依赖于有限的计算能力和电池容量。因此,如何提高计算效率,降低边缘神经网络推理的功耗已成为一个关键问题。

减小模型的大小(模型的参数数或权重数)是提高计算效率和能源效率的一个热门研究课题,因为,减少的模型大小通常意味着在读取和写模型参数和特征图时,更少的MACss(乘法累积运算或浮点运算的数量)和更少的动态随机存取内存(DRAM)流量。一些研究已经转向了精度-参数比的最大化。最先进的网络,如残差网络(ResNets)[16]、SqueezeNets[20]和密集连接网络(DenseNets)[18],已经实现了高参数效率,显著降低了模型的大小,同时保持了高精度。通过压缩,可以进一步减小模型的尺寸。Han等人的[15]表明,从DRAM加载大量浮点权值可能比算术运算消耗更多的功率。他们的深度压缩算法采用权值剪枝和量化来显著降低模型的大小和功耗。

除了功耗之外,由于DRAM带宽的有限,DRAM访问也可能在推理时间方面主导系统的性能。因为我们观察到CNN中的中间特征图内存占用之和可以十到几百倍大于模型大小,特别是高分辨率任务如语义分割使用完全卷积网络[27],我们建议减少在DRAM中访问特征图,或许可以在某些情况下加速。

缩小特征地图的大小是一种减少流量的一种直接方法。虽然关于特征映射的无损压缩的论文较少,但在模型精度近似和操作近似[11,8,14,28,29]的研究中,人们对特征映射的有损压缩进行了深入的研究。在这些工作中通常用于模型压缩的量化减小特征映射的大小。然而,就像其他有损压缩方法,如下采样一样,它们通常会降低精度。在本文中,我们探讨了如何通过仔细设计CNN的架构,在不降低精度的情况下减少特征图的DRAM流量。

为了设计这样一个低DRAM流量的CNN架构,需要对实际流量进行测量。对于一个通用的图形处理单元(GPU),我们使用Nvidia分析器来测量DRAM读/写字节的数量。对于移动设备,我们使用ARMScaleSim[30]来获取每个CNN架构的流量数据和推理周期计数。我们还提出一个度量称为卷积输入/输出(CIO),这是一个简单的关于每个卷积层中输入tensor大小和输出tensor总和的方程(1),其中c是通道的数量,w和h特征为卷积层l输出特征图的宽度和高度。

C I O = ∑ l ( x i n l × w i n l × h i n l + x o u t l × w o u t l × h o u t l ) CIO=\sum_{l}(x_{in}^l \times w_{in}^l \times h_{in}^l + x_{out}^l \times w_{out}^l \times h_{out}^l ) CIO=l∑(xinl×winl×hinl+xoutl×woutl×houtl)

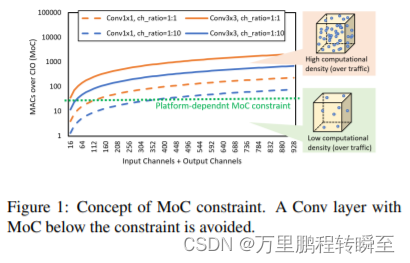

CIO是实际DRAM流量值成比例的近似值。请注意,输入tensor可以是一个串联,因此复用的tensor可以计算多次。使用大量的大型卷积内核可以很容易地实现最小化的CIO。然而,它也损害了计算效率,并最终导致超过增益的显著延迟开销。因此,我们认为保持较高的计算效率仍然是必要的,只有当一个层,MACss超过CIO (MoC),且低于计算平台的某个性能指标下,CIO才能主导推理时间。

例如,在一个固定的CIO下,将卷积层的输入和输出之间的信道比从1:1逐步改为1:100会导致减少MACss和延迟。对于延迟,它比MACss的减少下降得更慢,因为内存流量是一样的。MoC的一定值可能表明,在这个比率以下,一个层的延迟总是被限制在一个固定的时间内。然而,这种价值依赖于平台,而且在经验上很模糊。

本文对各层的MoC应用软约束,设计了一个合理增加MACs的低CIO网络模型。如图1所示,我们避免使用MoC很低的层,例如具有非常大的输入/输出信道比的Conv1x1层。受密集连接网络[18]的启发,我们通过应用该策略提出了一种谐波紧密连接网络(HarDNet)。我们首先减少了来自DenseNet的大部分层连接,以减少连接成本。然后,我们通过增加连接层的通道数来平衡输入/输出通道比。

本文的贡献是,我们引入了用于特征图访问的DRAM流量及其平台独立近似CIO,作为评估CNN架构的新度量,并表明推理延迟与DRAM流量高度相关。通过限制每一层的MoC,我们提出了HarDNets,与DenseNets相比,它减少了40%的DRAM流量。我们在CamVid[3]、ImageNet(ILSVRC)[9]、PASCAL VOC[12]和MS COCO[26]数据集上评估了提出的HarDNet。与DenseNet和ResNet相比,HarDNet实现了相同的精度,CIO减少了30%∼50%,推理时间减少了30%∼40%。

2. Related works

神经网络研究的一个重要趋势是利用shortcuts。为了解决退化问题,Highway Networks[33] and Residual Networks[16]添加了shortcuts来总结一个具有多个前一个层的层。随机深度正则化[19]本质上是随机丢弃的交叉层的另一种shortcuts形式。shortcuts使隐式监督能够使网络不断深入而不退化。网络[18]连接所有前面的层作为一个shortcuts,实现更有效的深度监督。shortcuts也被证明在分割任务[10]中非常有用。J‘egou等人[21]表明,没有任何预训练,DenseNet可以很好地进行语义分割。然而,shortcuts会导致大量的内存使用和大量的DRAM流量。使用shortcuts可以延长张量的生命周期,这可能导致DRAM和缓存之间频繁的数据交换。

一些DenseNet的稀疏版本被提出。 LogDenseNet[17] and SparseNet[36]采用了一种稀疏化连接方式,对于所有layer k与layer k − 2 n k-2^n k−2n相连接,其中n>0, k − 2 n > 0 k-2^n>0 k−2n>0 【也就是每一层只和自己前面的 2 n 2^n 2n层连接,输出层也是如此】,使输入信道数从O(L2)减少到O(LlogL)。它们之间的区别在于,LogDenseNet全局应用这种策略,其中跨越不同分辨率的块的层连接仍然遵循log连接规则【只与自己距离为 2 n 2^n 2n的层连接】,而SparseNet有一个固定的block输出,将输出看作是具有L层的block的L+1 block。然而,这两种网络架构都需要显著提高增长率(输出通道数)来恢复连接剪枝后的精度下降,而增长率的增加会影响CIO的减少。然而,这些研究确实指出了一个很有前途的方向。

一个经典的微计算机架构的性能是由其有限的计算能力和内存带宽[4]主导的。研究人员更注重提高计算能力和效率。一些研究人员指出,在基于gpu的系统[25,27]、基于FPGA的系统[5,13]或自定义加速器[11,6,7]中,有限的内存带宽可以主导推理延迟和功耗。然而,目前还没有系统的方法来关联DRAM流量和延迟。因此,我们提出了CIO和MoC,并提出了一种提高效率的概念性方法。

3. Proposed Harmonic DenseNet

3.1. Sparsification and weighting

我们提出了一种新的基于密集连接网络的网络体系结构。与LogDenseNet中提出的稀疏化不同,如果 2 n 2^n 2n整除k,我们让k层连接到 k − 2 n k-2^n k−2n层,其中n是一个非负整数, k − 2 n > 0 k-2^n>0 k−2n>0【只考虑能整除 2 n 2^n 2n层的密集连接,输出层与所有的奇数层连接】;具体来说,第0层是输入层。在该连接方案下,一旦处理了层 2 n 2^n 2n,就可以从存储器中刷新层1到层 2 n − 1 2^n-1 2n−1。这些连接使网络表现为第两次谐波功率的重叠,如图2所示,因此我们称之为谐波密集连接网络(HarDNet)。所提出的稀疏化方案比LogDenseNet更好地降低了连接成本。这种连接模式看起来也像一个FractalNet[24],不过后者使用averaging shortcuts替代了concat。

在该网络中,指数除以较大幂的层比指数除以较小幂的层更有影响力。我们通过增加这些关键层的通道来放大它们,这可以平衡一个层的输入和输出之间的通道比率,以避免低MoC。一层l的初始增长率为k,我们让它的通道数为 k × m n k×m^n k×mn,其中n是满足l除以 2 n 2^n 2n的最大数。乘数m作为一个低维压缩因子。如果输入层0有k个信道和m个=2,我们得到每一层的信道比为1:1。设置m小于2就相当于将输入通道压缩为更少的输出通道。根据经验,将m设置在1.6和1.9之间可以了良好的精度和参数效率

3.2. Transition and Bottleneck Layers

所提出的连接模式形成了一组称为谐波密集块(HDB)的层,然后是一个Conv1x1层作为过渡。我们让每个HDB的深度为两的幂数,这样HDB的最后一层就有最多的信道。在DenseNet中,一个块的密集连接的输出直接将梯度从输出传递到之前的所有层,以实现深度监督。在我们的深度为L的HDB中,梯度将通过最多的log L层。为了缓解退化,我们将depth-L HDB的输出作为L层及其之前所有奇数层的连接,这是具有k个输出通道的最小显著层。一旦HDB完成,从2到L-2的所有偶数层的输出都可以被丢弃。当m在1.6到1.9之间时,它们的总内存占用大约是所有奇数层加起来的两到三倍。

DenseNet在每个Conv3x3层之前都有一个瓶颈层,以提高参数效率。由于我们已经平衡了每一层的输入和输出之间的信道比,因此这些瓶颈层的影响变得不显著。为每四个Conv3x3层插入一个瓶颈层仍然有助于减少模型的大小。我们让一个瓶颈层的输出通道为 c i n / c o u t × c o u t \sqrt{c_{in}/c_{out} } \times c_{out} cin/cout×cout,其中cin是连接的输入通道,而 c o u t c_{out} cout是以下Conv3x3层的输出通道。为了进一步提高推理时间,可以丢弃这些Conv1x1瓶颈层来满足我们的MoC约束。

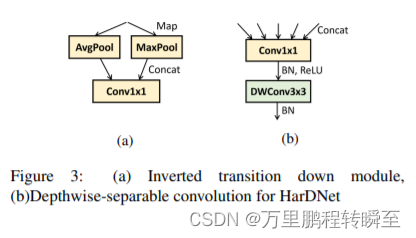

DenseNet提出的过渡层是Conv1x1层,然后是2x2的平均池化。如图3a所示,我们提出了一个反向转换模块,它将输入张量与原始平均池化一起映射到一个附加的最大池化函数,然后是连接和Conv1x1。该模块为Conv1x1减少了50%的CIO,同时以牺牲模型尺寸的增加为代价,实现了大致相同的精度。

3.3. Detailed Design

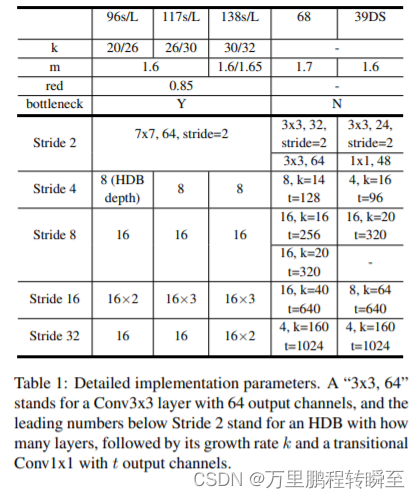

为了与DenseNet进行比较,我们遵循它的全局密集连接策略,即绕过一个HDB的所有输入作为其输出的一部分,并提出了6个HarDNet模型。具体参数见表1。我们对过渡层使用0.85的还原率,而不是在DenseNet中使用的0.5的还原率,因为正如我们之前提到的,已经对增长率倍增器应用了低维压缩。为了实现灵活的深度,我们将一个块划分为多个包含16层的块(当计算瓶颈层时为20层)。

我们进一步提出了一个HarDNet-68,在该方法中,我们删除全局密集连接并使用MaxPool进行降采样,我们将DenseNet提出的BN-ReLU-Conv顺序改为Conv-BNReLU的标准顺序,以实现批归一化的折叠。HarDNet-68中每个HDB的专用增长率k提高了CIO的效率。由于一个深度HDB有更多的输入信道,一个更大的增长率有助于平衡一个层的输入和输出之间的信道比率,以满足我们的MoC约束。对于层分布,我们没有专注于大多数CNN模型所采用的stride-16,而是让stride-8在HarDNet-68中拥有最多的层,从而提高了局部特征学习。相比之下,分类任务更多地依赖于全局特征学习,因此集中于低分辨率可以获得更高的精度和更低的计算复杂度。

HarDNet也采用了深度可分离卷积,它显著地降低了模型的大小和计算复杂度。我们提出了一个hordet-39DS,除了第一个深度卷积层外的纯深度可分离(DS)卷积,将Conv3x3层分解为点卷积和深度卷积,如图3b所示。在这种情况下很重要。由于HDB中的每一层都有一个宽的输入和一个窄的输出,倒置顺序会显著增加CIO。请注意,CIO可能不是比较标准Conv3x3模型和深度可分离卷积模型之间的推理延迟的直接预测,因为它们之间的MACs有巨大的差异。然而,当对CIO的分解卷积进行加权时,仍然可以实现预测。

4. Experiments

4.1. CamVid Dataset

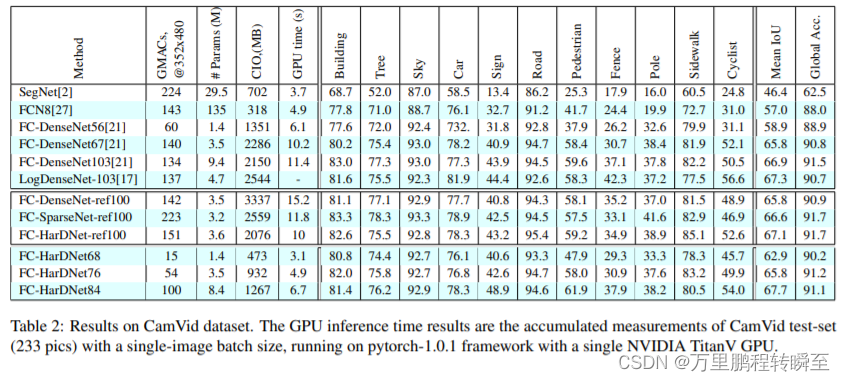

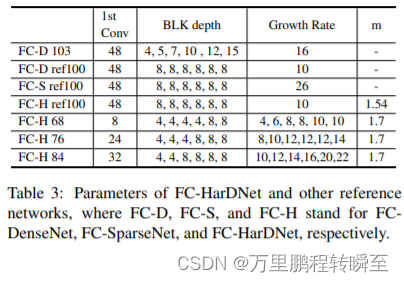

为了研究HDB的性能,我们将FC-DenseNet中的所有块替换为hdb。我们遵循FC-DenseNet的架构,采用编码器-解码器结构和块级shortcuts来创建语义分割模型。为了进行公平的比较,我们为每个块做了两个具有完全相同深度的参考架构,并且模型大小大致相同,命名为FC-HarDNet-ref100和FC-DenseNet-ref100,分别。我们在CamVid数据集上训练和测试了这两个网络,在完全相同的环境下,epoch为800和学习速率衰减为0.998,并遵循了原始工作[21]中使用的两个passes的批处理大小。表2显示了总体和每个类的平均离子化单位的实验结果。与这两个网络相比,FCHarDNet-ref100获得了更高的平均IoU和38%的CIO。当在单个NVIDIA TitanVGPU上运行推理测试时,我们观察到使用紧张流和Pytorch框架分别节省了24%和36%的推理时间。由于FC-HarDNet-ref100比FC-DenseNet-ref100消耗的MACs略多,因此节省推理时间应该来自于减少内存流量。

与其他稀疏版本的DenseNet相比,表2显示FC-LogDenseNet103的CIO数比FC-DenseNet103差,这是由于其全局转换导致的前半层的存活时间较长。另一方面,稀疏网使用了一个局部的过渡层,这样它可以比LogDenseNet更好地降低张量寿命。因此,我们实现了一个FC-SparseNet-ref100进行比较,并在相同的环境中对其进行了5次运行的训练,然后我们选择了最好的结果。结果表明,FC-SparseNet也可以减少GPU推理时间,但不像FC-HarDNet-ref100那样减少那么多。

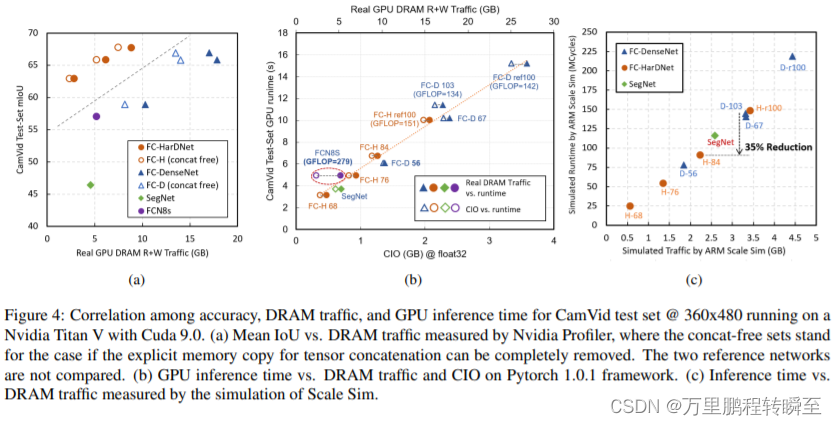

我们建议使用表3中指定的FC-HarDNet84,以便与FC-DenseNet103进行比较。新网络的CIO减少了41%,GPU推理时间减少了35%。一个更小的版本,FC-HarDNet68,也比FC-DenseNet56少了65%的CIO,少52%的GPU推理时间。我们研究了精度、DRAM流量和GPU推理时间之间的相关性。图4a显示,HarDNet的DRAM流量准确率最高。从图4b可以看出,GPU推理时间与DRAM流量的相关性确实远远大于MACs。它还表明,CIO是一个很好的近似于实际的DRAM流量,除了FCN8s是一个由于其使用了大的卷积内核的异常值。

为了验证硬件平台上的推理时间和内存流量之间的相关性,我们采用了ARM规模Sim进行研究。它是一个ARM收缩期阵列的循环精确模拟工具,类似与Eyeriss。请注意,该工具不支持deconvolution,并将这些deconvolution视为普通的卷积层。从图4c可以看出,DRAM流量与ScaleSim上的推理时间之间的相关性仍然很高,与FC-DenseNet-103相比,FC-HarDNet-84仍然减少了35%的推理时间。但这也表明,在GPU上SegNet的相对推断时间要差得多。因此,它证实了不同平台之间的相对DRAM流量可能会有很大的不同。

Pleiss等人已经提到,与DenseNet实现存在一个连接开销,这是由从现有张量的显式张量复制到一个新的内存分配引起的。因此,它会导致额外的DRAM流量。为了证明HarDNet仍然优于DenseNet,我们将张量连接的流量减去DRAM流量,如图4a所示的连接的DRAM流量由Nvidia分析器测量,并分解为数据批量复制函数。图4a显示,与FC-HarDeNet相比,FC-DenseNet可以通过折扣连接减少更多的DRAM流量,但后者仍然优于前者。

4.2. ImageNet Datasets

为了训练6个HarDNet模型的ImageNet分类任务,我们重用了来自[16,18]的torch 1.7训练环境,并将所有超参数与它们对齐。为了与其他先进的CNN架构,如ResNeXt和MobileNetV2[31]相比,我们采用了更先进的超参数,如余弦学习率衰减和微调的权值衰减。HarDNet-68/39DS模型的训练采用的批量大小为256,初始学习率为0.05,余弦学习率衰减,权重衰减为6e-5。

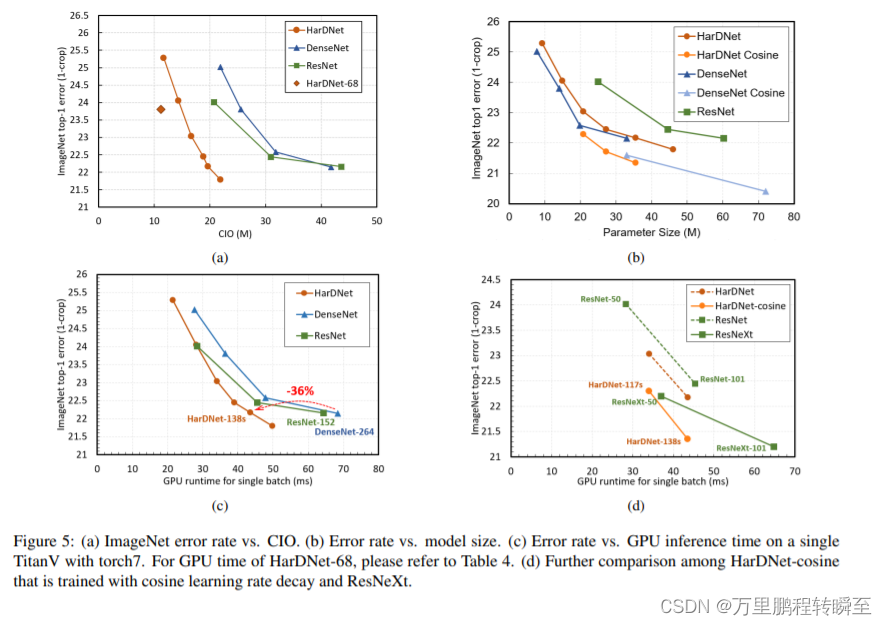

研究CIO的精度表明,HarDNet可以优于ResNet和DenseNet,而模型大小的精度介于两者之间,如图5(a)(b).所示图5c显示了使用torch 1.7对NvidiaTitanV的GPU推断时间结果,这与图5a的趋势非常相似,再次显示了CIO和GPU推断时间之间的高度相关性。然而,结果也表明,对于小模型,与ResNet相比,HarDNet的GPU推理时间没有改善,我们认为这是由于层数和连接成本造成的。我们还认为,一旦一个不连续的输入tensor可以被卷积运算支持,DenseNet和HarDNet的推理时间将进一步减少。

在图5d中,我们将最先进的CNN模型ResNeXt与我们使用余弦学习率衰减训练的模型进行了比较。尽管ResNeXt在相同的模型大小下实现了显著的精度提高,但这些模型仍然存在推理时间开销。由于ResNeXt没有增加mac,所以开销可以用CIO的增加来解释。

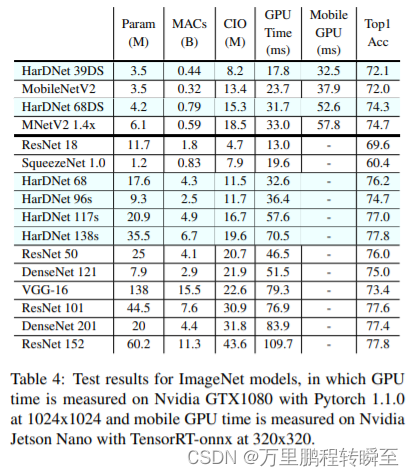

在表4中,我们展示了在ImageNet上CIO排序的结果比较,其中还包括HarDNet68/39DS。随着层数的减少、全局密集连接的取消以及BN-reordering,HarDNet-68从ResNet-50中实现了显著的推理时间减少。为了进一步比较使用标准卷积的模型和使用深度可分离卷积的模型粉粉之间的CIO,我们可以对后者的CIO应用0.6等权重。加权后,当比较两种非常不同的模型时,CIO仍然可以是对推理时间的粗略预测。

4.3. Object Detection

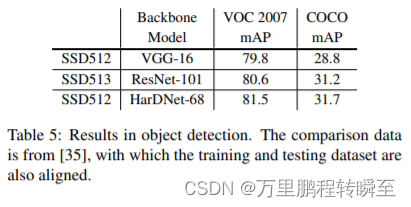

我们评估了HarDNet-68作为单阶段探测器(SSD)的主干模型,并使用pascal VOC2007和MS COCO数据集对其进行训练。与SSD-VGG对齐,我们在stride 8和stride 16中将一个预先训练过的HargeNet-68附加在最后一层的SSD上,相应的是HDB中的stride 32被丢弃。我们在HDB的 stride 16后插入一个桥接模块。桥模块包括一个步幅为1的3x3最大池化,一个3x3的卷积,以及一个点向卷积,其中两个卷积层都有640个输出通道。我们分别对VOC和COCO数据集进行了300个和150个epoch的训练模型。初始学习速率为0.004,在总时期的60%、80%、90%的60%时衰减0.1,COCO和VOC的重量衰减分别为1e-4和5e-4。表5中的结果显示,尽管我们的模型在ImageNet101中的精度较低,但它与SSD-ResNet101的精度相似,这表明了我们对32层的stride 8增强的有效性,提高了小尺度对象的局部特征学习。此外,HarDNet-68比VGG-16和ResNet-101都要快得多,这使得它在实时应用中非常具有竞争力。

5. Discussion

CIO有一个假设,这是一个CNN模型,逐层处理,不需要融合。相比之下,提出了针对多卷积层的融合层计算方法[1],其中融合层组中的中间层不会为特征映射产生任何内存流量。在这种情况下,MobileNetV2中的倒残差模块可能是实现低内存流量的更好的设计。此外,深度级卷积在相邻层之前或之后实现为元素级操作。在这种情况下,关于深度卷积的CIO应该被打折扣。

结果表明,在某些情况下,CIO仍然无法预测实际的推理时间,如比较两个架构有显著不同的网络模型。正如我们前面提到的,CIO只有在MoC低于一定比例时才会主导推理时间,这是一个数据流量空间内的计算密度。在一个网络模型中,每个层都有一个不同的MoC。在某些层中,CIO可能占主导地位,但对于其他层,如果其计算密度相对较高,它仍然可能是关键因素。为了精确地预测网络的推理延迟,我们需要对每个层进行分解,并研究其MoC来预测该层的推理延迟。

我们还想进一步强调DRAM流量的重要性。由于量化方法已被广泛应用于CNN模型中,因此可以降低算子的硬件成本和数据流量。然而,从float32到int8的硬件成本的降低远远大于来自同一事物的数据流量的减少。当开发主要使用int8乘数器的硬件平台时,计算能力可以比数据带宽增长得更快,因此在这种情况下,数据流量将更加重要。我们认为,实现流量减少的最佳方法是合理地增加网络模型的MoC,这可能与被广泛接受的使用更多的Conv1x1可以实现更高的效率相反。然而,在许多情况下,我们已经证明了它确实是有用的。

6. Conclusion

我们提出了一种新的度量方法来评估卷积神经网络,通过估计其特征图的DRAM流量,这是影响系统功耗的一个关键因素。当计算密度较低时,流量可以比模型大小和操作计数更显著地影响推理时间。我们使用卷积输入/输出(CIO)作为DRAM流量的近似值,并提出了一种谐波密集连接网络(HarDNet),该网络通过增加计算密度(MACs超过CIO)来实现高于CIO的精度,并实现高计算效率。

实验表明,与FC-DenseNet相比,所提出的连接模式和信道平衡使FC-HarDNet减少了40%的DRAM流量,GPU推理时间减少了35%。与DenseNet-264和ResNet-152相比,HarDNet-138s实现了相同的精度,GPU推理时间减少了35%。与ResNet-50相比,HarDNet-68实现了30%的推理时间减少,这也是一个理想的对象检测主干模型,提高了SSD的准确性,比使用ResNet-101更高,同时推理时间也从SSD-VGG显著减少。总之,除了精度超过模型大小和精度超过mac的权衡外,我们证明了超过DRAM流量的特征图的精度确实是设计神经网络架构时的一个重要考虑因素。