12.1 实践版OpenMIPS处理器的设计目标

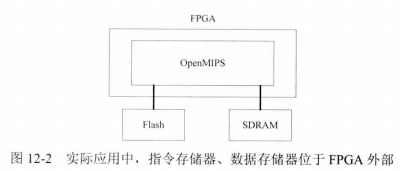

但在实际应用中,程序的体积可能非常大,指令存储器不能集成在FPGA内部了,一般使用FPGA芯片外部的Flash作为指令存储器,同理,一般使用FPGA芯片外部的SDRAM作为数据存储器。

因此,为了使OpenMIPS实用化,需要为其添加Flash控制器,SDRAM控制器:

- 更进一步,如果要使用FPGA外部SRAM,那么需要再为OpenMIPS添加SRAM控制器,如果要使用串口,那么需要再为OpenMIPSt添加UART控制器。由此出现一个问题,每添加一个设备都需要修改OpenMIPS,这种做法不具有良好的扩展性。

- 参考常用的PC,其一般都提供PCI总线接口,各种板卡只要满足PCI总线接口标准,就可以直接插在PC的PCI插槽使用,十分方便,并不需要修改处理器。借鉴这种方式,我们只需要为OpenMIPS添加通用总线接口,就可以方便地接入新设备。OpenMIPS通过总线接口挂在总线上,各种外部设备的控制器也挂在总线上。

- 因为OpenMIPS采用哈佛结构,所以有两个总线接口,分别是指令总线接口和数据总线接口。

- 各种控制器都可以直接使用已有的IP核,为了方便不同研发者或公司的IP核能够相互连接,要求这些IP核遵守相同的总线规范。总线规范定义了IP核之间的通用接口。该书实践版OpenMIPS采用Wishbone总线规范。

- 实践版就是在教学版OpenMIPS处理器基础上添加Wishbone总线接口,这样就能方便地将其挂接在Wishbone总线上,从而可以使用大量开源的SDRAM,Flash,GPIO,UART,LCD等模块的控制器,组成一个SOPC,完成特定功能,成为一个能发挥实际作用的处理器。

12.2 Wishbone总线介绍

12.2 Wishbone总线介绍

12.2.1 Wishbone总线接口说明

(1)CLK_1、RST_1:分别是时钟信号、复位信号、由外部输入

(2)DAT_O/DAT_I:数据总线

(3)ADR_O/ADR_I:地址总线,地址由主设备传送给从设备

(4)WE_O/WE_I:写使能信号, 主设备传给从设备

(5)SEL_O/SEL_I:数据总线选择信号,用于标识当前操作中,数据总线上哪些比特是有效的,以总线粒度为单位:如:一个32位宽,粒度为一个字节8位,则数据总线选择信号应该定义为:SEL_O(3:0)/SEL_I(3:0),此时,SEL_O(4’b1001)就代表当前操作中数据总线的最高和最低字节有效

(6)CYC_O/CYC_I:总线周期信号,有效代表一个主设备请求总线使用权或者正在占有总线。

(7)STB_O/STB_I:选通信号。有效代表主设备发起一次总线操作。只有选通信号有效时,ADR_O/ADR_I、DAT_O/DAT_I、SEL_O/SEL_I才有意义

(8)ACK_O/ACK_I:都是主从设备间的操作结束信号。

12.2.2 Wishbone总线单次读操作的过程

12.2.3 Wishbone总线单次写操作的过程

在时钟上升沿1到达之前,从设备检测到主设备发起的操作,于是锁存DAT_O的数据,同时将主设备的输入ACK_I置高,作为对主设备STB_O的响应。从设备可以在设置ACK_I有效之前,插入任意数量的等待状态。

12.3 实践版OopenMIPS处理器接口

将之前指令存储器、数据UN初期接口分别换成指令Wishbone总线接口、数据Wishbone总线接口,其余未变。

12.4 实践版OpenMIPS处理器的实现思路

说明:

由于指令存储器是只读的,并且指令宽度固定为32位,所以取指阶段添加的Wishbone总线接口模块的输入cpu_data_i直接设置为32’h00000000;cpu_we_i固定为1’0,表示始终读操作;cpu_sel_i固定为4‘b1111.

12.5 从教学版OpenMIPS到实践版OpenMIPS

12.5.1 Wishbone总线接口模块的实现

采用有限状态机实现wishbone总线接口模块,定义三个状态:空闲状态,总线忙状态,等待结束状态

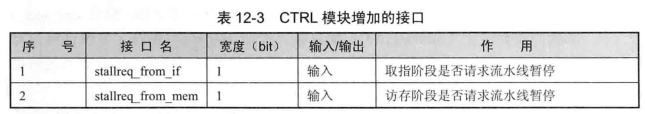

12.5.2 修改CTRL模块