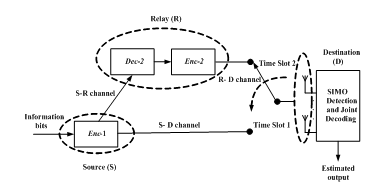

简化后系统模型(此模型里不用VBALST,接收端仍然用联合迭代检测)

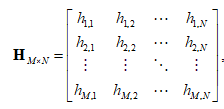

Let a sparse parity-check matrix of a binary regular LDPC code be

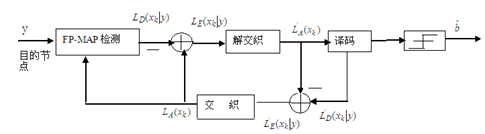

BPSK调制,采用球形FP-MAP的接收端迭代检测模型,

来仿真系统误码率图(最后出来2个图)(请给出球形译码的初始半径等相关参数说明)

图1)先给出外部迭代一次时LDPC译码迭代几次图(通过这个图找出稳定次数)

图2)以LDPC译码稳定迭代次数为参考,在给出外部迭代2次,3次,4次的误码率比较图

(目的:下面这个图是上述的系统模型和参数在正常BP算法直接译码的结果,没有联合MIMO检测迭代,所以这次的目的是像用之前我们做的迭代检测来与直接LDPC译码的BP算法的性能比较优劣

(比较的性能参考图,没有球形译码迭代的)

说明:

由于,这里我们所采取的,其参数远远大于最早我们所做的512,256的参数。所以第二题,虽然模型结构简化了,但是整个系统的仿真时间大大增加了,幸亏实现做的时候,我事先申请了服务器,哎,,如果后面有修改的话,尽量放周末,服务器大概仿真了20多个小时。

代码设计说明(因为这个部分的代码的联合迭代部分和第一个课题详细,所以这里直接给出仿真结果并进行简单的说明)

对于LDPC部分,我们单独仿真一个文件夹中。

发送端,首先进行LDPC编码,根据你的要求

要求:使用上述的系统模型和两个不同LDPC编码用在源节点和中继节点上,(强调)中继节点是先译码源节点的信息后,在进行第二次编码的,在慢衰落的瑞利信道环境下(强调一下),BPSK调制,采用球形FP-MAP的接收端迭代检测模型,

我们在源节点上,使用1000.600这组参数的LDPC进行编码,然后在中继节点上采用2000,1000这组参数的LDPC进行编码,发送端为1个天线,而接收端为2个天线,且采用非VBLAST结构。即在接收端,采用时间间隔的方式分别对源节点的发送信号和中继节点的发送信号进行接收。通过的信道为瑞利信道。

此外,发送端采用1方式的LDPC译码,而中继采用2方式的LDPC译码,则对于在进行2编译码的时候,对于每帧数据,缺少的数据,则采用加入虚拟填充符的方式进行。具体如下所示:

仿真结果如下所示:

由于这个代码仿真时间非常长,

所以,这里,我们仅给出内部迭代次数为5,10,15,20这么几组仿真结果

从上面的仿真结果可知,当迭代次数为20的时候,和15的时候,其编码增益提升非常小,说明当迭代次数为15的时候,系统已经稳定,因此,内部迭代次数,我们选择15.

然后对于外部迭代,还是仿真迭代次数为1,2,3,4的仿真结果。

从上面的仿真结果可知,外部迭代四次的时候,系统基本稳定(仿真图中,由于当迭代次数为2的时候,在SNR为6的时候,性能较好,是在没法仿真过去了,耗时间太久,所以没仿真,依次,迭代为3,4的时候,SNR为5.5和6这两个点没仿真,时间太久了)