这个问题很简单,前面的很多博文也多多少少提到了这个问题,(如:Verilog HDL 使用规范(一)),今天就系统地理一遍。

Verilog HDL设计中容易犯的一个通病就是不正确使用语言,生成了并不想要的锁存器。下面给出两种情形:

情形一:

不恰当地使用 if 语句

1.1 有锁存器的代码:

always @(al or b)

begin

if(al) q <= b;

end

这个“always”块中,if语句保证了只有al = 1时, q才取 d 的值。这段程序没有写出al = 0时的结果,那么当al = 0时会怎么样呢?变量q保持原来的值。

1.2 无锁存器的代码:

always @(al or b)

begin

if(al) q <= b;

else q <= 0;

end这个“always”块中,相对于上一段代码的不同之处在于当al = 0 时,给了q一个值0。

总结上面的两段代码,如果在给定的条件下变量没有赋值,这个变量就会保持原值,也就是会生成一个锁存器。

如果设计人员希望当al = 0时,q值为0,else项就必不可少了,注意1.2的代码中的“always”块,整个Verilog HDL程序模块被综合出来后,always块对应的部分不会生成锁存器。

情形二:

不恰当使用case语句

Verilog HDL程序另一种偶然生成锁存器的情况是使用case语句时缺少default项的情况下发生的。

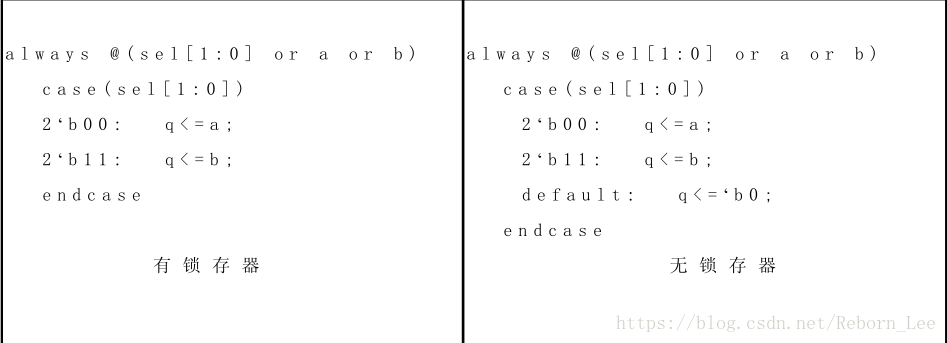

case语句的功能是:在某个信号(本例中的sel)取不同的值时,给另一个信号(本例中的q)赋不同的值。注意看下图左边的例子,如sel=00,q取a值,而sel=11,q取b的值。这个例子中不清楚的是:如果sel取00和11以外的值时q将被赋予什么值?在下面左边的这个例子中,程序是用Verilog HDL写的,即默认为q保持原值,这就会自动生成锁存器。

右边的例子很明确,程序中的case语句有default项,指明了如果sel不取00或11时,编译器或仿真器应赋给q的值。程序所示情况下,q赋为0,因此不需要锁存器。

以上就是怎样来避免 偶然生成锁存器的错误。如果用到if语句,最好写上else项。如果用case语句,最好写上default项。遵循上面两条原则,就可以避免发生这种错误,使设计者更加明确设计目标,同时也增强了Verilog程序的可读性。