1. 实践得到的启发

先从一个简单的现象得出结论,Verilog语句是并发执行的!

同时,这也是**$monitor系统任务为全局有效**的一个重要支持因素,如果没有并发,它是完不成这项功能的实现的。

众所周知,高级语言通常都是自上而下编译和执行的,但是Verilog硬件描述语言不一样,它更喜欢并发执行。

这是一门直接触及底层硬件编程的语言,效率非常高,并发执行是为了适应它所处的环境。

先来看看一下激励块代码:

module stimulus;

// 设置激励信号

reg I0 = 1,I1 = 0,I2 = 1,I3 = 0,I4 = 1,I5 = 0,I6 = 1,I7 = 0; // 输入数据信息

reg S2,S1,S0; // 地址输入端信息,注意使用“小端序”

wire OUT; // 输出数据

mux8_to_1 M8T (I0,I1,I2,I3,I4,I5,I6,I7,S2,S1,S0,OUT);

// 设置信号监视器

initial

begin

$monitor ($time," S2 = %b, S1 = %b, S0 = %b, OUT = %b\n",S2,S1,S0,OUT); // 注意【\n】

end

// 设置激励信号

initial

begin

// $display ("I0 = %b, I1 = %b, I2 = %b, I3 = %b, I4 = %b, I5 = %b, I6 = %b, I7 = %b\n"

// ,I0,I1,I2,I3,I4,I5,I6,I7);

#1 S2 = 0; S1 = 0; S0 = 0;

#1 S2 = 0; S1 = 0; S0 = 1;

#1 S2 = 0; S1 = 1; S0 = 0;

#1 S2 = 0; S1 = 1; S0 = 1;

#1 S2 = 1; S1 = 0; S0 = 0;

#1 S2 = 1; S1 = 0; S0 = 1;

#1 S2 = 1; S1 = 1; S0 = 0;

#1 S2 = 1; S1 = 1; S0 = 1;

end

endmodule

输出结果为:

0 S2 = x, S1 = x, S0 = x, OUT = x

1 S2 = 0, S1 = 0, S0 = 0, OUT = 1

2 S2 = 0, S1 = 0, S0 = 1, OUT = 0

3 S2 = 0, S1 = 1, S0 = 0, OUT = 1

4 S2 = 0, S1 = 1, S0 = 1, OUT = 0

5 S2 = 1, S1 = 0, S0 = 0, OUT = 1

6 S2 = 1, S1 = 0, S0 = 1, OUT = 0

7 S2 = 1, S1 = 1, S0 = 0, OUT = 1

8 S2 = 1, S1 = 1, S0 = 1, OUT = 0

观察可得,不仅仅两个initial块是并发执行的,并且他们还是从仿真时刻为0的时候就开始并发执行了。

【疑问】(未解决)

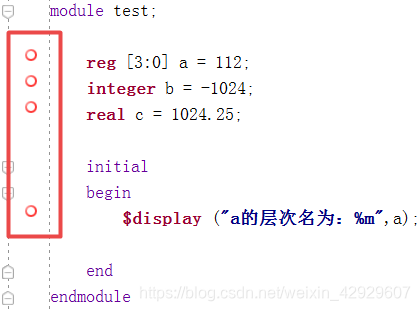

Vivado 2017.4中

红圈圈是意味着并发执行吗?暂时不知道,后续再研究。

——————————

后续深入内容以后再说