The first is the clock system diagram

In the block diagram of the entire system, the external high-speed oscillator (12Mhz) crystal oscillator is to be configured this time, so only focus on the configuration in the upper left corner.

External Oscillator Configuration Location

Xtal_in: High speed oscillator input Xtal32_in: Low speed 32k oscillator input

Talk about the configuration process (12M crystal oscillator as an example):

A. XTAL_IN is connected to an external 12M crystal oscillator, the system selects the external crystal oscillator, and needs to initialize the external crystal oscillator:

stc_clk_xtal_cfg_t stcXtalCfg; /* 高速外部振荡器 */

/* 外部高速振荡器初始化 */

MEM_ZERO_STRUCT(stcXtalCfg);

stcXtalCfg.enMode = ClkXtalModeOsc; /* 配置振荡器 */

stcXtalCfg.enDrv = ClkXtalLowDrv; /* 12M晶振属于低速驱动能力 */

stcXtalCfg.enFastStartup = Enable; /* 使能快速启动 */

CLK_XtalConfig(&stcXtalCfg); /* 配置参数 */

CLK_XtalCmd(Enable); /* 使能振荡器 */

B. The internal sram also needs to be configured (the main reference manual):

The configuration is as follows:

stc_sram_config_t stcSramConfig;/* sRam配置 */

/* sram */

stcSramConfig.u8SramIdx = Sram12Idx | Sram3Idx | SramHsIdx | SramRetIdx;

stcSramConfig.enSramRC = SramCycle2; /* 等待周期 参考上图表8-1 */

stcSramConfig.enSramWC = SramCycle2;

/*

参考: 8.2.3 SRAM 校验控制寄存器( SRAM_CKCR)

若1位错误,ECC纠错, 产生1位错误标志,产生中断/复位

若2位错误,ECC检错, 产生2位错误标志,产生中断/复位

*/

stcSramConfig.enSramEccMode = EccMode3; /* 校验模式选择 */

stcSramConfig.enSramEccOp = SramNmi; /* ecc校验失败不产生NMI中断*/

stcSramConfig.enSramPyOp = SramNmi; /*奇偶校验出错后不产生NMI中断 */

SRAM_Init(&stcSramConfig); /* SRAM初始化 */

EFM_Unlock(); /* 解锁flash配置寄存器 */

/* 配置延迟周期(参考表3),这个参数跟HCLK配置频率有关系 */

EFM_SetLatency(EFM_LATENCY_5);

EFM_Lock(); /* 上锁 */

C. Configure PLL (output after VCO frequency multiplication)

计算方式:

1. 输入晶振频率/分频系数 *倍频系数 得到PLL时钟源(VCO)

2. PLL再进行分频

MPLL:用于cpu,io及外设i2c等

uPLL: 主要用于usb外设

| PLL | qPLL | pPLL | rPLL |

| MPLL | MqPLL |

MpPLL |

MrPLL |

| UPLL | UqPLL |

UpPLL |

MrPLL |

计算12M晶振输出:

计算公式:

PLL(VCO)= xtal(12)/ pllmDiv(3) * plln(100) = 400M

晶振输入频率12M先进行分频,得到稳定的4M然后倍频到400MHz,然后在进行分频给p,q,r;The code configuration is as follows:

stc_clk_mpll_cfg_t stcMpllCfg; /* MPLL 倍频/分频器 配置 */

/* MPLL config (XTAL / pllmDiv * plln / PllpDiv = 200M). */

/* 分频系数 (12M)晶振频率/(3)mdiv*(100)plln = MPLL频率 400MHz */

stcMpllCfg.pllmDiv = 3ul;

stcMpllCfg.plln = 100ul; /* 倍频系数 *100 = 400M */

/* MPLL_P 分频系数 MPLL频率/p = MPLL_P频率 200MHz */

stcMpllCfg.PllpDiv = 2ul;

/* MPLL_Q 分频系数 MPLL频率/q = MPLL_Q频率 200MHZ */

stcMpllCfg.PllqDiv = 2ul;

/* MPLL_R 分频系数 MPLL频率/r = MPLL_R频率 200MHZ */

stcMpllCfg.PllrDiv = 2ul;

CLK_SetPllSource(ClkPllSrcXTAL); /* 配置时钟源 外部高速振荡器 */

CLK_MpllConfig(&stcMpllCfg); /* 配置MPLL参数 */

/* 使能MPLL. */

CLK_MpllCmd(Enable);

Then configure the system clock source:

stc_clk_sysclk_cfg_t stcSysClkCfg; /* 系统时钟 */

/* 系统时钟配置 */

MEM_ZERO_STRUCT(stcSysClkCfg);

/* 12M/2 *100 = 400M(PLL) */

stcSysClkCfg.enHclkDiv = ClkSysclkDiv2; /* 200M ,max 200MHz */

stcSysClkCfg.enExclkDiv = ClkSysclkDiv4;/* 100M ,max 100MHz */

stcSysClkCfg.enPclk0Div = ClkSysclkDiv4;/* 100M ,max 100MHz */

stcSysClkCfg.enPclk1Div = ClkSysclkDiv8;/* 50M ,max 60MHz */

stcSysClkCfg.enPclk2Div = ClkSysclkDiv8;/* 50M ,max 50MHz */

stcSysClkCfg.enPclk3Div = ClkSysclkDiv4;/* 100M ,max 100MHz */

stcSysClkCfg.enPclk4Div = ClkSysclkDiv4;/* 100M ,max 100MHz */

CLK_SysClkConfig(&stcSysClkCfg);

The configuration should be carried out according to the manual. If the ratio is wrong, the configuration will be successful, and it will not be available after burning!

The reference documents for bus clock configuration are as follows:

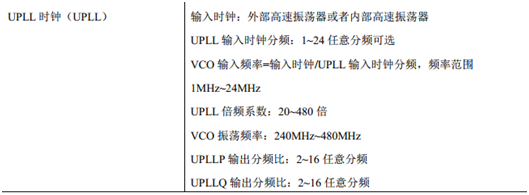

Here is pll (VCO) related parameter settings for frequency multiplication and frequency division:

a. Input crystal frequency division factor: 1~24

b. Multiplication factor: 20~480

c. Output frequency after frequency doubling: If it exceeds the range between 240M and 480M, it will be abnormal

d. P, Q, R (pll) frequency division factor: 2~16

e. Upll is configured in the same way as mpll

The required maximum frequency is obtained above, and the actual frequency needs to be configured for the system clock:

Referring to the maximum frequency range of the clock in the figure above, we can get the frequency division factor we need:

enHclkDiv: HCLK时钟 max 200MHZ

enExclkDiv:EXCLK时钟 max100Mhz

enPclk0Div: EXCLK时钟 max100Mhz

enPclk1Div: EXCLK时钟 max50Mhz

enPclk2Div: EXCLK时钟 max50Mhz

enPclk3Div: EXCLK时钟 max100Mhz

enPclk4Div: EXCLK时钟 max100Mh

在之前配置Mpll的时候 我们配置到了400Mhz

| bus |

MPLL = 400MHz/division factor |

Frequency after frequency division |

| HCLK |

2 |

200Mhz |

| PCLK0 |

2 |

200Mhz |

| PCLK1 |

4 |

100Mhz |

| PCLK2 |

8 |

50Mhz |

| PCLK3 |

8 |

50Mhz |

| PCLK4 |

4 |

100Mhz |

| EXCLK |

4 |

100Mhz |

Although the configuration is complete here, you need to pay attention to the frequency ratio in the document:

There is basically no problem in configuring the clock according to the above operations. Note that the PLL (VCO) needs to be within the output range after multiplication.

EX:

Here is an example to illustrate my own wrong configuration:

以下是错误示范,请勿直接使用代码

12M外部输入晶振

MPLL:

mPLL=12M/3* 42 = 168Mhz

MPLL 分频参数: 3

MPLL 倍频参数: 42

然后PQR使用2分频 得到 84MHz

Configure the system clock (incorrect configuration example):

| bus |

MPLL = 168MHz/division factor |

Frequency after frequency division |

| HCLK |

1 |

168Mhz |

| PCLK0 |

1 |

168Mhz |

| PCLK1 |

2 |

84Mhz |

| PCLK2 |

4 |

42Mhz |

| PCLK3 |

4 |

42Mhz |

| PCLK4 |

2 |

100Mhz |

| EXCLK |

2 |

84Mhz |

The above configuration is also configured according to the required coefficients in the document but it does not work in practice.

Finally found the cause of the configuration error, the PLL (VCO) output frequency is not within the output range (240M-480M).

The correction parameters are as follows:

此处是修正代码(可以正常使用)

12M外部输入晶振

MPLL:

mPLL=12M/3* 84 = 338Mhz

MPLL 分频参数: 3

MPLL 倍频参数: 84

然后PQR使用2分频 得到 168MHz

Configure the system clock:

| bus |

MPLL = 168MHz/division factor |

Frequency after frequency division |

| HCLK |

2 |

168Mhz |

| PCLK0 |

2 |

168Mhz |

| PCLK1 |

4 |

84Mhz |

| PCLK2 |

8 |

42Mhz |

| PCLK3 |

8 |

42Mhz |

| PCLK4 |

4 |

84Mhz |

| EXCLK |

4 |

84Mhz |

Now the system is running normally!

When modifying the system clock, you need to make corresponding modifications to EFM:

关于sram部分的修改这里没有继续写出,参考 sram延迟周期即可(根据运行频率选择对应等待周期即可)

EFM_Unlock();

EFM_SetLatency(EFM_LATENCY_4);/* 对应HCLK主频 */

EFM_Lock();

After this configuration, the code runs without any problems.

continued:

It's not over yet (three configuration clock schemes are posted here):

Option One:

void system_clk_init(void) /* 12M晶振, 3分频 84倍频输出 PLL(VCO)== 336M */

{

stc_clk_sysclk_cfg_t stcSysClkCfg; /* 系统时钟 */

stc_clk_xtal_cfg_t stcXtalCfg; /* 高速外部振荡器 */

stc_clk_xtal32_cfg_t stcXtal32Cfg; /* 外部低速振荡器 */

stc_clk_mpll_cfg_t stcMpllCfg; /* MPLL 倍频/分频器 */

stc_sram_config_t stcSramConfig; /* sRam配置 */

/* 系统时钟配置 HCLK 168M */

MEM_ZERO_STRUCT(stcSysClkCfg);

/* 12M/2 =6M *56 = 336M(PLL) */

stcSysClkCfg.enHclkDiv = ClkSysclkDiv2; /* 168M ,max 200MHz */

stcSysClkCfg.enExclkDiv = ClkSysclkDiv4;/* 84M ,max 100MHz */

stcSysClkCfg.enPclk0Div = ClkSysclkDiv2;/* 168M ,max 200MHz */

stcSysClkCfg.enPclk1Div = ClkSysclkDiv4;/* 84M ,max 100MHz */

stcSysClkCfg.enPclk2Div = ClkSysclkDiv8;/* 42M ,max 60MHz */

stcSysClkCfg.enPclk3Div = ClkSysclkDiv8;/* 42M ,max 50MHz */

stcSysClkCfg.enPclk4Div = ClkSysclkDiv4;/* 84M ,max 100MHz */

CLK_SysClkConfig(&stcSysClkCfg);

/* 外部高速振荡器初始化 */

MEM_ZERO_STRUCT(stcXtalCfg);

stcXtalCfg.enMode = ClkXtalModeOsc; /* 配置振荡器 */

stcXtalCfg.enDrv = ClkXtalLowDrv; /* 12M晶振属于低速驱动能力 */

stcXtalCfg.enFastStartup = Enable; /* 使能快速启动 */

CLK_XtalConfig(&stcXtalCfg); /* 配置参数 */

CLK_XtalCmd(Enable); /* 使能振荡器 */

/* 外部低速振荡器初始化 */

MEM_ZERO_STRUCT(stcXtal32Cfg);

stcXtal32Cfg.enDrv = ClkXtal32MidDrv;

stcXtal32Cfg.enFilterMode = ClkXtal32FilterModeFull;

CLK_Xtal32Config(&stcXtal32Cfg);

CLK_Xtal32Cmd(Disable); /* 未使用禁用掉 */

/* 配置sram及PLL */

MEM_ZERO_STRUCT(stcMpllCfg);

MEM_ZERO_STRUCT(stcSramConfig);

/* sram */

stcSramConfig.u8SramIdx = Sram12Idx | Sram3Idx | SramHsIdx | SramRetIdx;

stcSramConfig.enSramRC = SramCycle2;

stcSramConfig.enSramWC = SramCycle2;

/*

若1位错误,ECC纠错, 产生1位错误标志,产生中断/复位

若2位错误,ECC检错, 产生2位错误标志,产生中断/复位

*/

stcSramConfig.enSramEccMode = EccMode3;

stcSramConfig.enSramEccOp = SramNmi;

stcSramConfig.enSramPyOp = SramNmi;

SRAM_Init(&stcSramConfig);

EFM_Unlock();

EFM_SetLatency(EFM_LATENCY_4);

EFM_Lock();

/* MPLL config (XTAL / pllmDiv * plln / PllpDiv = 168M). */

/* 分频系数 (12M)晶振频率/(3)mdiv*(84)plln = MPLL频率 336MHz */

stcMpllCfg.pllmDiv = 3ul;

stcMpllCfg.plln = 84ul; /* 倍频系数 *100 = 336M */

stcMpllCfg.PllpDiv = 2ul; /* MPLL_P 分频系数 MPLL频率/p = MPLL_P频率 168MHz */

stcMpllCfg.PllqDiv = 2ul; /* MPLL_Q 分频系数 MPLL频率/q = MPLL_Q频率 168MHZ */

stcMpllCfg.PllrDiv = 2ul; /* MPLL_R 分频系数 MPLL频率/r = MPLL_R频率 168MHZ */

CLK_SetPllSource(ClkPllSrcXTAL); /* 配置时钟源 外部高速振荡器 */

CLK_MpllConfig(&stcMpllCfg); /* 配置MPLL参数 */

/* Enable MPLL. */

CLK_MpllCmd(Enable);

if(SystemCoreClock > CLK_HP_FREQ /* 168M */){

CLK_SetSysClkSource(CLKSysSrcMPLL);

}else if( SystemCoreClock < CLK_HS_FREQ /* 8M */){

PWC_LS2HP();

CLK_SetSysClkSource(CLKSysSrcMPLL);

}else{

PWC_HS2HP();

CLK_SetSysClkSource(CLKSysSrcMPLL);

}

}Option II:

void system_clk_init(void) /* 12M晶振, 3分频 100倍频输出 PLL(VCO)== 400M */

{

stc_clk_sysclk_cfg_t stcSysClkCfg; /* 系统时钟 */

stc_clk_xtal_cfg_t stcXtalCfg; /* 高速外部振荡器 */

stc_clk_xtal32_cfg_t stcXtal32Cfg; /* 外部低速振荡器 */

stc_clk_mpll_cfg_t stcMpllCfg; /* MPLL 倍频/分频器 */

stc_sram_config_t stcSramConfig; /* sRam配置 */

/* 系统时钟配置 HCLK 200M */

MEM_ZERO_STRUCT(stcSysClkCfg);

/* 12M/2 =6M *56 = 336M(PLL) */

stcSysClkCfg.enHclkDiv = ClkSysclkDiv2; /* 200M ,max 200MHz */

stcSysClkCfg.enExclkDiv = ClkSysclkDiv4;/* 100M ,max 100MHz */

stcSysClkCfg.enPclk0Div = ClkSysclkDiv2;/* 200M ,max 200MHz */

stcSysClkCfg.enPclk1Div = ClkSysclkDiv4;/* 100M ,max 100MHz */

stcSysClkCfg.enPclk2Div = ClkSysclkDiv8;/* 50M ,max 60MHz */

stcSysClkCfg.enPclk3Div = ClkSysclkDiv8;/* 50M ,max 50MHz */

stcSysClkCfg.enPclk4Div = ClkSysclkDiv4;/* 100M ,max 100MHz */

CLK_SysClkConfig(&stcSysClkCfg);

/* 外部高速振荡器初始化 */

MEM_ZERO_STRUCT(stcXtalCfg);

stcXtalCfg.enMode = ClkXtalModeOsc; /* 配置振荡器 */

stcXtalCfg.enDrv = ClkXtalLowDrv; /* 12M晶振属于低速驱动能力 */

stcXtalCfg.enFastStartup = Enable; /* 使能快速启动 */

CLK_XtalConfig(&stcXtalCfg); /* 配置参数 */

CLK_XtalCmd(Enable); /* 使能振荡器 */

/* 外部低速振荡器初始化 */

MEM_ZERO_STRUCT(stcXtal32Cfg);

stcXtal32Cfg.enDrv = ClkXtal32MidDrv;

stcXtal32Cfg.enFilterMode = ClkXtal32FilterModeFull;

CLK_Xtal32Config(&stcXtal32Cfg);

CLK_Xtal32Cmd(Disable); /* 未使用禁用掉 */

/* 配置sram及PLL */

MEM_ZERO_STRUCT(stcMpllCfg);

MEM_ZERO_STRUCT(stcSramConfig);

/* sram */

stcSramConfig.u8SramIdx = Sram12Idx | Sram3Idx | SramHsIdx | SramRetIdx;

stcSramConfig.enSramRC = SramCycle2;

stcSramConfig.enSramWC = SramCycle2;

/*

若1位错误,ECC纠错, 产生1位错误标志,产生中断/复位

若2位错误,ECC检错, 产生2位错误标志,产生中断/复位

*/

stcSramConfig.enSramEccMode = EccMode3;

stcSramConfig.enSramEccOp = SramNmi;

stcSramConfig.enSramPyOp = SramNmi;

SRAM_Init(&stcSramConfig);

EFM_Unlock();

EFM_SetLatency(EFM_LATENCY_5);

EFM_Lock();

/* MPLL config (XTAL / pllmDiv * plln / PllpDiv = 200M). */

/* 分频系数 (12M)晶振频率/(3)mdiv*(100)plln = MPLL频率 400MHz */

stcMpllCfg.pllmDiv = 3ul;

stcMpllCfg.plln = 100ul; /* 倍频系数 *100 = 400M */

stcMpllCfg.PllpDiv = 2ul; /* MPLL_P 分频系数 MPLL频率/p = MPLL_P频率 200MHz */

stcMpllCfg.PllqDiv = 2ul; /* MPLL_Q 分频系数 MPLL频率/q = MPLL_Q频率 200MHZ */

stcMpllCfg.PllrDiv = 2ul; /* MPLL_R 分频系数 MPLL频率/r = MPLL_R频率 200MHZ */

CLK_SetPllSource(ClkPllSrcXTAL); /* 配置时钟源 外部高速振荡器 */

CLK_MpllConfig(&stcMpllCfg); /* 配置MPLL参数 */

/* Enable MPLL. */

CLK_MpllCmd(Enable);

if(SystemCoreClock > CLK_HP_FREQ /* 168M */){

CLK_SetSysClkSource(CLKSysSrcMPLL);

}else if( SystemCoreClock < CLK_HS_FREQ /* 8M */){

PWC_LS2HP();

CLK_SetSysClkSource(CLKSysSrcMPLL);

}else{

PWC_HS2HP();

CLK_SetSysClkSource(CLKSysSrcMPLL);

}

}third solution:

void system_clk_init(void)

{

stc_clk_sysclk_cfg_t stcSysClkCfg; /* 系统时钟 */

stc_clk_xtal_cfg_t stcXtalCfg; /* 高速外部振荡器 */

stc_clk_xtal32_cfg_t stcXtal32Cfg; /* 外部低速振荡器 */

stc_clk_mpll_cfg_t stcMpllCfg; /* MPLL 倍频/分频器 */

stc_sram_config_t stcSramConfig;/* sRam配置 */

/* 系统时钟配置 */

MEM_ZERO_STRUCT(stcSysClkCfg);

/* 12M/2 =6M *64 = 384M(PLL) */

stcSysClkCfg.enHclkDiv = ClkSysclkDiv2; /* 192M ,max 200MHz */

stcSysClkCfg.enExclkDiv = ClkSysclkDiv4;/* 96M , max 100MHz */

stcSysClkCfg.enPclk0Div = ClkSysclkDiv2;/* 192M , max 200MHz */

stcSysClkCfg.enPclk1Div = ClkSysclkDiv4;/* 96M , max 100MHz */

stcSysClkCfg.enPclk2Div = ClkSysclkDiv8;/* 48M , max 60MHz */

stcSysClkCfg.enPclk3Div = ClkSysclkDiv8;/* 48M , max 50MHz */

stcSysClkCfg.enPclk4Div = ClkSysclkDiv4;/* 96M , max 100MHz */

CLK_SysClkConfig(&stcSysClkCfg);

/* 外部高速振荡器初始化 */

MEM_ZERO_STRUCT(stcXtalCfg);

stcXtalCfg.enMode = ClkXtalModeOsc; /* 配置振荡器 */

stcXtalCfg.enDrv = ClkXtalLowDrv; /* 12M晶振属于低速驱动能力 */

stcXtalCfg.enFastStartup = Enable; /* 使能快速启动 */

CLK_XtalConfig(&stcXtalCfg); /* 配置参数 */

CLK_XtalCmd(Enable); /* 使能振荡器 */

/* 外部低速振荡器初始化 */

MEM_ZERO_STRUCT(stcXtal32Cfg);

stcXtal32Cfg.enDrv = ClkXtal32MidDrv;

stcXtal32Cfg.enFilterMode = ClkXtal32FilterModeFull;

CLK_Xtal32Config(&stcXtal32Cfg);

CLK_Xtal32Cmd(Disable); /* 未使用禁用掉 */

/* 配置sram及PLL */

MEM_ZERO_STRUCT(stcMpllCfg);

MEM_ZERO_STRUCT(stcSramConfig);

/* sram */

stcSramConfig.u8SramIdx = Sram12Idx | Sram3Idx | SramHsIdx | SramRetIdx;

stcSramConfig.enSramRC = SramCycle2;

stcSramConfig.enSramWC = SramCycle2;

/*

若1位错误,ECC纠错, 产生1位错误标志,产生中断/复位

若2位错误,ECC检错, 产生2位错误标志,产生中断/复位

*/

stcSramConfig.enSramEccMode = EccMode3;

stcSramConfig.enSramEccOp = SramNmi;

stcSramConfig.enSramPyOp = SramNmi;

SRAM_Init(&stcSramConfig);

EFM_Unlock();

EFM_SetLatency(EFM_LATENCY_5);

EFM_Lock();

/* MPLL config (XTAL / pllmDiv * plln / PllpDiv = 200M). */

stcMpllCfg.pllmDiv = 2ul; /* 分频系数 (12M)晶振频率/(2)mdiv*(64)plln = MPLL频率 384MHz */

stcMpllCfg.plln = 64ul; /* 倍频系数 *100 = 384M */

stcMpllCfg.PllpDiv = 2ul; /* MPLL_P 分频系数 MPLL频率/p = MPLL_P频率 192MHz */

stcMpllCfg.PllqDiv = 2ul; /* MPLL_Q 分频系数 MPLL频率/q = MPLL_Q频率 192MHZ */

stcMpllCfg.PllrDiv = 2ul; /* MPLL_R 分频系数 MPLL频率/r = MPLL_R频率 192MHZ */

CLK_SetPllSource(ClkPllSrcXTAL); /* 配置时钟源 外部高速振荡器 */

CLK_MpllConfig(&stcMpllCfg); /* 配置MPLL参数 */

/* Enable MPLL. */

CLK_MpllCmd(Enable);

if(SystemCoreClock > CLK_HP_FREQ /* 168M */){

CLK_SetSysClkSource(CLKSysSrcMPLL);

}else if( SystemCoreClock < CLK_HS_FREQ /* 8M */){

PWC_LS2HP();

CLK_SetSysClkSource(CLKSysSrcMPLL);

}else{

PWC_HS2HP();

CLK_SetSysClkSource(CLKSysSrcMPLL);

}

}Modify crystal parameters:

In system_hc32f460keta.h about:

#if !defined (XTAL_VALUE)

#define XTAL_VALUE ((uint32_t)8000000) /*!< External high speed OSC freq. */

#endif8M is used by default, we can define a 12M crystal oscillator parameter:

#define XTAL_VALUE ((uint32_t)12000000) /*!< External high speed OSC freq. */

#if !defined (XTAL_VALUE)

#define XTAL_VALUE ((uint32_t)8000000) /*!< External high speed OSC freq. */

#endif