Counter design exploration in FPGA, taking the counter as an example of 32 bits:

The first way is to define a 32-bit counter directly.

reg [31:0]count;

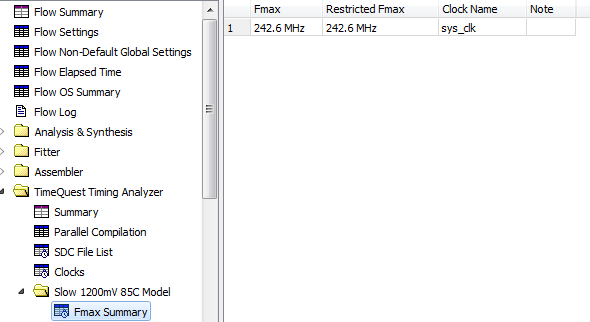

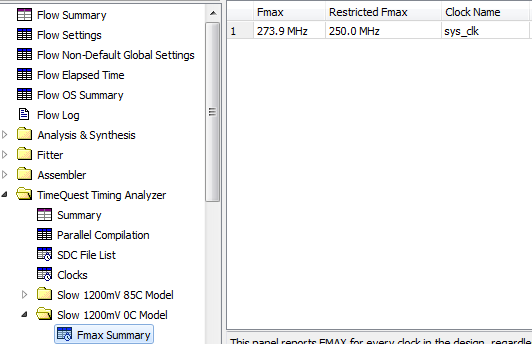

Compilation under quartus ii, resource consumption.

Clock frequency under 85C model.

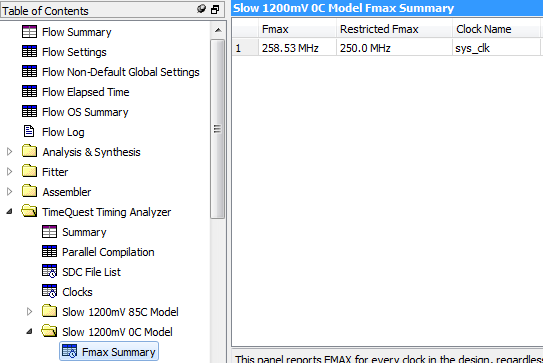

Clock frequency under 0C model.

Resource distribution under the chip planner.

The second way, define 2 16-bit counters.

reg [15:0]count1,count2;

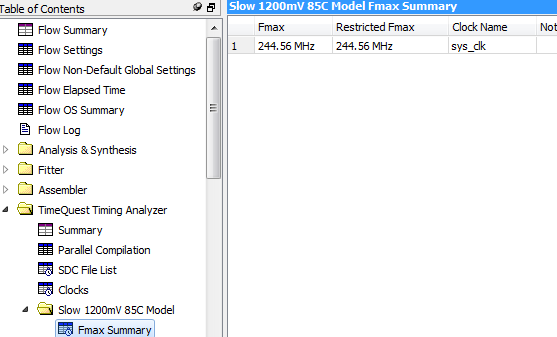

Compilation under quartus ii, resource consumption.

Clock frequency under 85C model.

Clock frequency under 0C model.

Resource distribution under chip planner

From the above two situations, combined with the structure of the C4 internal LAB, the two methods consume the same amount of resources, and the clock frequencies under the two models are relatively close.

It is worth noting that the above tests are tested under the condition that the resources are sufficient and the frequency is not high. According to experience, when more resources are used and the clock frequency is high, the second method is recommended.

Copyright ownership belongs to Qingcui Technology Hangzhou FPGA Division , please indicate the source for reprinting

Author: Hangzhou Qingcui Technology ALIFPGA

Original address: Hangzhou Qingcui Technology FPGA Geek Space WeChat Official Account

Scan the QR code to follow Hangzhou Qingcui Technology FPGA Geek Space