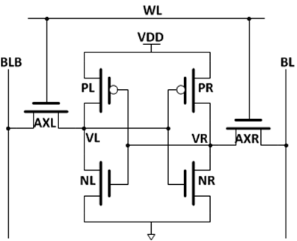

1.SPICE电路结构与网表

电路结构:

SPICE 网表:

*6T_SRAM CMOS

.OPTIONS LIST NODE POST

.lib 'gd018.l' TT

.OP

.TRAN 200P 100N

Mpl vl vr VDD VDD PCH L=1U W=20U

Mpr vr vl VDD VDD PCH L=1U W=20U

Mnl vl vr 0 0 NCH L=1U W=20U

Mnr vr vl 0 0 NCH L=1U W=20U

Maxl vl wl blb 0 NCH L=1U W=20U

Maxr vr wl bl 0 NCH L=1U W=20U

Vdd VDD 0 1.8

Vwl wl 0 PULSE 0 1.8 12N 1N 1N 6N 20N

Vblb blb 0 PWL 12N 0V, 22N 0V, 32N 0.9V, 42N 0.9V, 52N 1.8V, 62N 1.8V, 72N 0.9V, 82N 0.9V, 92N 0V, R 12N

Vbl bl 0 PWL 12N 1.8V, 22N 1.8V, 32N 0.9V, 42N 0.9V, 52N 0V, 62N 0V, 72N 0.9V, 82N 0.9V, 92N 1.8V, R 12N

C1 blb 0 50f

C2 bl 0 50f

.print tran i(Maxl)

.END

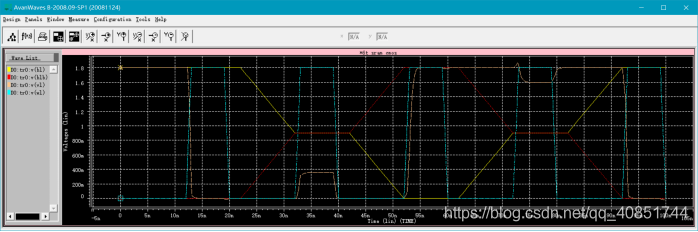

2.电路仿真结果-基础部分

V(bl):位线BL电压,是我们写入数据的“负值”,也就是说,如果写入数据为1,那么此

信号为低电平;当写入数据为0时,此信号为高电平。这里我给的是一个0~22ns为1.8V,

22ns~32ns下降到0.9V,32ns~42ns保持0.9V中位电平,42ns~52ns下降到0V低电平,

52ns~62ns保持0V低电平,62ns~72ns上升到0.9V中位电平,72ns~82ns保持0.9V中位

电平,82ns~92ns上升到1.8V高电平,然后保持12ns终止。

V(blb):位线BLB电压,是我们写入数据的“正值”,也就是说,如果写入数据为1,那么

此信号为高电平;当写入数据为0时,此信号为低电平。这里我给的是一个0~22ns为0V,

22ns~32ns上升到0.9V,32ns~42ns保持0.9V中位电平,42ns~52ns上升到1.8V高电平,

52ns~62ns保持1.8V高电平,62ns~72ns下降到0.9V中位电平,72ns~82ns保持0.9V中位

电平,82ns~92ns下降到0V低电平,然后保持12ns终止。

V(vl):vl节点电压,即存储器中的值。这里是我们的输出量。

V(wl):字线WL电压,是我们的输入写信号,这里我给的是一个输入高电平为1.8V,低

电平为0V,12ns延时,上升延时为1ns,下降延迟为1ns,脉冲宽度为6ns,周期为20ns

的周期信号

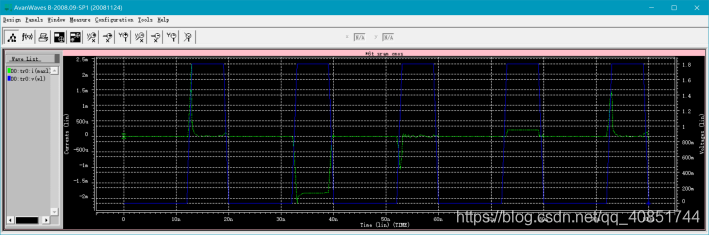

I(maxl):流过nmos管AXL电流

3.实验结果分析

写操作:WL处于高电平,向SRAM中写入数据,当写入数据为1时,blb位于高电平,bl为低电平,当写入数据为0时,blb位于低电平,bl为高电平。

保持状态:WL处于低电平,noms管均不导通。

读操作:bl和blb都达到VDD/2,此时,WL处于高电平。

1、SRAM是静态存储单元,由2个反相器组成的双稳态结构和两个开关组成,一共使用6个晶体管(6-T);其位线在源漏两端,字线在栅极,因此只有字线接通才能导通;两条位线分别是位线和位线取反,起到了平衡电路使其更加稳定的作用

2、对于读操作,假设当前数据为0,读的过程首先是进行预充,打开开关,字线选中,产生电流,BL流入电流,电压降低,非BL流出电流,电压升高,此时位线不再平衡,敏感放大器捕捉到左位线低右位线高,说明存的是0

3、对于写操作,若是想写入的值与当前值相同,则不产生电流,没有任何变化;若想写的与当前存的不同(假设当前为1,想写入0)那么数据端通过开关流出电流到位线,非BL通过开关流入电流到非D端;晶体管M5完全放电至0V,M6充电到VDD-VTN(虽然没有充到VDD,但在双稳态电路中,经过几次迭代就可变成标准高电压)