这个小项目几乎也就快结束了,中间因为要写开题报告所以落下了一段时间。经过前8次的讲解,想必相中也有了这个项目的大概框架;

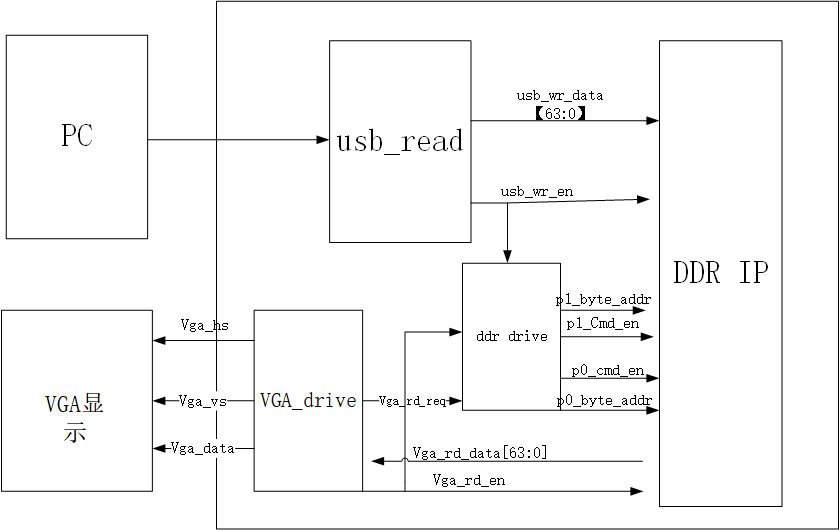

一、整体框架图

前几次我们都实现了,usb_read 模块,DDR IP模块,ddr_drive模块,整个小项目只剩下了,VGA的驱动模块。具体原理介绍如下:

二、关于本次要实现的模块的介绍

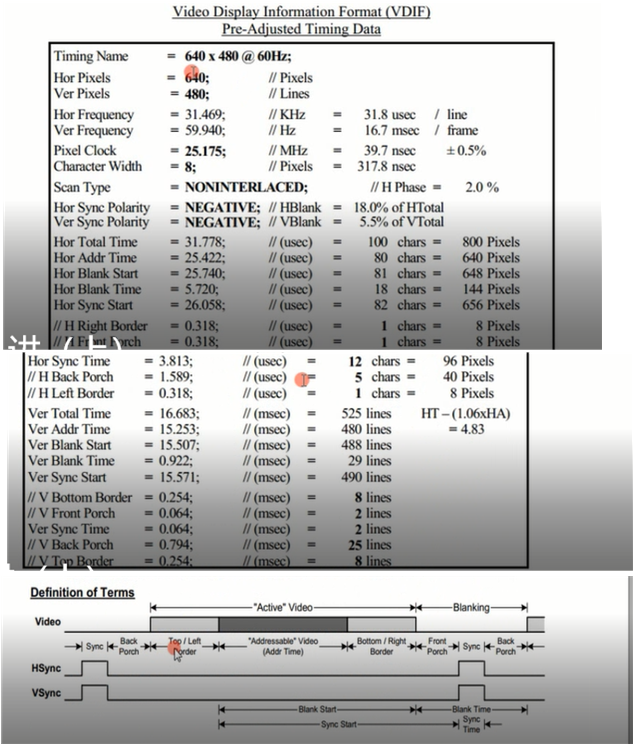

传送640*480的像素点的图片,vga_rd_data什么时候会出数据呢?因为我们用到的FIFO(指的是DDR中的FIFO)是fast_word模式,所以会在Vga_rd_en拉高的时候就直接出数据,并不会出现延迟的情况。这里我们的一次读是读出来了64bit的数据。然而VGA读出来的数据是16bit。这里需要进行对数据的拆分。也就是时序图中的Vga_rd_data[63:0]是从DDR中读出来的数据。但是在Vga_rd_en为低电平的时候,读出来的Vga_rd_data并不是不变的,因为Vga_data[15:0]是要直接给到VGA来显示的,所以应当先吧接收到的数据储存到寄存器Rd_data_reg[63:0]当中,然后对Rd_data_reg[63:0]中的数据进行拆分,在对Rd_data_reg[63:0]中的数据进行拆分时,必须保证里面的数据是已经准备好了的,所以在Vga_rd_en应该提前一拍,就是在行计数是142的时候拉高,然后Vga_rd_data[63:0]就会从DDR中把数据读出来,把读出来的数据缓存到Rd_data_reg[63:0]中,通过Vga_data[16:0]把Rd_data_reg[63:0]中的数据拆分成4个16bit的数据。可以发现Vga_rd_en每间隔4个时钟周期会拉高一次。用时序逻辑所以要提前一拍产生。需要产生让Rd_cnt相加的标志位Rd_cnt_add。一行最后一个像素点是144+639=783。需要将读使能拉高640/4=160次,对应的就是778是读使能的最后一次拉高。Byte_cnt用来拆分数据,Rd_cnt_add_r2拆分数据的标志位。

因为当P1的读使能拉高的时候,DDR中的读FIFO也不会立刻就有数据,但是我们必须保证,在VGA读使能有效的时候,FIFO中已经有了数据,所以FIFO中必须提前准备好要给VGA的数据,那就意味着ddr_drive 模块要先产生相应的读命令是能,vga_drive模块产生的读请求使能触发P1_cmd_en 使能。

P1_rd_cnt 单纯对VGA的读使能进行计数,VGA的读使能拉高一次进行一次自加,当加到16的时候会产生FIFO读空的情况。所以当P1_rd_cnt为16的时候再次拉高P1_cmd_en 进行向DDR中写入数据,但是这个时候向DDR中写入的时间,与读出的时间只有四个时钟周期的时间,所以容易产生错误,即将p1_rd_cnt 为1的时候,拉高P1_cmd_en。这里需要考虑读FIFO会不会读满的呢?因为这里设的读FIFO的深度为64,下一个VGA读使能到来的时候。FIFO里面最多也就是16个深度。字节地址开始自加一次自加128,突发次数计数器p1_bl_cnt,通过读请求Vga_rd_req来使得字节地址清0 。

DDR中的读写FIFO是一次突发16个数据每一个数据是64Bit,要传送的图像是640*480的像素点,每一个像素点是16bit,也就是一行像素点要突发640/64=10次,P1_cmd_en使能拉高10次,总共480行,也就是拉高4800次。因为在最初的vga_rd_req就会使得使能拉高一次,所以在一幅图片里面使能拉高了4801次,那么在传送第二幅图的时候就会有第一幅图的64个像素点在干扰。所以需要做一下限制。利用突发次数做限制,使其只能产生4800次。

xilinx芯片内部会对送入锁相环的时钟有个限制,当时钟送到PPL产生一个分频或者一个倍频时钟时,那么当前的时钟不能再送给其他pll作为时钟源的参考,驱动能力有限,会报错。最好就是再提供一个不同于之前的一个时钟源来做参考。

USB的高低字节会取反,所以出现的图像会色差比较厉害。

三、时序图的设计

四、相关事项

1、6480 X640 @60HZ 说明

2、硬件双端口时钟UCF约束

3、产生BIT文件时会报的约束错误

五、该模块编码

1 // ********************************************************************************* 2 // Project Name : 3 // Email : 4 // Website : 5 // Create Time : 6 // File Name : .v 7 // Module Name : 8 // Abstract : 9 // editor : sublime text 3 10 // ********************************************************************************* 11 // Modification History: 12 // Date By Version Change Description 13 // ----------------------------------------------------------------------- 14 // 2019/12/30 李国勇 1.0 Original 15 // 16 // ********************************************************************************* 17 `timescale 1ns/1ns 18 module vga_drive ( 19 //system signals 20 input wire sclk , 21 input wire s_rst_n , 22 //vga signals 23 output wire vga_hs , 24 output wire vga_vs , 25 output reg [15:0] vga_data , 26 //vga ctrl signals 27 output reg vga_rd_req , 28 output reg vga_rd_en , 29 input wire [63:0] vga_rd_data 30 31 ); 32 33 //========================================================================\ 34 // =========== Define Parameter and Internal signals =========== 35 //========================================================================/ 36 37 //640 X 480 @60HZ 38 localParam H_total_time = 800 ; 39 localParam H_sync_time = 96 ; 40 localParam H_back_porch = 40 ; 41 localParam H_left_border = 8 ; 42 localParam H_addr_time = 640 ; 43 44 localParam V_total_time = 525 ; 45 localParam V_sync_time = 2 ; 46 localParam V_back_porch = 25 ; 47 localParam V_top_border = 8 ; 48 localParam V_addr_time = 480 ; 49 50 51 reg [9:0] H_cnt ;//行计数器,总共是880 52 reg [9:0] V_cnt ;//列计数器,总共是525 53 reg [63:0] rd_data_reg ;//对从DDR中独处的数据的一个中间缓存器 54 reg [1:0] rd_cnt ;//对数据的拆分计数 55 reg rd_cnt_add ;//对拆分计数开始的标志位 56 reg [1:0] byte_cnt ;//拆分字节计数器 57 reg rd_cnt_add_r2 ;//拆分字节计数器开始标志位。相当于对数据拆分标志位延迟两个节拍 58 59 //============================================================================= 60 //**************************** Main Code ******************************* 61 //============================================================================= 62 63 assign vga_hs = (H_cnt < H_sync_time)? 1'b1 : 1'b0 ; 64 assign vga_hs = (V_cnt < V_sync_time)? 1'b1 : 1'b0 ; 65 66 //H_cnt 67 always @(posedge sclk or negedge s_rst_n)begin 68 if (!s_rst_n) 69 H_cnt <= 'd0 ; 70 else if(H_cnt >= (H_total_time-1)) 71 H_cnt <= 'd0 ; 72 else 73 H_cnt <= H_cnt + 1'b1 ; 74 75 end 76 77 //V_cnt 78 always @ (posedge sclk or negedge s_rst_n) begin 79 if(s_rst_n == 1'b0) 80 V_cnt <= 'd0 ; 81 else if (V_cnt >= (V_total_time-1) && V_cnt >= (H_total_time-1)) 82 V_cnt <= 'd0 ; 83 else if(V_cnt == H_total_time-1) 84 V_cnt <= V_cnt + 1'b1 ; 85 86 end 87 88 //rd_data_reg 89 always @ (posedge sclk or negedge s_rst_n) begin 90 if(s_rst_n == 1'b0) 91 rd_data_reg <= 64'h0 ; 92 else if(vga_rd_en == 1'b1) 93 rd_data_reg <= vga_rd_data ; 94 95 end 96 97 98 99 //rd_cnt_add 100 always @ (posedge sclk or negedge s_rst_n) begin 101 if(s_rst_n == 1'b0) 102 rd_cnt_add <= 1'b0 ; 103 else if(H_cnt >= 140 & H_cnt <= 780) 104 rd_cnt_add <= 1'b1 ; 105 else 106 rd_cnt_add <= 1'b0 ; 107 end 108 109 //rd_cnt 110 always @ (posedge sclk or negedge s_rst_n) begin 111 if(s_rst_n == 1'b0) 112 rd_cnt <= 'd0 ; 113 else if(rd_cnt_add == 1'b1) 114 rd_cnt <= rd_cnt + 1'b1 ; 115 else if(rd_cnt == 3) 116 rd_cnt <= 'd0 ; 117 118 end 119 120 //byte_cnt 121 always @ (posedge sclk or negedge s_rst_n) begin 122 if(s_rst_n == 1'b0) 123 byte_cnt <= 'd0; 124 else if(rd_cnt_add_r2 == 1'b1 ) 125 byte_cnt <= byte_cnt + 1'b1 ; 126 127 end 128 129 //rd_cnt_add_r2 130 always @(posedge sclk)begin 131 rd_cnt_add <= rd_cnt ; 132 rd_cnt_add_r2 <= rd_cnt_add ; 133 end 134 135 136 //vga_rd_req 137 always @ (posedge sclk or negedge s_rst_n) begin 138 if(s_rst_n == 1'b0) 139 vga_rd_req <= 1'b0 ; 140 else if(V_cnt == 35 && H_cnt == 0) 141 vga_rd_req <= 1'b1 ; 142 143 end 144 145 146 //vga_rd_en 147 always @ (posedge sclk or negedge s_rst_n) begin 148 if(s_rst_n == 1'b0) 149 vga_rd_en <= 1'b0 ; 150 else if(rd_cnt_add == 1'b1 && rd_cnt == 0) 151 vga_rd_en <= 1'b1 ; 152 else 153 vga_rd_en <= 1'b0 ; 154 end 155 156 //拆分数据 vga_data 157 always @ (posedge sclk or negedge s_rst_n) begin 158 if(s_rst_n == 1'b0) 159 vga_data <= 'd0 ; 160 else if(rd_cnt_add_r2 == 1'b1) 161 case (byte_cnt) 162 0: vga_data <= rd_data_reg[63:48]; 163 1: vga_data <= rd_data_reg[47:32]; 164 2: vga_data <= rd_data_reg[31:16]; 165 3: vga_data <= rd_data_reg[15: 0]; 166 167 endcase 168 else 169 vga_data <= 'd0 ; 170 end 171 172 endmodule

1 // ********************************************************************************* 2 // Project Name : 3 // Weixin : li15226499835 4 // Website : https://www.cnblogs.com/lgy-gdeu/ 5 // Create Time : 201// 6 // File Name : .v 7 // Module Name : 8 // Abstract : 9 // editor : sublime text 3 10 // ********************************************************************************* 11 // Modification History: 12 // Date By Version Change Description 13 // ----------------------------------------------------------------------- 14 // 201// 李国勇 1.0 Original 15 // 16 // ********************************************************************************* 17 18 `timescale 1ns/1ps 19 module usb_read( 20 21 // system signals 22 input s_rst_n , 23 // system signals 24 input usb_ifclk , 25 input usb_full , 26 input usb_empty , 27 output wire usb_slcs , 28 output wire usb_slwr , 29 output wire usb_slrd , 30 output wire usb_sloe , 31 output wire [ 1:0] usb_fifoadr , 32 input [15:0] usb_fdata , 33 // User Data 34 output reg usb_wr_en , 35 output reg [63:0] usb_wr_data 36 ); 37 38 //========================================================================\ 39 // =========== Define Parameter and Internal signals =========== 40 //========================================================================/ 41 42 reg usb_slrd_reg ; 43 reg [ 1:0] data_cnt ; 44 45 46 //============================================================================= 47 //************** Main Code ************** 48 //============================================================================= 49 assign usb_slcs = 1'b0; 50 assign usb_slrd = (usb_empty == 1'b1 && usb_slrd_reg == 1'b0) ? 1'b0 : 1'b1; 51 assign usb_slwr = 1'b1; 52 assign usb_sloe = 1'b0; 53 assign usb_fifoadr = 2'b00; // 2,4,6,8 54 55 56 always @(posedge usb_ifclk or negedge s_rst_n) begin 57 if(s_rst_n == 1'b0) 58 usb_slrd_reg <= 1'b1; 59 else if(usb_empty == 1'b1) 60 usb_slrd_reg <= 1'b0; 61 else 62 usb_slrd_reg <= 1'b1; 63 end 64 65 always @(posedge usb_ifclk or negedge s_rst_n) begin 66 if(s_rst_n == 1'b0) 67 usb_wr_data <= 64'h0; 68 else if(usb_slrd == 1'b0) 69 usb_wr_data <= {usb_wr_data[47:0], usb_fdata[7:0],usb_fdata[15:8]}; 70 end 71 72 always @(posedge usb_ifclk or negedge s_rst_n) begin 73 if(s_rst_n == 1'b0) 74 data_cnt <= 'd0; 75 else if(usb_slrd == 1'b0) 76 data_cnt <= data_cnt + 1'b1; 77 end 78 79 always @(posedge usb_ifclk or negedge s_rst_n) begin 80 if(s_rst_n == 1'b0) 81 usb_wr_en <= 1'b0; 82 else if(usb_slrd == 1'b0 && data_cnt == 'd3) 83 usb_wr_en <= 1'b1; 84 else 85 usb_wr_en <= 1'b0; 86 end 87 88 endmodule

1 // ********************************************************************************* 2 // Project Name : 3 // Weixin : li15226499835 4 // Website : https://www.cnblogs.com/lgy-gdeu/ 5 // Create Time : 201// 6 // File Name : .v 7 // Module Name : 8 // Abstract : 9 // editor : sublime text 3 10 // ********************************************************************************* 11 // Modification History: 12 // Date By Version Change Description 13 // ----------------------------------------------------------------------- 14 // 201// æŽå›½å‹ 1.0 Original 15 // 16 // ********************************************************************************* 17 `timescale 1ns/1ps 18 module ddr_drive( 19 20 // system signals 21 input wr_clk , 22 input rd_clk , 23 input s_rst_n , 24 // DDR3 User Interfaces 25 input p0_wr_en , 26 output reg p0_cmd_en , 27 output wire [ 2:0] p0_cmd_instr , 28 output wire [ 5:0] p0_cmd_bl , 29 output reg [29:0] p0_byte_addr , 30 output wire [ 7:0] p0_wr_mask , 31 output reg p1_cmd_en , 32 output wire [ 2:0] p1_cmd_instr , 33 output wire [ 5:0] p1_cmd_bl , 34 output reg [29:0] p1_byte_addr , 35 36 37 //debug vga interfaces 38 //output reg p1_rd_en , 39 //input [63:0] p1_rd_data , 40 //vga port 41 input wire vga_rd_req , 42 input wire p1_rd_en // input wire vga_rd_en 43 ); 44 45 //========================================================================\ 46 // =========== Define Parameter and Internal signals =========== 47 //========================================================================/ 48 //localparam BURST_END = 'd10 ; 49 localparam BURST_END = 4800 ; 50 51 reg [ 3:0] wr_cnt ; 52 reg [15:0] wr_bl_cnt ; 53 54 reg [ 3:0] rd_cnt ;//读数æ®è®¡æ•°å™¨ 55 reg [15:0] rd_bl_cnt ;//读çªå‘次数计数器 56 //============================================================================= 57 //************** Main Code ************** 58 //============================================================================= 59 assign p0_cmd_instr = 3'b000; 60 assign p0_cmd_bl = 'd15; 61 assign p0_wr_mask = 8'h0; 62 assign p1_cmd_instr = 3'b001; 63 assign p1_cmd_bl = 'd15; 64 65 always @(posedge wr_clk or negedge s_rst_n) begin 66 if(s_rst_n == 1'b0) 67 wr_cnt <= 'd0; 68 else if(p0_wr_en == 1'b1) 69 wr_cnt <= wr_cnt + 1'b1; 70 end 71 72 always @(posedge wr_clk or negedge s_rst_n) begin 73 if(s_rst_n == 1'b0) 74 p0_cmd_en <= 1'b0; 75 else if(p0_wr_en == 1'b1 && wr_cnt == 'd15) 76 p0_cmd_en <= 1'b1; 77 else 78 p0_cmd_en <= 1'b0; 79 end 80 81 always @(posedge wr_clk or negedge s_rst_n) begin 82 if(s_rst_n == 1'b0) 83 p0_byte_addr <= 'd0; 84 else if(p0_cmd_en == 1'b1 && wr_bl_cnt >= (BURST_END-1)) 85 p0_byte_addr <= 'd0; 86 else if(p0_cmd_en == 1'b1) 87 p0_byte_addr <= p0_byte_addr + 'd128; 88 end 89 90 always @(posedge wr_clk or negedge s_rst_n) begin 91 if(s_rst_n == 1'b0) 92 wr_bl_cnt <= 'd0; 93 else if(p0_cmd_en == 1'b1 && wr_bl_cnt >= (BURST_END-1)) 94 wr_bl_cnt <= 'd0; 95 else if(p0_cmd_en == 1'b1) 96 wr_bl_cnt <= wr_bl_cnt + 1'b1; 97 end 98 99 100 101 //============================================================================= 102 //*************************VGA debug with ddr ip************************** 103 //============================================================================= 104 105 //p1_cmd_en 106 always @ (posedge rd_clk or negedge s_rst_n) begin 107 if(s_rst_n == 1'b0) 108 p1_cmd_en <= 1'b0 ; 109 else if (vga_rd_req == 1'b1 ) 110 p1_cmd_en <= 1'b1 ;//äº§ç”Ÿç¬¬ä¸€ä¸ªå‘½ä»¤ä½¿èƒ 111 else if(p1_rd_en ==1'b1 && rd_cnt == 0 && rd_bl_cnt <= (BURST_END-1)) 112 p1_cmd_en <= 1'b1 ; 113 else 114 p1_cmd_en <= 1'b0 ; 115 116 end 117 118 //rd_cnt 119 always @ (posedge rd_clk or negedge s_rst_n) begin 120 if(s_rst_n == 1'b0) 121 rd_cnt <= 'd0 ; 122 else if(p1_rd_en == 1'b1 ) 123 rd_cnt <= rd_cnt + 1'b1 ; 124 125 end 126 127 //p1_byte_addr 128 always @ (posedge rd_clk or negedge s_rst_n) begin 129 if(s_rst_n == 1'b0) 130 p1_byte_addr <= 'd0 ; 131 else if(vga_rd_req == 1'b1 ) 132 p1_byte_addr <= 'd0 ; 133 else if(p1_cmd_en == 1'b1 ) 134 p1_byte_addr <=p1_byte_addr + 'd128 ; 135 136 end 137 138 //rd_bl_cnt 139 always @ (posedge rd_clk or negedge s_rst_n) begin 140 if(s_rst_n == 1'b0) 141 rd_bl_cnt <= 'd0 ; 142 else if(vga_rd_req == 1'b1 ) 143 rd_bl_cnt <= 'd0 ; 144 else if(p1_cmd_en == 1'b1 ) 145 rd_bl_cnt <= rd_bl_cnt + 1'b1 ; 146 147 end 148 149 150 151 endmodule

1 // ********************************************************************************* 2 // Project Name : 3 // Weixin : li15226499835 4 // Website : https://www.cnblogs.com/lgy-gdeu/ 5 // Create Time : 2019 6 // File Name : .v 7 // Module Name : 8 // Abstract : 9 // editor : sublime text 3 10 // ********************************************************************************* 11 // Modification History: 12 // Date By Version Change Description 13 // ----------------------------------------------------------------------- 14 // 2019 李国勇 1.0 Original 15 // 16 // ********************************************************************************* 17 `timescale 1ns/1ps 18 19 module ddr_top( 20 21 22 23 // system signals 24 input c3_sys_clk , 25 input sclk ,//50Mhz 26 input c3_sys_rst_i , 27 // DDR3 Interfaces 28 inout [15:0] mcb3_dram_dq , 29 output wire [12:0] mcb3_dram_a , 30 output wire [2:0] mcb3_dram_ba , 31 output wire mcb3_dram_ras_n , 32 output wire mcb3_dram_cas_n , 33 output wire mcb3_dram_we_n , 34 output wire mcb3_dram_odt , 35 output wire mcb3_dram_reset_n , 36 output wire mcb3_dram_cke , 37 output wire mcb3_dram_ck , 38 output wire mcb3_dram_ck_n , 39 output wire mcb3_dram_dm , 40 inout mcb3_dram_udqs , 41 inout mcb3_dram_udqs_n , 42 inout mcb3_dram_dqs , 43 inout mcb3_dram_dqs_n , 44 inout mcb3_rzq , 45 inout mcb3_zio , 46 output mcb3_dram_udm , 47 // USB interfaces 48 input usb_ifclk , 49 input usb_full , 50 input usb_empty , 51 output wire usb_slcs , 52 output wire usb_slwr , 53 output wire usb_slrd , 54 output wire usb_sloe , 55 output wire [ 1:0] usb_fifoadr , 56 input [15:0] usb_fdata , 57 //VGA interfaces 58 output wire vga_hs , 59 output wire vga_vs , 60 output wire [4:0] vga_r , 61 output wire [5:0] vga_g , 62 output wire [4:0] vga_b 63 // output wire vga_clk ,//it use for which vga_asic drive 64 // output wire vga_blank ;//it use for which vga_asic drive 65 // output wire [15:0] vga_data 66 ); 67 68 69 70 //========================================================================\ 71 // =========== Define Parameter and Internal signals =========== 72 //========================================================================/ 73 wire p0_cmd_en ; 74 wire [ 2:0] p0_cmd_instr ; 75 wire [ 5:0] p0_cmd_bl ; 76 wire [29:0] p0_byte_addr ; 77 wire p0_wr_en ; 78 wire [ 7:0] p0_wr_mask ; 79 wire [63:0] p0_wr_data ; 80 wire p1_cmd_en ; 81 wire [ 2:0] p1_cmd_instr ; 82 wire [ 5:0] p1_cmd_bl ; 83 wire [29:0] p1_byte_addr ; 84 wire p1_rd_en ; 85 wire [63:0] p1_rd_data ; 86 87 wire vga_rd_req ; 88 wire clk_sys25m ; 89 wire pll_locked ; 90 wire [15:0] vga_data ; 91 //============================================================================= 92 //************** Main Code ************** 93 //============================================================================= 94 //assign vga_clk = clk_sys25m ;//it use for which vga_asic drive 95 //assign vga_blank = 1'b1 ;//it use for which vga_asic drive 96 assign {vga_r,vga_g,vga_b} = vga_data ; 97 usb_read usb_read_inst( 98 // system signals 99 .s_rst_n (c3_sys_rst_i & c3_calib_done ), 100 // system signals 101 .usb_ifclk (usb_ifclk ), 102 .usb_full (usb_full ), 103 .usb_empty (usb_empty ), 104 .usb_slcs (usb_slcs ), 105 .usb_slwr (usb_slwr ), 106 .usb_slrd (usb_slrd ), 107 .usb_sloe (usb_sloe ), 108 .usb_fifoadr (usb_fifoadr ), 109 .usb_fdata (usb_fdata ), 110 // User Data 111 .usb_wr_en (p0_wr_en ), 112 .usb_wr_data (p0_wr_data ) 113 ); 114 115 ddr_drive ddr_drive_inst( 116 // system signals 117 .rd_clk (clk_sys25m ), 118 .wr_clk (usb_ifclk ), 119 .s_rst_n (c3_sys_rst_i ), 120 // DDR3 User Interfaces 121 .p0_cmd_en (p0_cmd_en ), 122 .p0_cmd_instr (p0_cmd_instr ), 123 .p0_cmd_bl (p0_cmd_bl ), 124 .p0_byte_addr (p0_byte_addr ), 125 .p0_wr_en (p0_wr_en ), 126 .p0_wr_mask (p0_wr_mask ), 127 .p1_cmd_en (p1_cmd_en ), 128 .p1_cmd_instr (p1_cmd_instr ), 129 .p1_cmd_bl (p1_cmd_bl ), 130 .p1_byte_addr (p1_byte_addr ), 131 .p1_rd_en (p1_rd_en ), 132 //VGA interfaces 133 134 .vga_rd_req (vga_rd_req ) 135 ); 136 137 mig_39_2 # ( 138 .C3_P0_MASK_SIZE (8 ), 139 .C3_P0_DATA_PORT_SIZE (64 ), 140 .C3_P1_MASK_SIZE (8 ), 141 .C3_P1_DATA_PORT_SIZE (64 ), 142 .DEBUG_EN (0 ), 143 .C3_MEMCLK_PERIOD (3200 ), 144 .C3_CALIB_SOFT_IP ("TRUE" ), 145 .C3_SIMULATION ("TRUE" ), 146 .C3_RST_ACT_LOW (1 ), 147 .C3_INPUT_CLK_TYPE ("SINGLE_ENDED" ), 148 .C3_MEM_ADDR_ORDER ("BANK_ROW_COLUMN" ), 149 .C3_NUM_DQ_PINS (16 ), 150 .C3_MEM_ADDR_WIDTH (13 ), 151 .C3_MEM_BANKADDR_WIDTH (3 ) 152 ) u_mig_39_2 ( 153 154 .c3_sys_clk (c3_sys_clk ), // input 155 .c3_sys_rst_i (c3_sys_rst_i ), // input 156 157 .mcb3_dram_dq (mcb3_dram_dq ), 158 .mcb3_dram_a (mcb3_dram_a ), 159 .mcb3_dram_ba (mcb3_dram_ba ), 160 .mcb3_dram_ras_n (mcb3_dram_ras_n ), 161 .mcb3_dram_cas_n (mcb3_dram_cas_n ), 162 .mcb3_dram_we_n (mcb3_dram_we_n ), 163 .mcb3_dram_odt (mcb3_dram_odt ), 164 .mcb3_dram_cke (mcb3_dram_cke ), 165 .mcb3_dram_ck (mcb3_dram_ck ), 166 .mcb3_dram_ck_n (mcb3_dram_ck_n ), 167 .mcb3_dram_dqs (mcb3_dram_dqs ), 168 .mcb3_dram_dqs_n (mcb3_dram_dqs_n ), 169 .mcb3_dram_udqs (mcb3_dram_udqs ), // for X16 parts 170 .mcb3_dram_udqs_n (mcb3_dram_udqs_n ), // for X16 parts 171 .mcb3_dram_udm (mcb3_dram_udm ), // for X16 parts 172 .mcb3_dram_dm (mcb3_dram_dm ), 173 .mcb3_dram_reset_n (mcb3_dram_reset_n ), 174 .c3_clk0 (c3_clk0 ), // output 175 .c3_rst0 (c3_rst0 ), // output 176 177 178 179 .c3_calib_done (c3_calib_done ), 180 .mcb3_rzq (mcb3_rzq ), 181 182 .mcb3_zio (mcb3_zio ), 183 184 // Command Path 185 .c3_p0_cmd_clk (usb_ifclk ), 186 .c3_p0_cmd_en (p0_cmd_en ), 187 .c3_p0_cmd_instr (p0_cmd_instr ), 188 .c3_p0_cmd_bl (p0_cmd_bl ), 189 .c3_p0_cmd_byte_addr (p0_byte_addr ), 190 .c3_p0_cmd_empty ( ), 191 .c3_p0_cmd_full ( ), 192 // Write Data path 193 .c3_p0_wr_clk (usb_ifclk ), 194 .c3_p0_wr_en (p0_wr_en ), 195 .c3_p0_wr_mask (p0_wr_mask ), 196 .c3_p0_wr_data (p0_wr_data ), 197 .c3_p0_wr_full ( ), 198 .c3_p0_wr_empty ( ), 199 .c3_p0_wr_count ( ), 200 .c3_p0_wr_underrun ( ), 201 .c3_p0_wr_error ( ), 202 203 .c3_p0_rd_clk (0 ), 204 .c3_p0_rd_en (0 ), 205 .c3_p0_rd_data ( ), 206 .c3_p0_rd_full ( ), 207 .c3_p0_rd_empty ( ), 208 .c3_p0_rd_count ( ), 209 .c3_p0_rd_overflow ( ), 210 .c3_p0_rd_error ( ), 211 .c3_p1_cmd_clk (clk_sys25m ), 212 .c3_p1_cmd_en (p1_cmd_en ), 213 .c3_p1_cmd_instr (p1_cmd_instr ), 214 .c3_p1_cmd_bl (p1_cmd_bl ), 215 .c3_p1_cmd_byte_addr (p1_byte_addr ), 216 .c3_p1_cmd_empty ( ), 217 .c3_p1_cmd_full ( ), 218 .c3_p1_wr_clk (0 ), 219 .c3_p1_wr_en (0 ), 220 .c3_p1_wr_mask (0 ), 221 .c3_p1_wr_data (64'h0 ), 222 .c3_p1_wr_full ( ), 223 .c3_p1_wr_empty ( ), 224 .c3_p1_wr_count ( ), 225 .c3_p1_wr_underrun ( ), 226 .c3_p1_wr_error ( ), 227 .c3_p1_rd_clk (clk_sys25m ), 228 .c3_p1_rd_en (p1_rd_en ), 229 .c3_p1_rd_data (p1_rd_data ), 230 .c3_p1_rd_full ( ), 231 .c3_p1_rd_empty ( ), 232 .c3_p1_rd_count ( ), 233 .c3_p1_rd_overflow ( ), 234 .c3_p1_rd_error ( ) 235 ); 236 237 vga_drive vga_drive_inst( 238 //system signals 239 .sclk (clk_sys25m ), 240 .s_rst_n (pll_locked & c3_calib_done ), 241 //vga signals 242 .vga_hs (vga_hs ), 243 .vga_vs (vga_vs ), 244 .vga_data (vga_data ), 245 //vga ctrl signals 246 .vga_rd_req (vga_rd_req ), 247 .vga_rd_en (p1_rd_en ), 248 .vga_rd_data (p1_rd_data ) 249 250 ); 251 252 clk_wiz_v3_6 clk_wiz_v3_6_inst( 253 // Clock in ports 254 .CLK_IN1 (sclk ), // IN 255 // Clock out ports 256 .CLK_OUT1 (clk_sys25m), // OUT 257 // Status and control signals 258 .RESET (1'b0 ), // IN 259 .LOCKED (pll_locked)) ; // OUT 260 261 endmodule