参见我的工程E:\vivado_program\ps_control_pl_ddr3

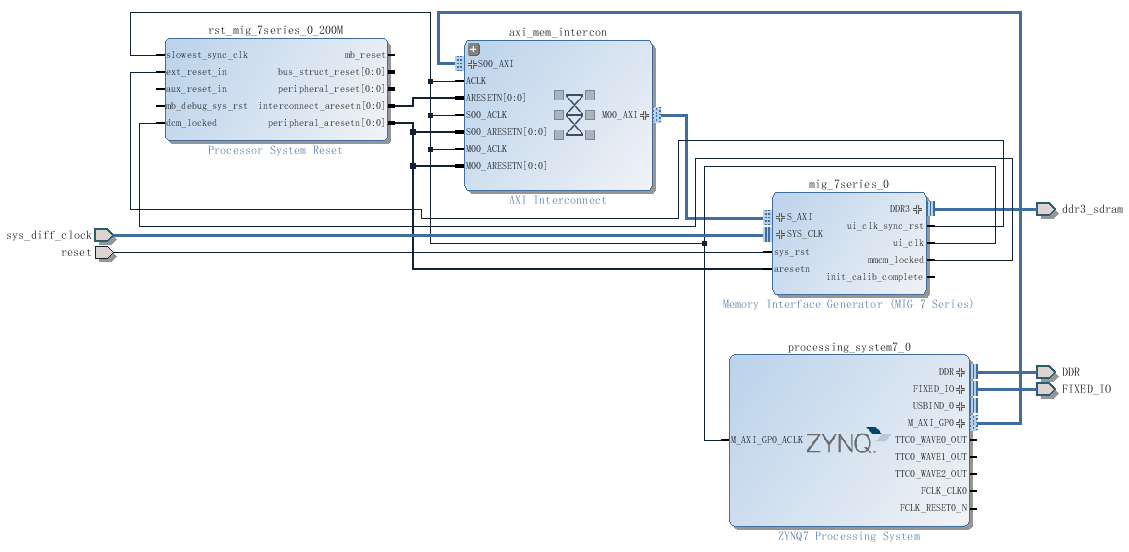

该例程是在ZC706开发板上实现的,在vivado中如下所示:

其中mig的配置比较复杂,具体参考文档在如下下载页中下载:

https://download.csdn.net/download/yanxiaopan/10467417

及xilinx官方文档ug898第五章。

在SDK中的程序如下所示:

#include <stdio.h>

#include "platform.h"

#include "xil_io.h"

#include "xparameters.h"

//void print(char *str);

int main()

{

init_platform();

//print("Hello World\n\r");

int num;

int result;

xil_printf("..........the test is start.........\n\r");

for(num=0;num<15;num++)

{

Xil_Out32(XPAR_MIG_7SERIES_0_BASEADDR+num*4,0x10000000+num);

}

for(num=0;num<15;num++)

{

result=Xil_In32(XPAR_MIG_7SERIES_0_BASEADDR+num*4);

xil_printf("the data at %x is %x \n\r",XPAR_MIG_7SERIES_0_BASEADDR+num*4,result);

}

xil_printf("..........the test is end.........\n\r");

cleanup_platform();

return 0;

}另外直接添加SDK中的模板程序memorytest,也测试成功。

一.各个时钟之间的关系

Input Clock Period是晶振时钟,一般设置为200MHZ

Clock period是主时钟,是自己设置的,一般可设置为400MHZ或800MHZ,DDR3按照这个时钟往DDR3中读写数据,上下沿都写数据。

PHYto Controller Clock Ratio 是用户时钟和主时钟的比例,可以设置为2:1或4:1,这里设置为4:1,当把主时钟设置成800MHZ时,则用户时钟为200MHZ,假设DDR3的数据位宽为64bits,则用户的数据位宽为64*4*2=512bits在这里设置的晶振时钟是200MHZ,然后经过4倍频变成800MH作为DDR3读写数据的主时钟,然后主时钟再经过四分频变成200MHZ作为用户时钟

这里的System Clock是指的主时钟????应该是晶振时钟吧????

当晶振时钟选择为200MHZ时,Reference Clock可以选择use System Clock