这里只是自己做个笔记,方便以后查看。会持续更新,只是部分相关只是更新。

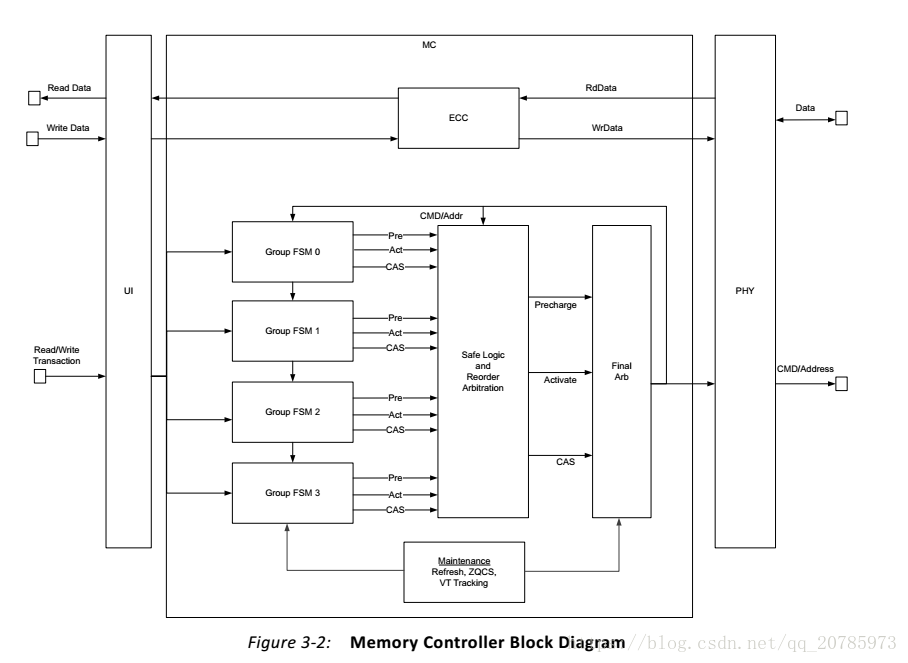

Group Machines

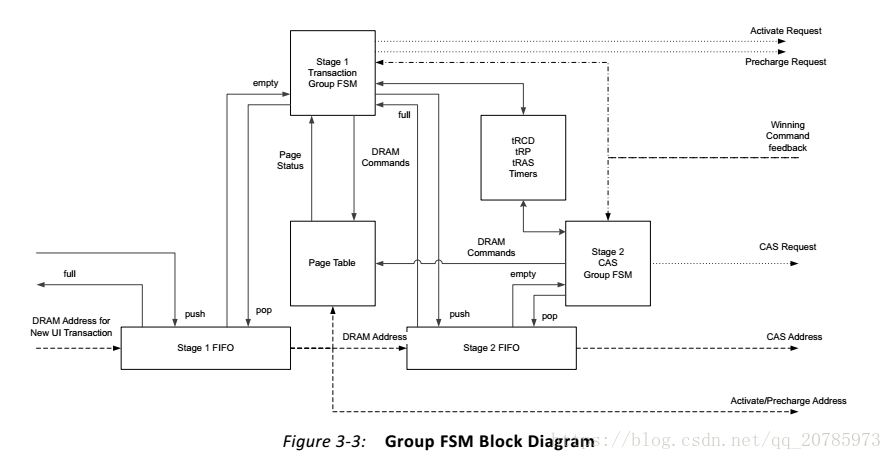

图3-3显示了一个实例的Group FSM框图。 主要有两个组FSM块,阶段1和阶段2的部分,每个部分包含FIFO和FSM。 阶段1与UI接口,发出预充电和激活命令,并跟踪DRAM页面状态。 阶段2发出CAS命令并管理RMW流。 FSM用于在最早的安全时间安排DRAM命令的每个等级和库也有一组DRAM定时器。 组FSM块被设计成使得每个实例从UI排队多个事务,将来自多个事务的DRAM命令交织到DDR总线上以提高效率,并严格按顺序执行CAS命令。

当从UI接受新事务时,它被推入阶段1事务FIFO。 检查阶段1 FIFO头部的事务的页面状态并将其提供给阶段1事务FSM。 FSM决定是否需要发出Precharge或Activate命令,以及何时根据DRAM定时器发出它们是安全的。 当页面打开且由于阶段2 FIFO中的待处理RDA或WRA而尚未安排关闭时,事务将从阶段1 FIFO传输到阶段2 FIFO。 此时,弹出阶段1 FIFO,阶段1 FSM开始处理下一个事务。 并行地,阶段2 FSM在阶段2 FIFO的头部处理事务的CAS命令阶段。 第2阶段FSM在基于tRCD定时器安全时发出CAS命令请求。 第2阶段FSM还发出RMW事务的读写CAS请求。

ECC

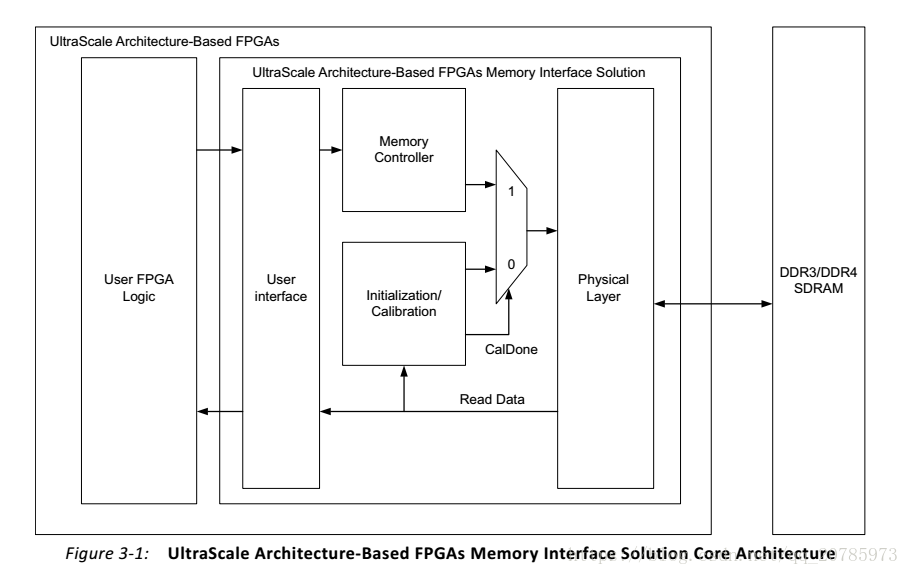

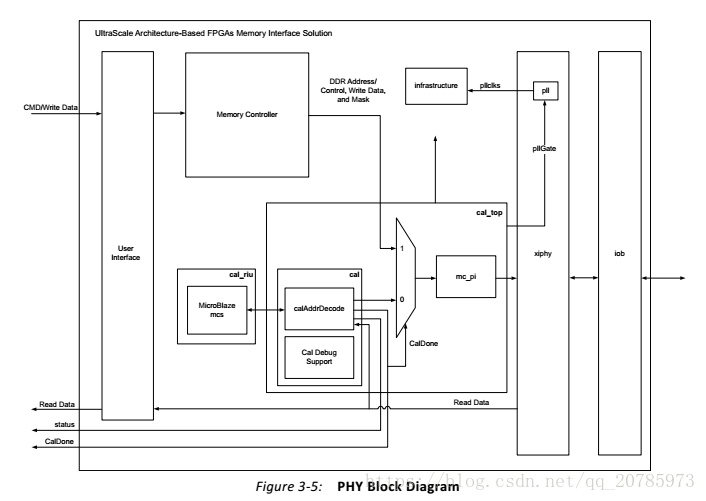

PHY

PHY被认为是外部DDR3或DDR4 SDRAM器件的低级物理接口,以及用于确保物理接口本身可靠运行的所有校准逻辑。 PHY生成与存储器设备接口所需的信号定时和排序。