Altera DDR3 IP Core的调用方法

FPGA

本篇文章介绍一下如何使用Quartusii13 来生成DDR3 IP核的例化模板。

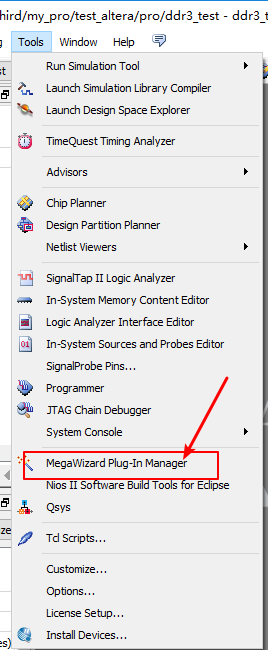

1.点击生成IP核

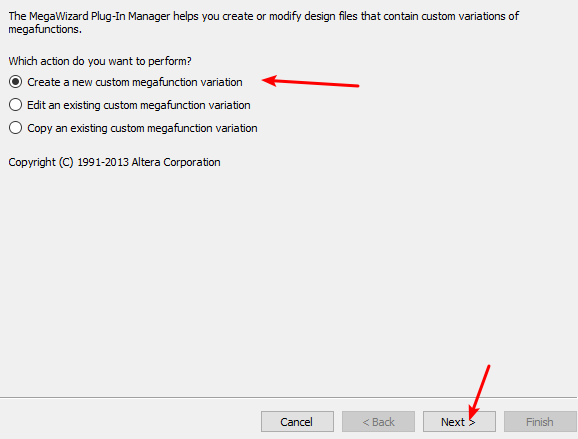

2.选择创建IP核,然后点击next

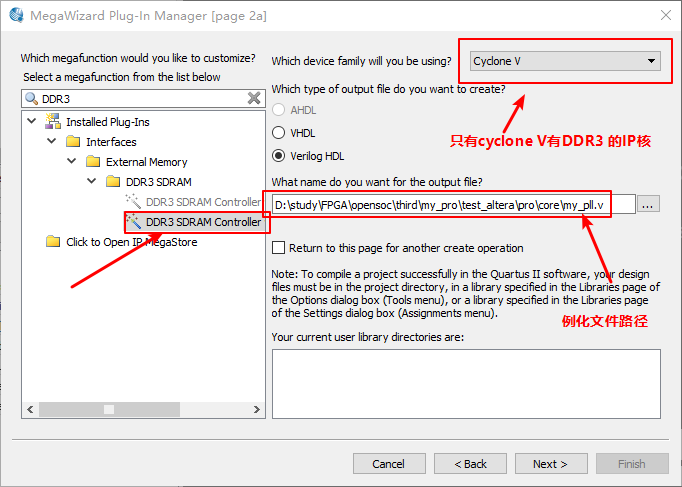

3.选择DDR3 IP核

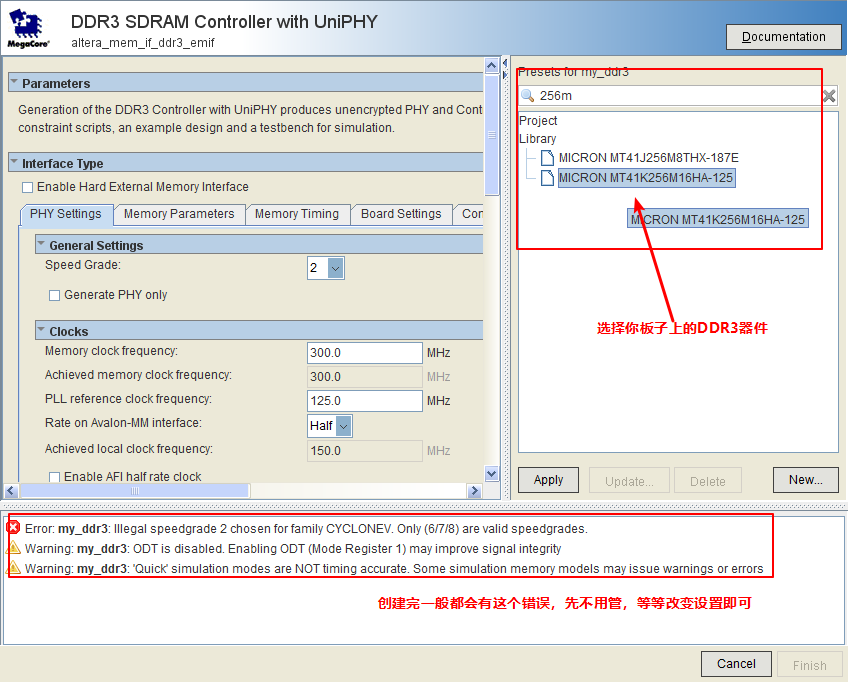

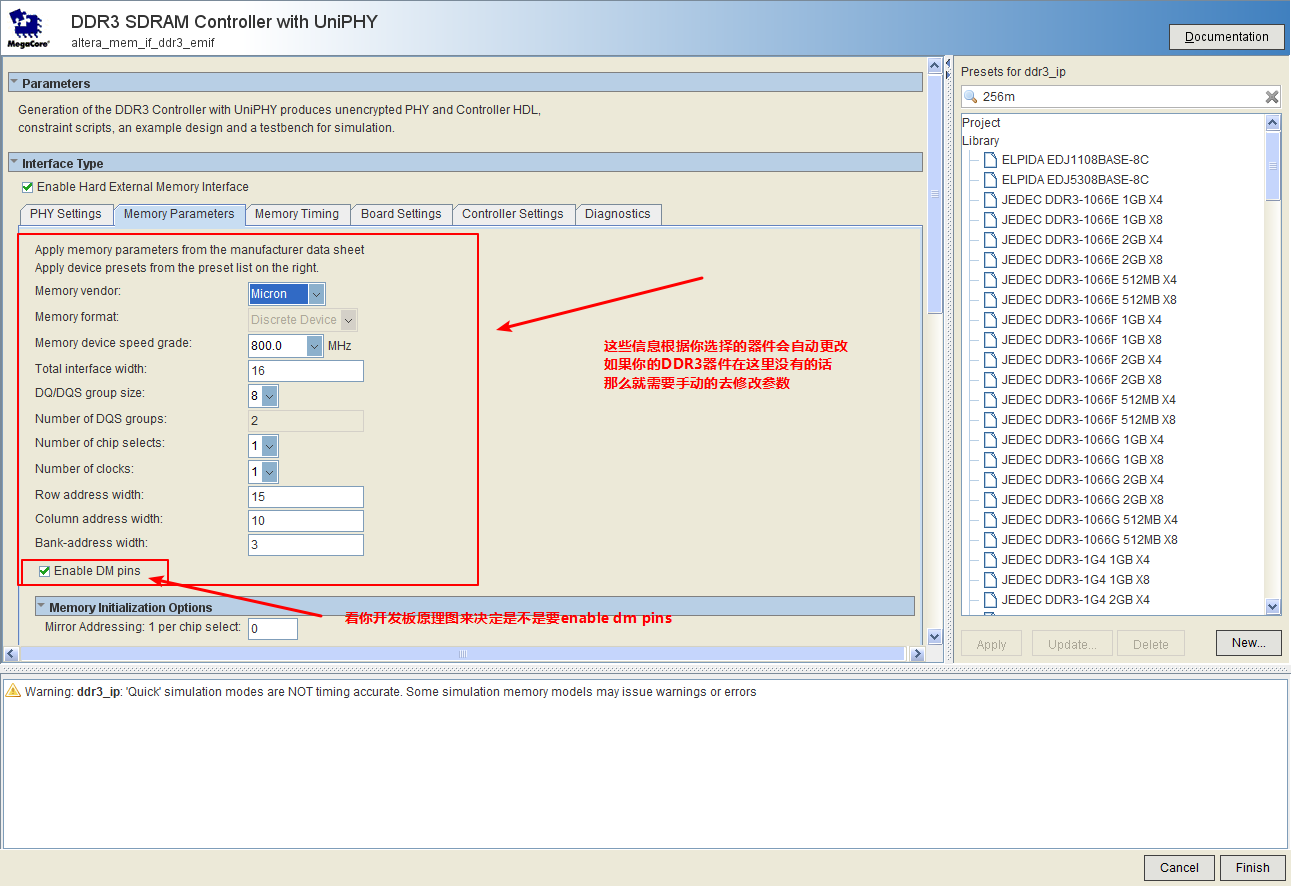

4.选择你开发板上DDR3的器件,然后点击Apply

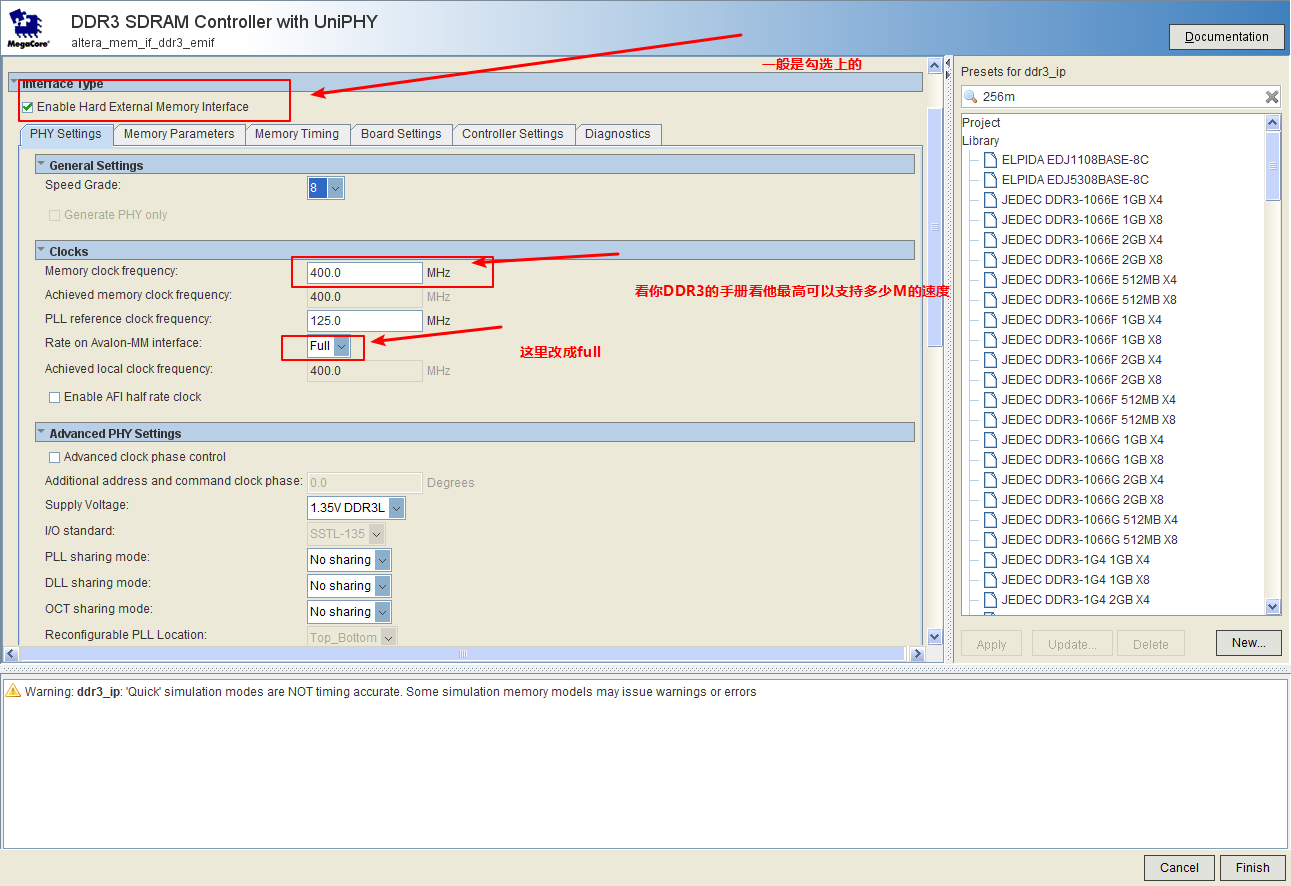

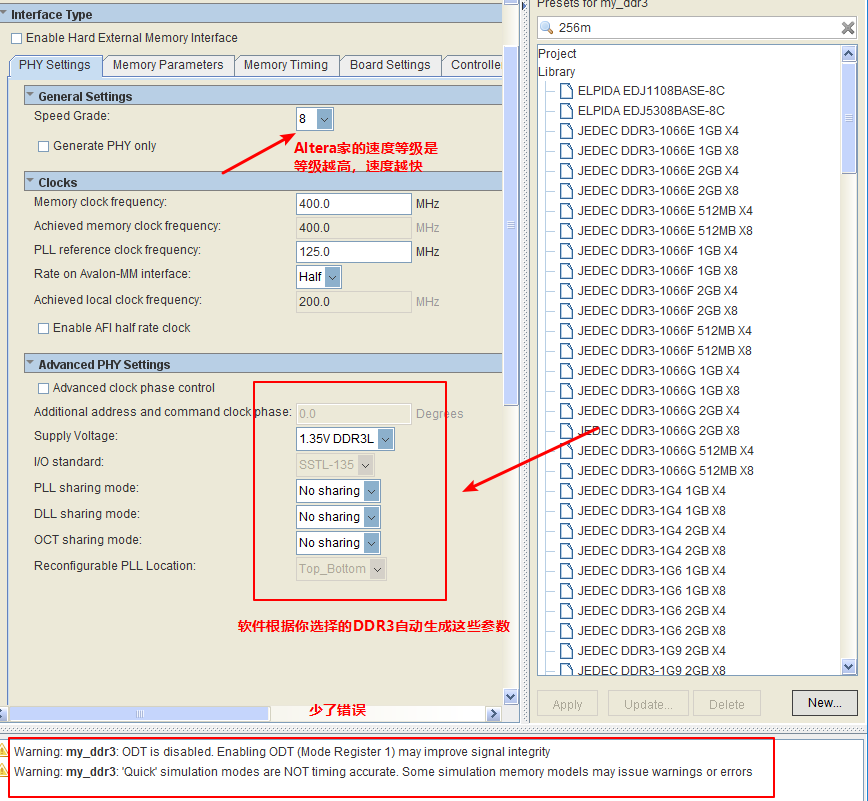

5.设置ddr3 phy setting

memory clock frequency 这个是你DDR3可以跑的速度

pll reference clock frequency这个是看你给DDR3这个器件提供多少M的时钟频率来确定这个数值。

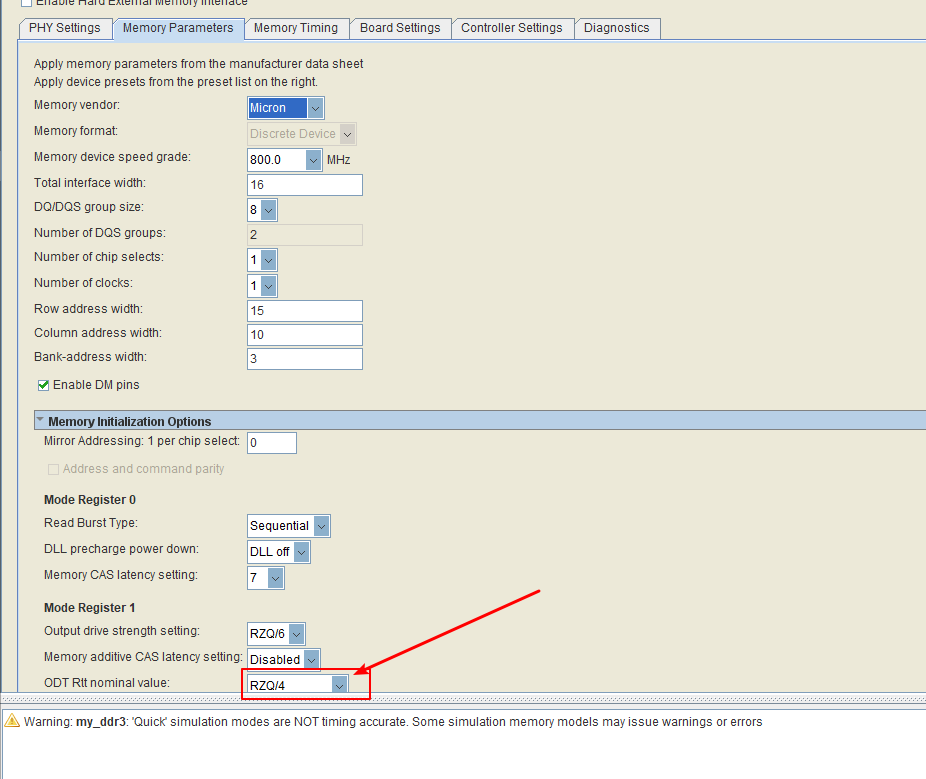

6.选择memory paramters

因为警告有说需要使能ODT,所以这里ODT选择RZQ/4

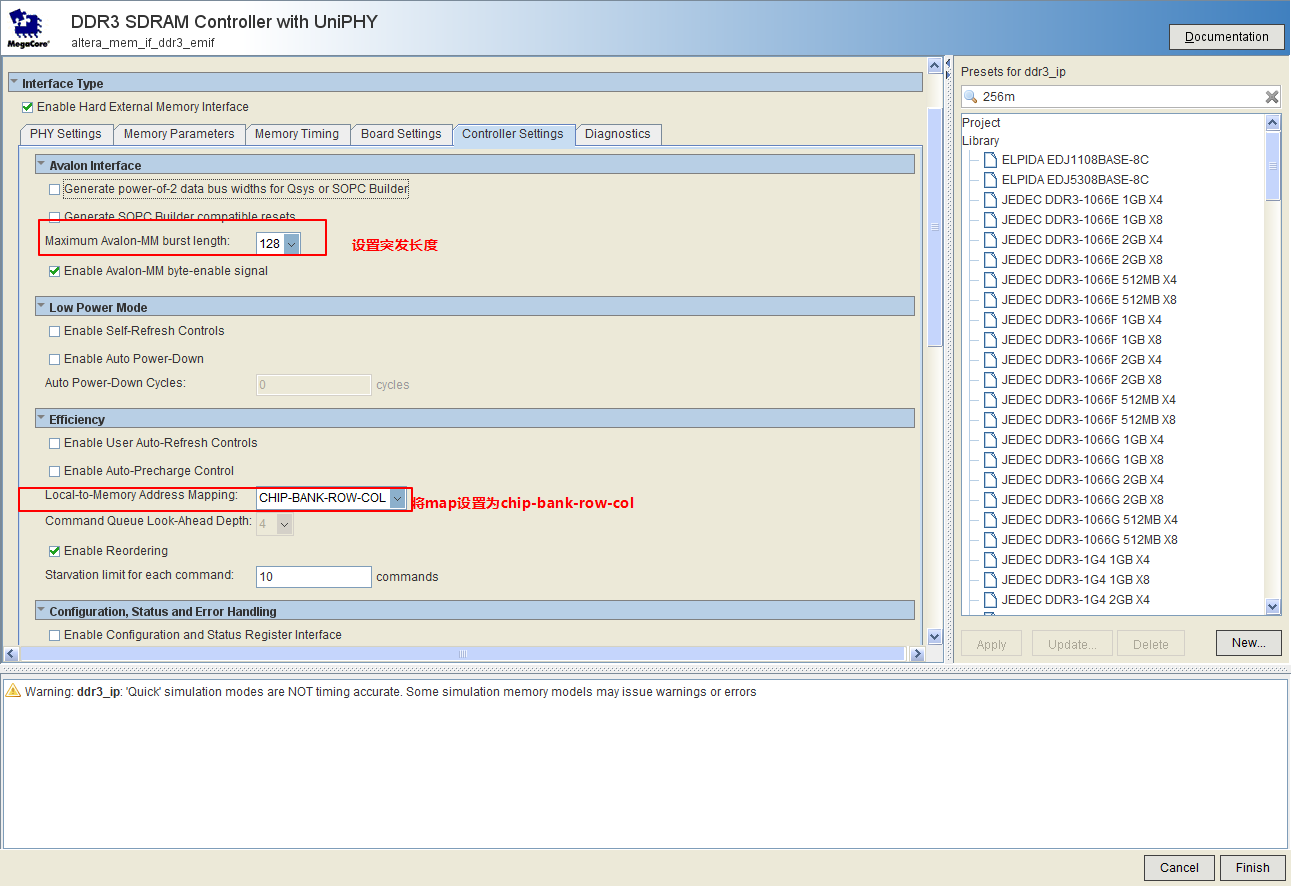

7.配置controller Setting

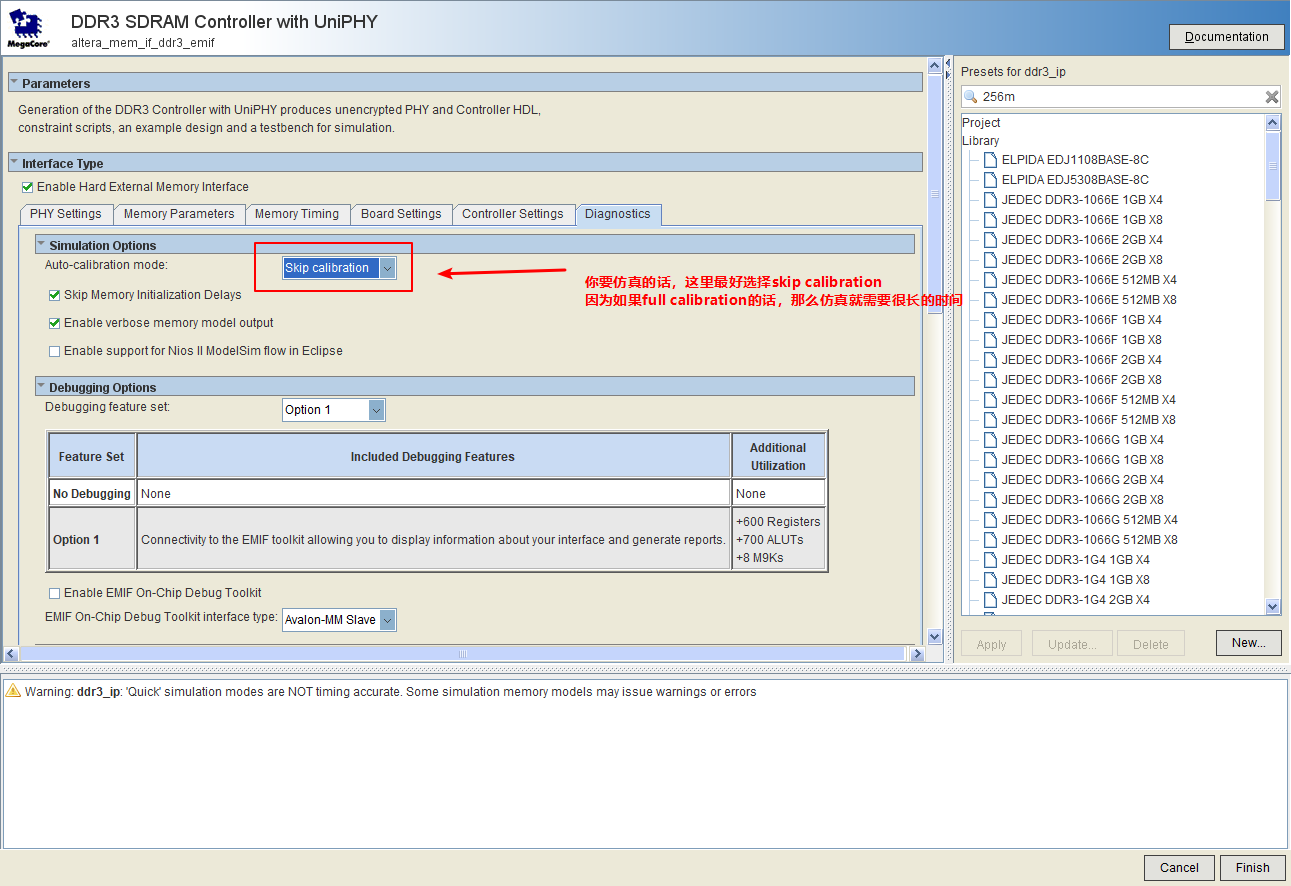

8.配置diagnostics,这里后面要测试的话,还是不要去选择full calibration ,一般都是选择skip calibration

配置完上面的内容是无错误,无警告的。配置完后,点击finish生成DDR3 IP核。

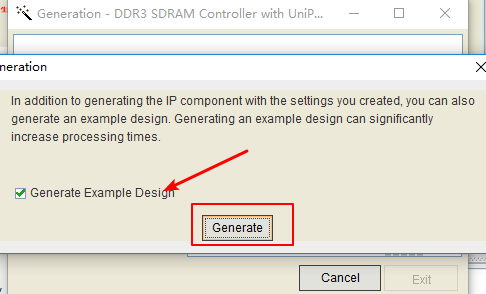

生成的时候要先点击generate这个选项。

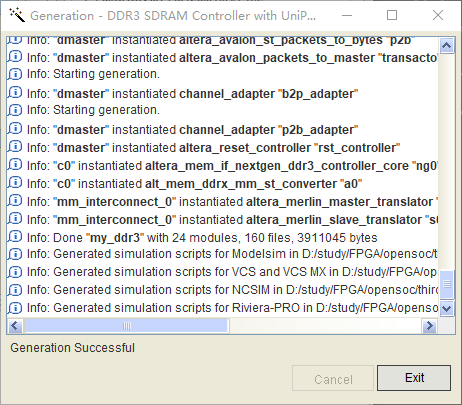

生成IP核后的信息

DDR3的IP核生成成功。