前言:

【相关教材《数字设计原理与实践(第四版)》】

这门课是笔者最害怕的一门课。作业不会写,实验不会做,上课浑浑噩噩......之所以造成这样的结果,或许是因为最初就没有好好跟着老师上课,且课下又不肯花时间学习的原因,所以一拖再拖,便导致了这种不堪设想的后果。但好在,一切都有补救的机会,“悟已往之不谏,知来者之可追。”

就在这种愧疚而自责的心情中,开启数电的"预习"之路吧...

第三章习题详解:

(笔者最终目标当然是考试啦,所以最快的入手方法就是从习题入手,一步一步地逆向回溯知识点,进而巩固记忆,熟练实战技巧。另:以下的解析仅仅是笔者自己针对答案的一些思考,有的可能不正确,所以大家要批判性阅读,不要盲目轻信)

3.7 2输入CMOS与非门电路使用多少个晶体管,每个类型使用多少个?

解析:想要解答这道题,首先就要对CMOS基本逻辑门电路的晶体管结构有一定的了解。

NMOS晶体管用作下拉电路,连接地线,输入高电源时导通

PMOS晶体管用作上拉电路,连接电源,输入低电源时导通

最简单的是CMOS反相器,由一个NMOS晶体管和PMOS晶体管构成。

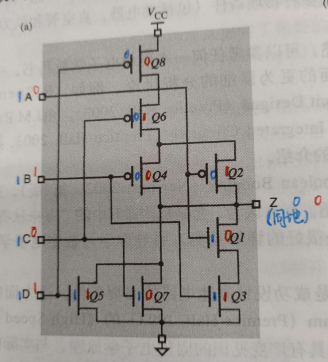

与非门:以CMOS反相器为基础,构成的CMOS与非门电路如下图所示。它由两个PMOS管和两个NMOS管构成,负载管PMOS管Q2与Q4并联,驱动管NMOS管Q1与Q3串联。

(本道题就解决了,还可以由此引申记忆或非门【上串下并】,与门,或门等)

3.10 给出“扇入”和“扇出”的定义,其中的哪一个是必须要计算的?

解析:定义略,扇出必须计算。(这个具体原因我问了一些同学,比较靠谱的解释是扇入上一个做器件的算扇出已经帮忙算好了......具体原因还待商榷)

这里要对扇入和扇出有一定的了解:

扇出:是指逻辑门电路在不超出其最坏情况负载规格的条件下,能够驱动输入端个数。

不仅依赖于输出端的特性,还依赖于所驱动的输入端的特性

必须考虑输出的两种可能:高电平状态和低电平状态。

扇出值=最大输出电流/最大输入电流。

总扇出:高态扇出和低态扇出中较小值。

3.11 下图所示电路是与或非门的一种类型,请画出该电路的功能表,并用与门,或门或反相器符号画出相应的逻辑原理图。

解析:这道题比较简单,只需要对PMOS晶体管和CMOS晶体管的基本功能有一定了解即可。

一共有4个输入端,所以共有16种情况。一个一个分析就好了。

下图中笔者用红蓝笔举了两个例子(0表示低电平和不导通,1相反)

3.20 使用表3-3中的数据表,确定74HC00在最坏条件下的最低和最高的直流噪声容限。要说明答案所需的所有假设。

解析:[这道题的难点在于要理解题目的含义,并且要能够在表中找到对应的信息。]

直流噪声容限:是一种对噪声程度的度量,表示多大的噪声会使最坏输出电压被破坏,成为不可被输入端识别的值。(单位为V)

计算方法一般是:V(ILmax)-V(OLmax)为低态直流噪声容;V(OHmin)-V(IHmin)为高态直流噪声容限

(这个记忆方法其实不是很难,在表中找四个数据即可:输入高电平的最小值,输入低电平的最大值,输出高电平的最小值,输出低电平的最大值)

本题解答:

最坏情况下,低态直流噪声容限:1.35-0.33=1.02V

高态直流噪声容限:3.84-3.15=0.69V

假设:低态:Vcc=Min IOL=4mA VIN=VIH 高态:Vcc=Min IOH=-4mA VIN=VIL

3.22、(?)在3.5节中定义了CMOS电路的7个不同电气参数。用3-3的数据表,确定74HC00的这些参数的最坏值。要说明答案所需的所有假设。

解析:该题首先要知道CMOS电路的7个不同的电气参数分别是什么。

输入高电平VIH和输入低电平VIL

输出高电平VOH和输出高电平VOL

直流噪声容限VNH和VNL

高电平输入电流和低电平输入电流

高电平输出电流和低电平输出电流

(以上是静态特征,找到了10个,其实7个就好了,电流只用算max)

本题解答:

VOHmin CMOS 负载:4.4V TTL 负载:3.84V 假设:Vcc=Min VIN=VIL IOH 为 max VIHmin 3.15V

VOLmax CMOS 负载:0.1V TTL 负载:0.33V 假设:Vcc=Min VIN=VIH IOL 为 max VILmax 1.35V

IOLmax CMOS 负载:20uA TTL 负载:4mA IOHmax CMOS 负载:-20uA TTL 负载:-4mA

IImax 1uA 假设:Vcc=Max VI=0(此时-1uA)或 Vcc(此时 1uA)

(注:这部分的解答有点迷,不太清楚怎么分辨CMOS和TTL,不清楚如何找假设条件)

3.31 何时与朋友握手是重要的?

解析:将 CMOS 器件交给别人时,尤其是在干燥的冬季

3.32 命名CMOS逻辑门延迟的两个分量,哪个受负载电容的影响更大?

解析:转换时间和传播延迟。转换时间受负载电容影响更大。

影响转换时间的因素:(1)晶体管的导通电阻 (2)负载电容[负载电容是指晶振的两条引线连接IC块内部及外部所有有效电容之和,可看作晶振片在电路中串接电容。]

只驱动CMOS输入时,直流负载可忽略。

交流负载决定了输出状态转换时的电压和电流,以及从一个状态转换到另一个状态所需的时间。

3.36 74VHC CMOS器件可在2.5V电源下工作,与工作于5.0V电源的情况相比,这样可以节约多少功耗?

解析:这是一个计算题,知道如何计算功耗即可。

关于功耗:静态状态下CMOS器件的功耗很低。

动态功耗:(1)CMOS输出结构的部分短路,输入电压不接近于供电轨道时,PMOS和NMOS部分导通;功耗取决于VCC的值和输出状态的转换发生率。

PT=C(PD)×VCC^2×f C(PD):功耗电容 f:输出信号转换的频率

(2)对负载电容CL充放电导致的功耗PL=CL×VCC^2×f CL:负载电容 f:输出信号转换的频率

综上:动态功耗:PD=PT+PL=CPD×VCC^2×f+CL×VCC^2×f=(CPD+CL) × VCC^2×f

本题解答:

PD=PT+PL=(CPD+CL)*VCC^2*f,动态功耗变为 5V 情况下的 1/4

3.37 一个施密特触发反相器,Vilmax=0.8V Vihmin=3.0V Vt+=1.7V Vt-=1.2V,那么它滞后多少?

解析:计算题,要知道如何计算滞后。

Vt+表示正向输入变化的阈值电压 Vt-表示负向输入变化的阈值电压

滞后就是两者的差值

本题解答:t=Vt+-Vt-=1.7V-1.2V=0.5V

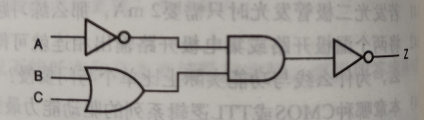

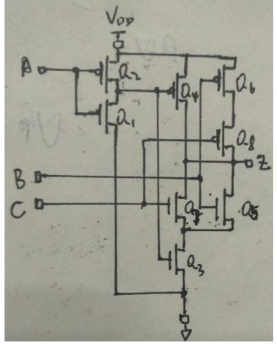

3.60 设计一个功能如图的CMOS电路(提示:只需要8个晶体管)

解析:先设计一个非门(两个电子管),然后设计一个或门(六个电子管),最后设计与非门(四个电子管)...这是一个比较麻烦的做法.

助教的完美做法:先考虑设计出“非”门。然后,考虑要求“非”门输出高电位时 B C 均为低电位才能获取高电位;“非”门输出低电位时 B C 任意输入均可得到高电位。根据两条路线设计剩余部分。

3.68 分析图 3-37 中 CMOS 反相器输出下降时间,Rl=900Ω Vl=2.0V。将结果与 3.6.1 节结果比较并解释之

解析:根据三要素分析法

初态:Vh=49/11V 终态:Vl=0.2V 转换后等效电阻 90Ω 时间常数 RC=9ns

输出电压随时间变化关系:Vout=Vl+(Vh-Vl)e^(-t/RC)

将 3.5V 和 1.5V 分别带入求解,得到下降时间 t=ln((3.5-0.2)/(1.5-0.2))*9ns≈8.4ns

与 3.6.1 得到结果相近。因为影响结果的只有 Vl,而 Vl 很小。

(这道题我看了半天都不知道Vh从何而来,如何计算等效电阻?RC要怎么计算?)

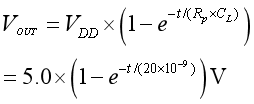

[补充一些相关知识:(1)关于CMOS器件的输出下降时间和上升时间的计算。

首先,要明白电容两端的电压不能瞬间改变。因此,即使电路输入的高低电平瞬间改变,对应的等效电阻也瞬间改变,但是电容两边的电压是要有一定延迟的。而这个变化时间是可以计算出来的。具体公式为 ,此为下降时间。

,此为下降时间。

,此为上升时间。两处所取的RC均为10nm]

,此为上升时间。两处所取的RC均为10nm]

3.79 考虑一个 CMOS8位二进制计数器,时钟频率 16MHz。为计算计数器动态功耗,最低有效位转换频率多少?最高有效位转换频率多少?为计算 8 个输出位动态功耗,应采用什么频率?

解析:时钟频率时指每个单位时间内产生的脉冲的数量,最低位共有两种形态0和1,因此转换频率为时钟频率/2。每上升一位,转换频率便除以2,因此最高位为最低位/2^7。为计算8个输出位的动态功耗,应该取所有位上的频率的平均值。

标准解答:最低有效位转换频率:16MHz/2=8MHz

最高有效位转换频率:8MHz/2^7=8MHz/128=0.0625MHz

应采用频率:求平均值,8MHz*(2-1/2^7)/8≈1.99MHz